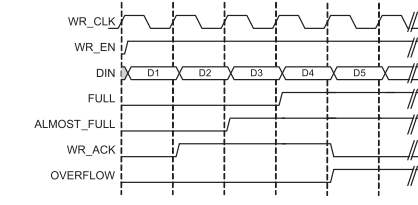

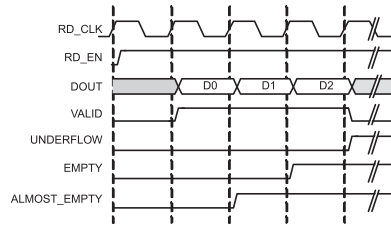

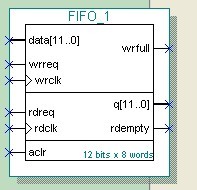

问一个问题哦:假设我的FIFO深度是8,在我写进第七个数据就会产生full信号吗 还是写进第八个产生full? 这个full=1的时候,我去读是读一个数据就full为0还是读到第几个数据时候full为0啊?

读的时候读到第七个就会产生empty信号吗 还是第八个产生empty信号呢,在读空的情况下既empty=1,去写数据,是写进去一个数据empty就为0还是写进去第几个数据empty就为0? 求高手解答啊 多谢啊

共4条

1/1 1 跳转至页

转一个

FIFO使用技巧

FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。我总结一下我在使用FIFO过程中的一些心得,与大家分享。

我本人是做有线通信的,所做的设计中大量的使用到FIFO,用于报文的缓存。我经常使用一个FIFO存报文内容,另一个FIFO存报文的长度,两者配合使用。

在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO的Empty和Almost_empty以及读使能配合起来使用,来保证能够连续读,并准确的判断FIFO空满状态,提前决定是否能启动读使能。具体的实施办法是:当Empty为1,立即停止读;当Empty为0,Almost_empty为0时,可以放心读;当Empty为0,但是Almost_empty为1时,如果上一拍读使能Read也为1,那么不能读;当Empty为0,但是Almost_empty为1时,如果上一拍读使能Read为0,可以读最后一拍。

在FIFO使用时,使用到Almost_full信号以及读写counter来控制FIFO的读满预警,如果数据不是在空满判断的下一拍写入FIFO,则设计FIFO的满预警时要小心。如果你不确定判断满预警之后要延迟多少拍才能真正写入FIFO,那么尽量让FIFO有足够满预警裕量。例如,在wr_data_count为128才是真的满了,你可以设成wr_data_count为120的时候就给出满预警,可以保证设计的可靠和安全。当然,如果你能准确的算出判断满预警与真正写入FIFO的延迟,可以用精确的满预警阈值。

当需要使用到数据位宽转换时,如将128位的数据转换成64位的数据,最好不要用XILINX自己生成的位宽转换FIFO。可以例化两个64位的FIFO,自己控制128转64。这样可以大大的节省资源,是XILINX CORE生成的FIFO资源的一半。

FIFO是在FPGA设计中使用的非常频繁,也是影响FPGA设计代码稳定性以及效率等得关键因素。我总结一下我在使用FIFO过程中的一些心得,与大家分享。

我本人是做有线通信的,所做的设计中大量的使用到FIFO,用于报文的缓存。我经常使用一个FIFO存报文内容,另一个FIFO存报文的长度,两者配合使用。

在数据连续读取时,为了能不间断的读出数据而又不导致FIFO为空后还错误的读出数据。可以将FIFO的Empty和Almost_empty以及读使能配合起来使用,来保证能够连续读,并准确的判断FIFO空满状态,提前决定是否能启动读使能。具体的实施办法是:当Empty为1,立即停止读;当Empty为0,Almost_empty为0时,可以放心读;当Empty为0,但是Almost_empty为1时,如果上一拍读使能Read也为1,那么不能读;当Empty为0,但是Almost_empty为1时,如果上一拍读使能Read为0,可以读最后一拍。

在FIFO使用时,使用到Almost_full信号以及读写counter来控制FIFO的读满预警,如果数据不是在空满判断的下一拍写入FIFO,则设计FIFO的满预警时要小心。如果你不确定判断满预警之后要延迟多少拍才能真正写入FIFO,那么尽量让FIFO有足够满预警裕量。例如,在wr_data_count为128才是真的满了,你可以设成wr_data_count为120的时候就给出满预警,可以保证设计的可靠和安全。当然,如果你能准确的算出判断满预警与真正写入FIFO的延迟,可以用精确的满预警阈值。

当需要使用到数据位宽转换时,如将128位的数据转换成64位的数据,最好不要用XILINX自己生成的位宽转换FIFO。可以例化两个64位的FIFO,自己控制128转64。这样可以大大的节省资源,是XILINX CORE生成的FIFO资源的一半。

共4条

1/1 1 跳转至页

回复

| 有奖活动 | |

|---|---|

| 【有奖活动】智能可穿戴设备AR/VR如何引领科技新潮流! | |

| 奖!发布技术笔记,技术评测贴换取您心仪的礼品 | |

| 【有奖活动】震撼来袭!这场直播将直击工程师的心灵! | |

| “我想要一部加热台”活动,不花钱赢取开发好工具!活动开始了哦 | |

| 【有奖活动】伙伴们:您的“需求”解决了吗? | |

| 打赏帖 | |

|---|---|

| 【换取手持数字示波器】N32G430点亮数码管与串口打印、ADC被打赏40分 | |

| 老胖子聊电路--分析一个反馈电路被打赏50分 | |

| 【换取手持数字示波器】+点亮WS2812RGB灯被打赏50分 | |

| 【换取手持数字示波器】+线性调整器理论知识分享被打赏40分 | |

| 放大↔震荡被打赏50分 | |

| 【换取手持数字示波器】RTduino驱动ssd1306+sht31温湿度计被打赏40分 | |

| 【换取手持数字示波器】称植国产开源TobudOS到雅特力AT32F425被打赏40分 | |

| 【分享评测,赢取加热台】+Telink-泰凌微电子B91点灯篇被打赏20分 | |

| 【换取手持数字示波器】+精英板驱动LCD屏被打赏50分 | |

| 【换取手持数字示波器】+DFR0216全彩灯带WS2812示例分享被打赏50分 | |

的

的