JLINK_V9 测试流程

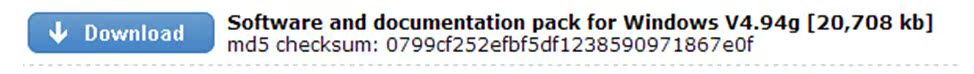

1. 下载最新的JLINK驱动:https://www.segger.com/jlink-software.html

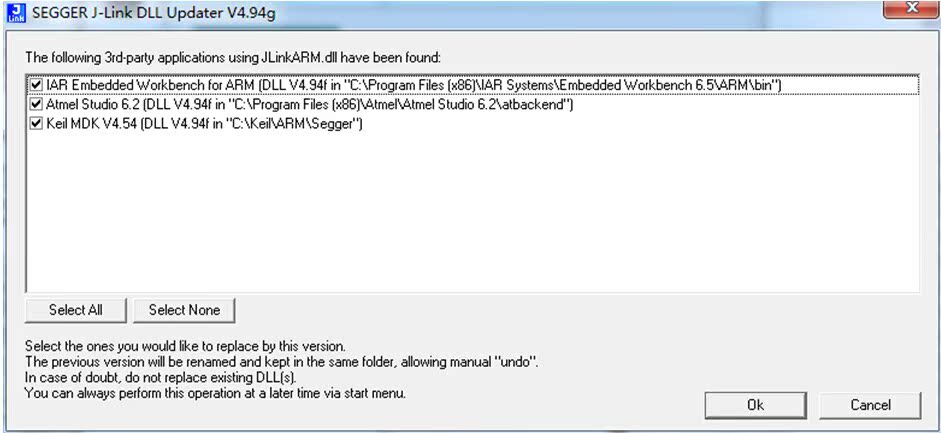

2 安装驱动;

WIN7系统最好用管理员身份安装,否则可能会有意外的问题。

该选择是替换系统已经安装软件的驱动,最好全选,覆盖掉老驱动。因为V9是比较新的,有测试过V4.54的驱动调试时会停掉或者异常,换最新的驱动就很正常了。

3. 测试V9

(1) 连接好V9和目标板;

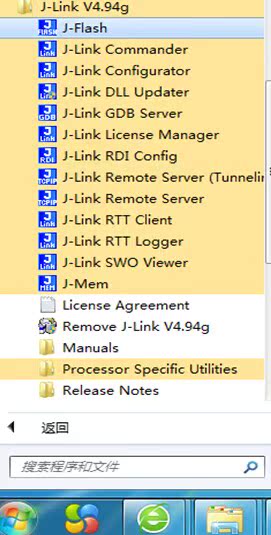

(2) 打开SEGGER J-Flash (SEGGER安装目录找)

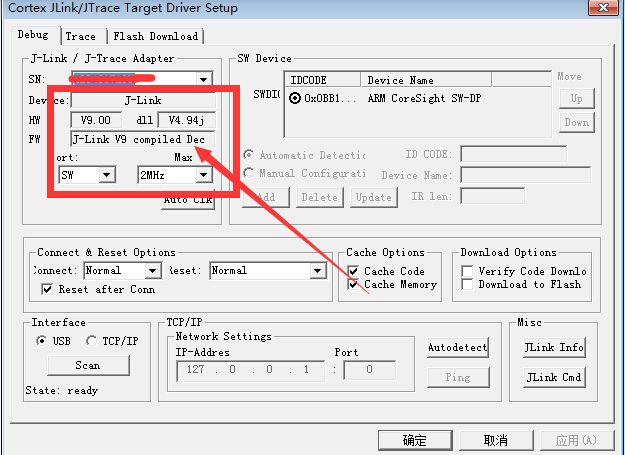

(3) 设置J-Flash

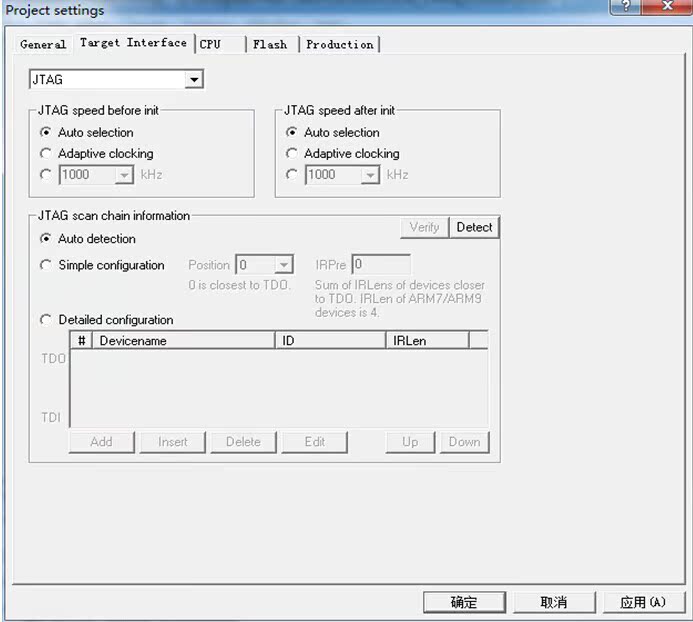

OptionsàProject Settings

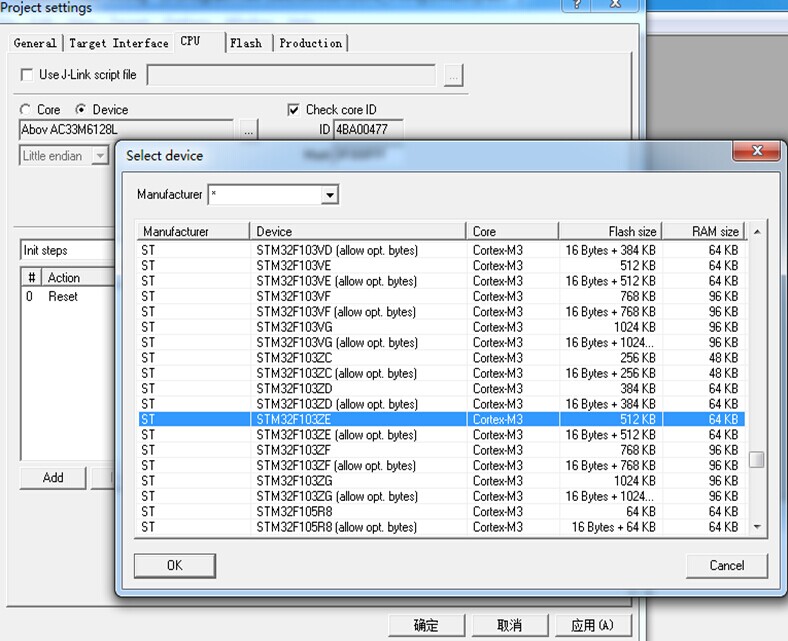

Device 我们默认选择STM32F103ZE(选择自己要下载的目标板型号), 点击“OK”

然后点击“应用”,“确定”,其他的都为默认设置。

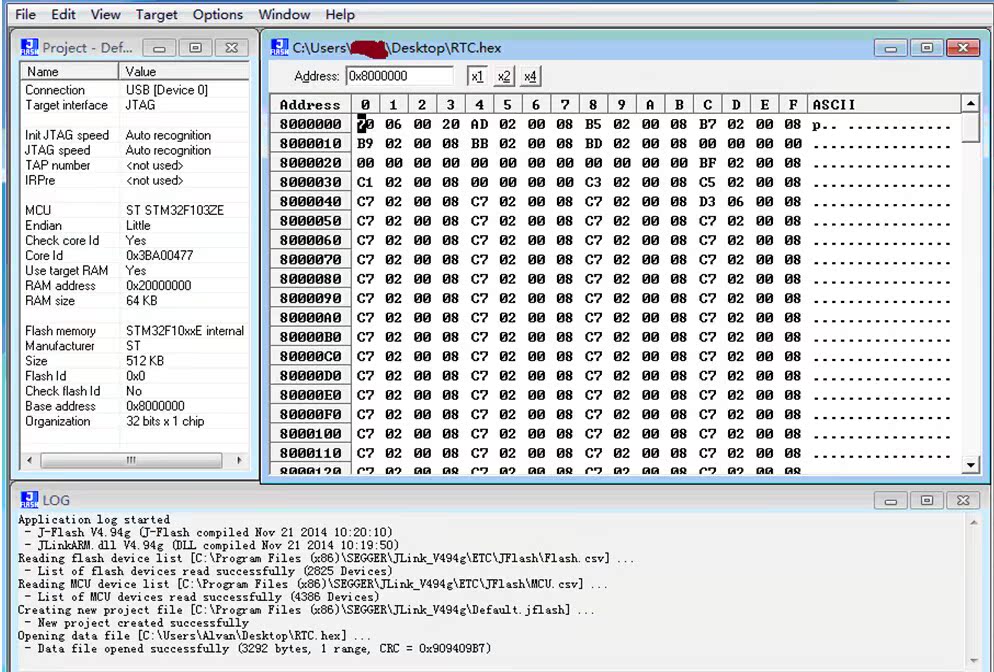

点击“File”-> “Open data file”,RTC.hex为我们的测试代码;

注:如果要下载自己的BIN文件,如果是STM32下来,打开文件时会提示地址选择,一定要输入“8000000”。

(4)下载测试

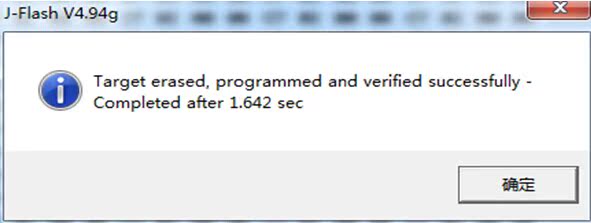

点击“Target”-> “auto”或者“F7”下载。

如果下载成功:

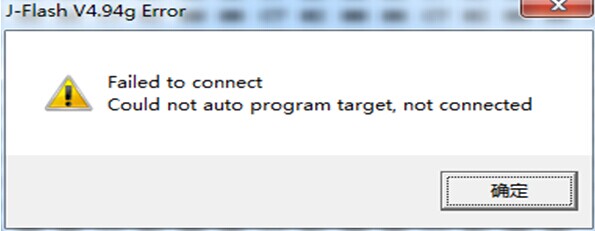

下载失败:

下载失败的原因:

<1> JTAG线是否连接正常

<2> 目标板是否供电

<3> 接口是否连接正常

JTAG:

1,2-------------3.3V

5------------------TDI

7------------------TMS

9------------------TCK

13-----------------TDO

15-----------------RESET(有些芯片不接正常)

2,4,6,8,10,12,14,16,18,20任一个接地

SWD:

1,2-------------3.3V

7------------------SWDIO

9------------------SWCLK

15-----------------RESET(有些芯片不接正常)

2,4,6,8,10,12,14,16,18,20任一个接地

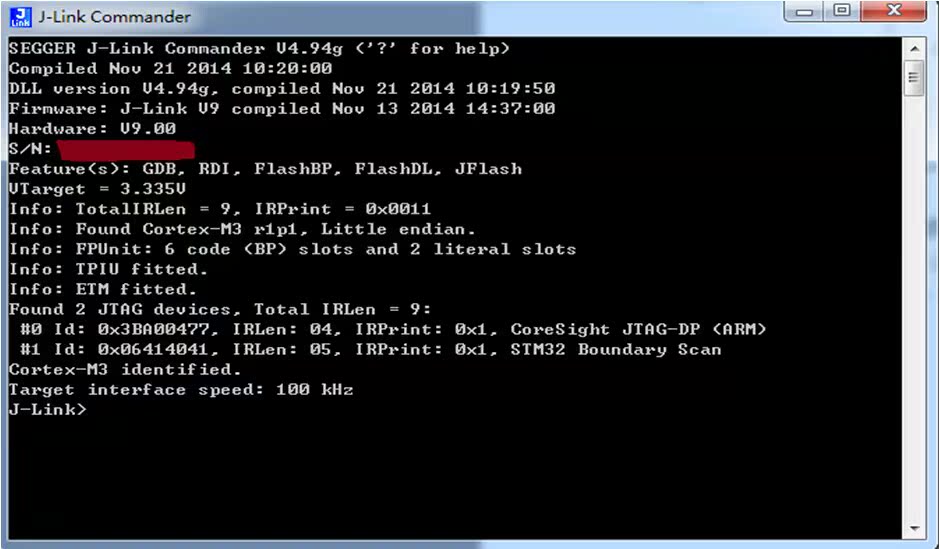

目标板测试:

连接好目标板,打开“J-Link Commander”如果目标板连接正常,会有如下显示:

J-LINK V9.3 仿真器 概述:

1,主控芯片采用STM32F205,不掉固件;

2,原装固件,支持自动升级;

3,沉金工艺,媲美原装;

4,原装富士康的USB座;

5,正凌连接器DC3简牛足3U金;

6,正凌FC压线头国标灰排线;

7,自动升级

8, 手动降级命令:EXEC invalidatefw

JTAG / SWD仿真器采用USB接口

J-Link是USB供电的JTAG仿真器支持大量CPU内核。

基于32位RISC CPU,它可以在高速与支持的目标处理器通信。 J-Link用于世界各地的数万地方进行开发和生产(闪存编程)的目的。

的J-Link是由所有主要的IDE,如IAR EWARM,Keil公司MDK,罗利CrossWorks的,Atollic TrueSTUDIO,IAR EWRX,瑞萨HEW,瑞萨e2studio,和其他许多人的支持。

包括所有车型,超过10万的J-链接已售出到目前为止,使得歼链接可能是最流行的仿真器ARM内核和事实上的标准。

产品特点

支持直接下载到闪存memoryof最流行的微控制器

支持的CPU:任何ARM7/ 9/11的Cortex-A5/ A8/ A9高速公路的Cortex-M0/ M1/ M3 / M4,的Cortex-R4,RX100/ RX200/ RX610/ RX621/ RX62N/ RX62T/ RX630/ RX631/ RX63N

下载速度高达1兆字节/秒

Supportsunlimited breakpointsin闪存!1MORE信息...

设置断点的Cortex-M系统的inexternalflash内存是可能的

J-Link'sUnlimited闪存Breakpointstechnology而已!

所有主要IDEsMore信息支持的...

免费软件updates2,1年的支持

支持并发访问CPU通过多个申请3

跨平台支持(运行在Windows,Linux,Mac OS X中)4

情报模拟器firmwareMore信息...

远程服务器包括在内。通过TCP/ IPMore资讯允许使用的J-连接远程...

GDBSERVER includedMore信息...

生产闪存编程软件(J-闪光灯)availableMore信息...

软件开发工具包(SDK)availableMore信息...

支持多种目标接口:JTAG,SWD

支持SWV/社会工作主任(串行线查看器/串行线输出)

目标电压范围广:1.2V - 3.3V,5V宽容

支持JTAG链上连接多个设备

嵌入式跟踪缓冲区(ETB)的支持

可用各种目标适配器,包括光电隔离adapter.More信息...

RDI接口DLL available.More信息...

完全即插即用兼容

无需电源,通过USB供电

支持自适应时钟

所有JTAG信号可以被监视,目标电压可以测量

目标电源:的J-Link可提供高达300 mA的目标具有过载保护

| Supported OS |

Microsoft Windows 2000 Microsoft Windows XP Microsoft Windows XP x64 Microsoft Windows 2003 Microsoft Windows 2003 x64 Microsoft Windows Vista Microsoft Windows Vista x64 Windows 7 Windows 7 x64 Windows 8 Windows 8 x64 Linux Mac OSX 10.5 and higher |

| Electromagnetic compatibility (EMC) | EN 55022, EN 55024 |

| Operating temperature | +5°C ... +60°C |

| Storage temperature | -20°C ... +65 °C |

| Relative humidity (non-condensing) | Max. 90% rH |

| Size (without cables) | 100mm x 53mm x 27mm |

| Weight (without cables) | 70g |

| USB interface | USB 2.0 |

| Target interface | JTAG 20-pin (14-pin adapter available) |

| Power supply |

USB powered Max. 50mA + Target Supply current. |

| Target interface voltage (VIF) | 1.2V ... 5V |

| Target supply voltage | 4.5V ... 5V (if powered with 5V on USB) |

| Target supply current | Max. 300mA |

| Reset Type |

Open drain. Can be pulled low or tristated. |

| Reset low level output voltage (VOL) | VOL <= 10% of VIF |

| For the whole target voltage range (1.2V <= VIF <= 5V) | |

| LOW level input voltage (VIL) | VIL <= 40% of VIF |

| HIGH level input voltage (VIH) | VIH >= 60% of VIF |

| For 1.2V <= VIF <= 3.6V | |

| LOW level output voltage (VOL) with a load of 10 kOhm | VOL <= 10% of VIF |

| HIGH level output voltage (VOH) with a load of 10 kOhm | VOH >= 90% of VIF |

| For 3.6 <= VIF <= 5V | |

| LOW level output voltage (VOL) with a load of 10 kOhm | VOL <= 20% of VIF |

| HIGH level output voltage (VOH) with a load of 10 kOhm | VOH >= 80% of VIF |

| JTAG speed | Max. 15MHz |

| SWO sampling frequency | Max. 7.5MHz |

| Data input rise time (Trdi) | Trdi <= 20ns |

| Data input fall time (Tfdi) | Tfdi <= 20ns |

| Data output rise time (Trdo) | Trdo <= 10ns |

| Data output fall time (Tfdo) | Tfdo <= 10ns |

| Clock rise time (Trc) | Trc <= 3ns |

| Clock fall time (Tfc) | Tfc <= 3ns |

* J-Link hardware revision 8 and up