说明,本文选自CSDN博客,原作者:ce123

如何学习总线技术

以形象生动的比喻来描绘了总线技术的基本思想,指出了总线的基本分类和总线传输的基本原理,以及在学习过程中应当掌握的最基本的知识,对初学者有起到抛砖引入的作用。

如果一座只能容一个人来往的独木桥,两端的人都想要过桥,为了不拥挤、阻塞,那我们就得采取有效的办法。比如规定某段时间哪端的人过桥,另一端的人就等着该他过桥的时间段的到来,同时也还可以规定人多时要按先来后到或年龄长幼的次序过桥。在这不经意间,我们就体会到了现代电子信息数据通过总线按时分系统传输的最原始的思想。

现代网络信息的发展,特别是对于成本和空间而言,总线传输替代点对点传输是目前发展的热点,它的出现将给信息传输上提供了最大的方便和最有效的技术解决方案。假如一个微处理器与它的部件和外围设备都分别用点对点的线路来连接通讯,则所有连线将会错综复杂,甚至难以实现。

目前与我们生活习习相关的一系列活动都无不牵涉到总线技术的应用,如我们上英特网、给亲戚朋友打电话、用U盘来存储信息等。虽然流行的总线所采取的形式不同,但他们主要的原则性思想无非就是时分系统、频分系统、相分系统和码分系统等。常言道“兵来将挡,水来土淹”,面对种类繁多的总线,我们只有从基本原理出发,从骨子里去了解它的实质,而不要被它形式多样的外表所迷惑,才能熟练掌握和灵活运用眼下正在或将要用到的各种总线技术。

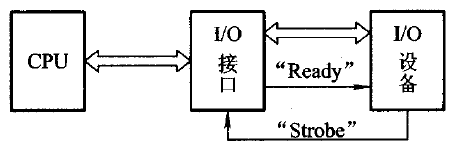

总线,英文叫作“BUS”,即我们中文的“公共车”,这是非常形象的比如,公共车走的路线是一定的,我们任何人都可以坐公共车去该条公共车路线的任意一个站点。如果把我们人比作是电子信号,这就是为什么英文叫它为“BUS”而不是“CAR”的真正用意。当然,从专业上来说,总线是一种描述电子信号传输线路的结构形式,是一类信号线的集合,是子系统间传输信息的公共通道。通过总线能使整个系统内各部件之间的信息进行传输、交换、共享和逻辑控制等功能。如在计算机系统中,它是CPU、内存、输入、输出设备传递信息的公用通道,主机的各个部件通过主机相连接,外部设备通过相应的接口电路再于总线相连接。

总线分类的方式有很多,如被分为外部和内部总线、系统总线和非系统总线等等,下面是几种最常用的分类方法。

最常见的是从功能上来对数据总线进行划分,可以分为地址总线(address bus)、数据总线(data bus)和控制总线(control bus)。在有的系统中,数据总线和地址总线可以在地址锁存器控制下被共享,也即复用。

地址总线是专门用来传送地址的。在设计过程中,见得最多的应该是从CPU地址总线来选用外部存储器的存储地址。地址总线的位数往往决定了存储器存储空间的大小,比如地址总线为16位,则其最大可存储空间为216(64KB)。

数据总线是用于传送数据信息,它又有单向传输和双向传输数据总线之分,双向传输数据总线通常采用双向三态形式的总线。数据总线的位数通常与微处理的字长相一致。例如Intel 8086微处理器字长16位,其数据总线宽度也是16位。在实际工作中,数据总线上传送的并不一定是完全意义上的数据。

控制总线是用于传送控制信号和时序信号。如有时微处理器对外部存储器进行操作时要先通过控制总线发出读/写信号、片选信号和读入中断响应信号等。控制总线一般是双向的,其传送方向由具体控制信号而定,其位数也要根据系统的实际控制需要而定。

按照数据传输的方式划分,总线可以被分为串行总线和并行总线。从原理来看,并行传输方式其实优于串行传输方式,但其成本上会有所增加。通俗地讲,并行传输的通路犹如一条多车道公路,而串行传输则是只允许一辆汽车通过单线公路。目前常见的串行总线有SPI、I2C、USB、IEEE1394、RS232、CAN等;而并行总线相对来说种类要少,常见的如IEEE1284、ISA、PCI等。

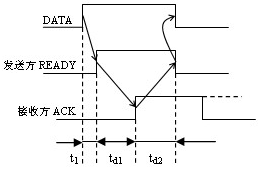

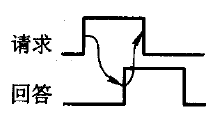

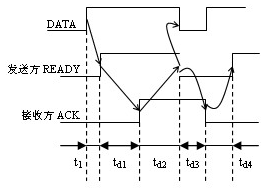

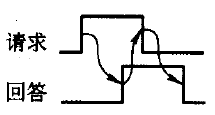

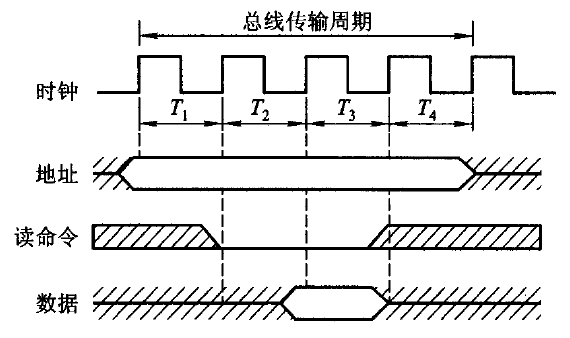

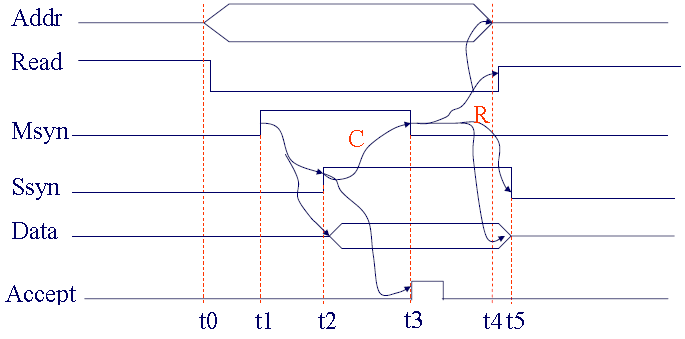

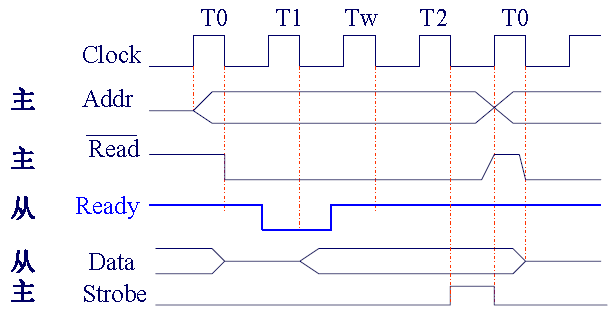

按照时钟信号是否独立,可以分为同步总线和异步总线。同步总线的时钟信号独立于数据,也就是说要用一根单独的线来作为时钟信号线;而异步总线的时钟信号是从数据中提取出来的,通常利用数据信号的边沿来作为时钟同步信号。

依据前面对总线的定义可知总线的基本作用就是用来传输信号,为了各子系统的信息能有效及时的被传送,为了不至于彼此间的信号相互干扰和避免物理空间上过于拥挤,其最好的办法就是采用多路复用技术,也就是说总线传输的基本原理就是多路复用技术。所谓多路复用就是指多个用户共享公用信道的一种机制,目前最常见的主要有时分多路复用、频分多路复用和码分多路复用等。

时分复用是将信道按时间加以分割成多个时间段,不同来源的信号会要求在不同的时间段内得到响应,彼此信号的传输时间在时间坐标轴上是不会重叠。

频分复用就是把信道的可用频带划分成若干互不交叠的频段,每路信号经过频率调制后的频谱占用其中的一个频段,以此来实现多路不同频率的信号在同一信道中传输。而当接收端接收到信号后将采用适当的带通滤波器和频率解调器等来恢复原来的信号。

码分多路复用是所被传输的信号都会有各自特定的标识码或地址码,接收端将会根据不同的标识码或地址码来区分公共信道上的传输信息,只有标识码或地址码完全一致的情况下传输信息才会被接收。

对于总线的学习,了解其通讯协议是整个过程中最关键的一步,所有介绍总线技术的资料都会花很大的篇幅来描述其协议,特别是ISO/OSI的那七层定义。其实要了解一种总线的协议,最主要的就是去了解总线的帧数据每一位所代表的特性和意义,总线各节点间有效数据的收发都是通过各节点对帧数据位或段的判断和确信来得以实现。

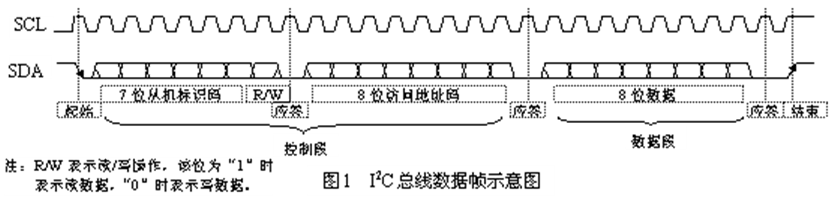

如图1所示是常见的I2C总线上传输的一字节数据的数据帧,其总线形式是由数据线SDA和时钟SCL构成的双线制串行总线,并接在总线上的电路模块即可作为发送器(主机)又可作为接收器(从机)。帧数据中除了控制码(包括从机标识码和访问地址码)与数据码外还包括起始信号、结束信号和应答信号。

起始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

控制码:用来选泽操作目标与对象,即接通需要控制的电路,确定控制的种类对象。在读期间,也即SCL时钟线处于时钟脉冲高电平时,SDA上的数据位不会跳变。

数据码:是主机向从机发送的具体的有用的数据(如对比度、亮度等)和信息。在读期间,SDA上的数据位不会跳变。

应答信号:接收方收到8bit数据后,向发送方发出特定的低电平。读/写的方向与其它数据位正好相反,也即是由从机写出该低电平,主机来读取该低电平。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变表示数据帧传输结束。

当然不同的总线其数据位或段的定义肯定不同,但依据同样的原理可以更快的去了解它的协议的特性和特点。虽然其信息帧的大小不一,但具体的某一数据位或数据段都类似于本文所提及的I2C总线,会依据它的协议的要求来定义它所达标的意义和功能。

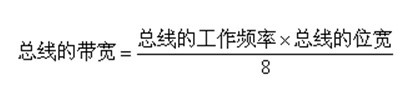

评价总线的主要技术指标是总线的带宽(即传输速率)、数据位的宽度(位宽)、工作频率和传输数据的可靠性、稳定性等。

总线的带宽指的是单位时间内总线上传送的数据量,即每钞传送MB的最大数据传输率。总线的位宽指的是总线能同时传送的二进制数据的位数,或数据总线的位数,即32位、64位等总线宽度的概念;总线的位宽越宽,数据传输速率越大,总线的带宽就越宽。总线的工作时钟频率以MHz为单位,它与传输的介质、信号的幅度大小和传输距离有关。在同样硬件条件下,我们采用差分信号传输时的频率常常会比单边信号高得多,这是因为差分信号的的幅度只有单边信号的一半而已。

总线的带宽、位宽和工作频率,这三者密切相关,它们之间的关系:

可靠性是评定总线最关键的参数,没有可靠性,传输的数据都是错误的信息,便就失去了总线的实际意义。为了提高总线的可靠性,通常采用的措施有:

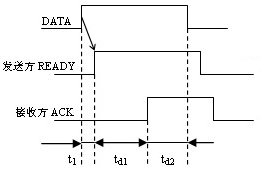

采用数据帧发送前发送器对总线进行侦听,只有侦听到总线处于空闲状态下时才可向总线传送数据帧,这样避免了不同节点的数据冲突。

采用双绞线差分信号来传送数据,以降低单线的电压升降幅度,减小信号的边沿产生的高次谐波。

适当的让数据的边沿具有一定的斜坡。

增加匹配电阻和电容等来减少总线上信号的发射和平衡总线上的分布电容等。

采用合适的网络拓扑结构和屏蔽技术等来减少受其他信号的干扰。

还有就是在软件上通过数字滤波、数据校验纠错等措施来提高数据传输的可靠性。

学习是一个循序渐进的过程,对总线技术的学习和理解也是随着其技术的不断发展而不断更新的过程。子曰“工欲善其事,必先利其器。”只有从最基本的原理出发,打好基础,才能在今后的学习中融会贯通,前仆后继,更进一步深入该知识点和拓宽知识面。