需求描述:XB_HIGH_IN输入下降沿时,H_Trig_OUT立即输出一个负脉冲

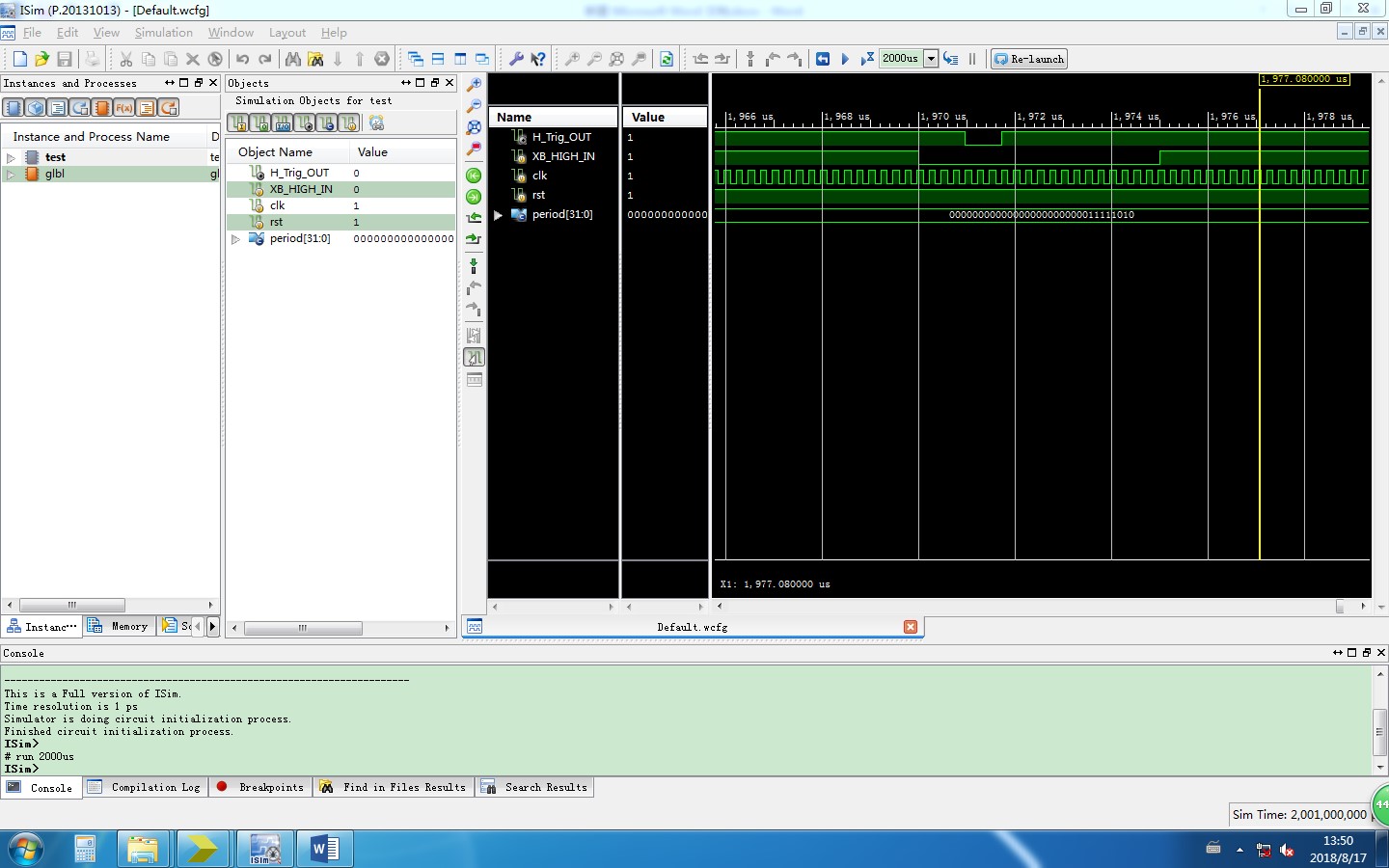

仿真结果:H_Trig_OUT输出的波形有4个clk的延时,求大神指教是什么导致了这4个clk的延迟

程序代码:

module TESTCODE(

input XB_HIGH_IN,

input clk,

input rst,

output reg H_Trig_OUT

);

parameter T100us = 12'd3;

reg H_fir,H_sec;

reg H_change_trig;

reg H_vld;

reg [11:0]H_count;

always@(posedge clk or negedge rst)

if(!rst)

begin

H_fir<=1'b1;

H_sec<=1'b1;

H_change_trig<=1'b0;

end

else

begin

H_fir<=XB_HIGH_IN;

H_sec<=H_fir;

H_change_trig<=~H_fir&H_sec;//下降沿

End

//输出负脉冲

always @(posedge clk or negedge rst)

if(!rst)

begin

H_count<=12'd0;

H_vld<=1'b0;

H_Trig_OUT<=1'b1;

end

else

begin

if(H_change_trig==1'b1)H_vld<=1'b1;

if(H_vld==1'b1)

begin

H_count<=H_count+1'b1;

H_Trig_OUT<=1'b0;

if(H_count==T100us)

begin

H_count<=12'd0;

H_vld<=1'b0;

H_Trig_OUT<=1'b1;

end

end

end

endmodule

测试代码:

module test;

// Inputs

reg XB_HIGH_IN;

reg clk;

reg rst;

// Outputs

wire H_Trig_OUT;

// Instantiate the Unit Under Test (UUT)

TESTCODE uut (

.XB_HIGH_IN(XB_HIGH_IN),

.clk(clk),

.rst(rst),

.H_Trig_OUT(H_Trig_OUT)

);

parameter period =250;///////40MHZ

initial begin

// Initialize Inputs

XB_HIGH_IN = 1;

clk = 0;

rst = 0;

// Wait 100 ns for global reset to finish

#100;

rst = 1;

// Add stimulus here

forever begin

#(period/2);

clk=~clk;

end

end

initial begin

forever begin

#(period*20);

XB_HIGH_IN<=1'b1;

#(period*20);

XB_HIGH_IN<=1'b0;

end

end

endmodule

仿真波形图: