作者:姜杰(一博科技自媒体高速先生团队成员)

残阳收尽最后一抹余晖,暮色四合,与天色一起暗淡下来的还有雷工的心情:因为自己信心满满设计的时钟端接不仅没有改善信号质量,反而拖了后腿。事情还要从高速先生最新的一期短视频说起。

话说,高速先生队长果然魅力非凡,一个浅显易懂的比喻就把端接的基本原理讲解的清清楚楚(信号为什么会反射?要怎样做好端接匹配之PCB设计十大误区视频链接)。

端接匹配的话题引起了雷工的兴趣,看完视频意犹未尽,自己还抽空把几种常见的端接重新都学习了一遍。机会是留给有准备的人,雷工在隔天的Layout设计中就遇到了表现的机会。

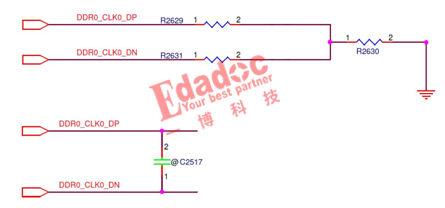

数据速率为2400Mbps的DDR3信号,地址及时钟走线拓扑为一拖四、fly-by。在处理差分时钟的时候,雷工在原理图上看到的除了端接电阻,还有一个并联在差分信号P/N中间的电容。

如果这个电容早两天出现,雷工估计还要纠结放在链路的哪个位置,可是,对于认真学过端接的他而言,这已经不再是问题,有端接电阻R,又出现电容C,可不就是终端RC端接嘛!明明需要放在一起,硬件攻城狮还要分开画图,简直多此一举,雷工毫不犹豫的把这个电容放在差分时钟的末端。走线完成之后发给高速先生仿真,雷工洋洋自得,坐等PASS。

高速先生带来了一好一坏两个消息,好消息是雷工设计的时钟“端接”起了作用,雷工的笑容开始绽放;坏消息是,“端接”起了副作用,拖垮了时钟信号,雷工的笑容僵在了脸上。于是出现了文章开头那略显伤感的一幕。

高速先生没有让雷工独自凌乱,而是帮他仔细分析了问题。关键就在于雷工所谓的“端接电容”并非RC端接的一部分,其实,它的主要作用是通过减缓驱动信号的上升沿从而减小源端反射,应该靠近驱动芯片布局,通常用于驱动较强的芯片。所以,雷工需要做出的修改也很简单,就是把该电容由末端调整至驱动端。关于这个电容,高速先生称之为“差分电容”,之前也有专门的文章介绍过。(《DDR3系列之时钟信号的差分电容,一般人我不告诉他!》文章链接)

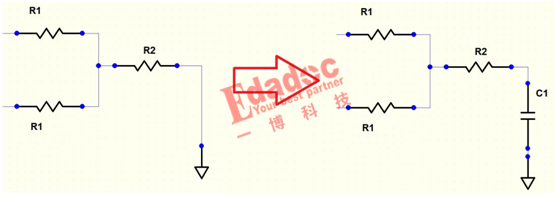

那么,雷工本来想用来炫技的RC端接正确的打开姿势又是怎样的呢?RC端接,又称AC端接,常用于传输直流平衡信号的链路。对于单端信号,RC端接方式是在传统的末端并联端接的基础上增加了一个电容,最大的优点就是直流功耗较小,同时也会避免传统并联端接高电平被拉低或者低电平被抬高的现象。

对于差分信号的RC端接,通常是在T型端接的基础上增加一个隔直流电容,有些设计也会把R2省掉。

无论是单端信号,还是差分信号,RC端接中的“C”都是为了切断直流通路,而雷工遇到的并联在差分时钟P/N中间的电容显然不在此列。一番解释之后,雷工豁然开朗,最终,按照仿真建议将差分电容从终端调整到驱动端,时钟波形随之改善,并满足了SPEC要求。问题解决后,雷工心头的阴霾一扫而空,反思这次教训,理论没吃透就贸然行事,结果闹了笑话,更觉自己的进阶之路任重而道远。