FPGA 供应商一直在故意推动 FPGA 架构中不断扩大的分歧。主要供应商要么倾向于使用具有高性能应用处理器的 SoC FPGA,要么提供不带处理器的低端 FPGA。服务器群和高性能计算等应用程序需要不断提高性能。为了解决这个问题,许多 SoC FPGA 都采用了非常适合这些应用的 ARM A 级应用处理器。许多其他应用程序的现实情况是,这些处理器超出了所需。A 级 SoC FPGA 通常过于昂贵,由于所需的操作系统而需要过多的软件支持负担,并且具有更高的功耗。此外,通常不需要原始计算性能。

另一方面,没有硬微控制器或处理器的低端 FPGA 可能会限制众多设计。低端 FPGA 仅提供软微控制器,没有附带的外围设备或子系统。如果需要外设,则必须使用 FPGA 门创建它们。带有软微控制器的低端 FPGA 运行速度非常慢,由于创建微控制器和子系统所需的 FPGA 门而效率低下,不提供安全性,并且是在专有架构上开发的。

对于广泛的应用,基于硬化微控制器的 SoC FPGA 通常是更有效的解决方案。每年都会生产大量 32 位微控制器架构,因为有许多应用程序可以使用它们。想象一下,如果有一个带有通用组件子系统的微控制器,并且它还包括一个可以实现硬件加速任务或其他逻辑功能的可配置块?ARM Cortex-M3 SoC FPGA 可以被视为具有可配置硬件加速的微控制器。硬件加速和逻辑功能的实现是 FPGA 架构擅长的两个关键特性。结合使用 ARM Cortex-M3 和 FPGA 架构,可以为各种应用中的许多任务实现理想的分工。

使用处理器和 FPGA 结构对设计示例进行分区

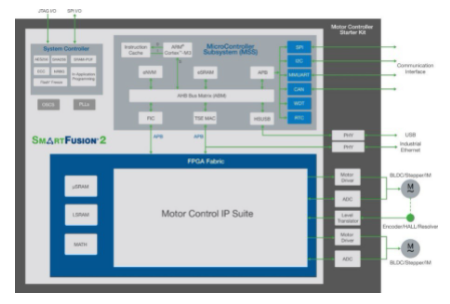

由于架构和访问存储器指令的要求,微控制器非常适合低速串行任务。FPGA 架构非常适合对时间要求更高的并行处理功能。当以这种方式划分设计时,每个组件应该实现哪些功能就变得很清楚了。例如,控制多个电机的主要挑战之一是需要电机控制回路的确定性响应。为确保设计可靠,每个电机都必须在严格的、确定的时间内进行维修,且时间不存在较大的变化。因为多轴电机控制算法是一个时间关键的功能,它应该驻留在 FPGA 架构中。FPGA 是实现具有严格确定性时序的控制回路的理想选择。图 1 是多轴电机控制设计的框图。大部分电机控制算法在 FPGA 架构中,而速度较慢的接口连接到 ARM Cortex-M3。

图 1:多轴电机控制设计框图。

为设计添加数据安全性

增加数据安全性需要证书和密钥交换,以及对数据实施加密和解密算法。有多个数据安全握手交换,并且通常需要对多种格式的支持。交换握手通常不是时间关键的,但每个交换算法都有不同的字符串需要解析、各种验证协议和多轮证书检查。由于所有这些程序和时间紧迫性的缺乏,在 Cortex-M3 等微控制器中实现证书和密钥交换是理想的。可以根据请求的握手交换调用和执行适当的代码。一旦交换了密钥并且两个设备都受信任,则需要对数据通信进行加密和解密。有许多有线和无线通信速度和协议,并且根据链路速度,数据加密和解密通常需要性能。当需要性能吞吐量时,建议在 FPGA 架构中实现。发送设备将实施诸如 AES 256、三重 DES、RSA 或类似的加密算法,而接收设备将实施相同的解密算法。如果数据链路性能不重要,Cortex-M3 可以实现加密和解密。然而,FPGA 架构非常适合需要更高吞吐量的情况。建议在 FPGA 架构中实现它。发送设备将实施诸如 AES 256、三重 DES、RSA 或类似的加密算法,而接收设备将实施相同的解密算法。如果数据链路性能不重要,Cortex-M3 可以实现加密和解密。然而,FPGA 架构非常适合需要更高吞吐量的情况。建议在 FPGA 架构中实现它。发送设备将实施诸如 AES 256、三重 DES、RSA 或类似的加密算法,而接收设备将实施相同的解密算法。如果数据链路性能不重要,Cortex-M3 可以实现加密和解密。然而,FPGA 架构非常适合需要更高吞吐量的情况。

向设计中添加自定义外围设备

尽管处理器和微控制器提供通用外设,但许多设计都需要定制接口。许多医疗、工业和嵌入式设计通常需要添加额外的接口,而开放式总线接口连接器解决了这个问题。两个比较流行的外围总线连接器是外围模块 (Pmod) 和 Arduino shield。有许多外设设计利用了这些连接器,而 SoC FPGA 非常适合在这些定制外设和设计的其余部分之间进行桥接。当需要额外的外围设备时,可以独特地利用基于微控制器的 SoC FPGA。微控制器和FPGA架构的结合可以实现桥接、加速功能、通信协议管理、I/O扩展和控制逻辑。一个示例是需要添加自定义显示的设计。与显示器接口需要接口控制逻辑、图像处理以及寄存器配置。ARM Cortex-M3 可以解决后者并执行其他管理任务,而 FPGA 最适合与显示器接口并根据需要修改图像。

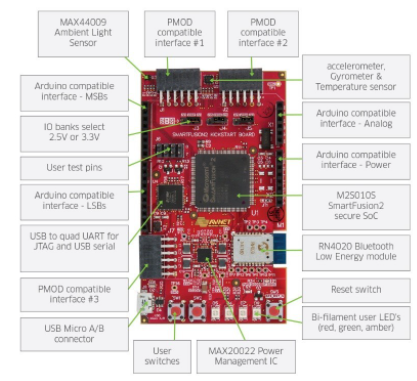

Avnet Electronics 最近创建了一个硬件套件,以展示基于微控制器的 SoC 可以为广阔市场带来的强大功能(图 2)。该板可以使用许多外围选项,因为它具有 Pmod 连接器和 Arduino 屏蔽连接器组。其他主要功能包括板载外围设备、低功耗蓝牙 (BLE)、USB 以及大量传感器和开关。该板采用 Microsemi SmartFusion2 SoC FPGA,其中包括硬核 ARM Cortex-M3 微控制器和综合子系统。该架构包含 HDL 和 C 代码参考设计、基于 Windows 的软件 GUI 和 Android 应用程序,以增加灵活性。Windows GUI 可以连接到所有板载组件,参考设计示例支持添加 Arduino 扩展板或 Pmod 外设。使用 Windows GUI 连接到 Android 手机时,可以看到完整的数据安全演示。这种数据安全设计实现了 SmartFusion2 FPGA 和 Android 智能手机之间的密钥交换和数据加密。

图 2: Avnet SmartFusion2 KickStart 套件。

有各种各样的通用应用程序理想地在基于微控制器的 SoC FPGA 中实现,可以解决桥接、I/O 扩展、硬件加速、协议管理和电路板初始化等解决方案。使用带有参考设计和软件 GUI 的硬件解决方案可以让设计理念迅速变为现实。