前言

首先要解释一下耦合,耦合就是互相影响,正如变压器的原边会影响副边,同时副边也会影响原边,这就让人想起金庸小说里的七伤拳,伤人伤己。

那么去耦,就是减少耦合,减少互相影响。其实这里的去耦电容跟滤波电容的意思是一样的,相关文章推荐:EMC防护中的滤波电容。但是为什么要另起一个名字呢?

笔者认为,如果耦合的反义词是滤波的话,往往会让人摸不着头脑,所以需要再起一个名词叫去耦,这样刚好满足人们语言表达的需求。

去耦电容的作用

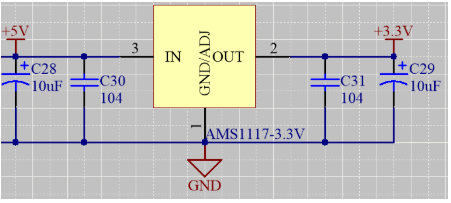

如上图所示,一个LDO的输入和输出各加了两个电容,分别是104和10uF。

显然电容是具有滤波的作用,但是这跟模电上的RC、LC、RLC滤波不一样,只有一个C,这样也能滤波的,滤波的频率叫自谐振频率。

上图中,NPO电容的自谐振频率呈V字形,而Z5V电容则呈U字形,说明了NPO电容的滤波特性更好,同时,也最容易滤掉虚线对应的频率,就是自谐振频率。

此外,电容工作在虚线左边的频率范围内,呈电容的特性,而虚线右边,则呈电感的特性,下面有解释。

为什么一个电容也会谐振?

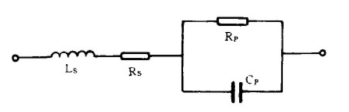

由电容的等效电路。

由于电容的制造工艺、材料等原因,实际的电容应该等效成上图所示,但是用在频率较低的电路上,Rs、Rp、Ls影响非常小,所以只把它当成一个Cp,而把其它的忽略掉。

如果电容工作在频率较高的电路上,就不能把Rs、Rp、Ls忽略了,这时利用上图的等效电路和拉氏变换,可以推导出电容的自谐振频率。而且,如果工作的频率超过电容的自谐振频率,那么感抗wLs会远大于容抗1/(wCp),这时,感抗起主导作用,容抗的影响非常小,可以忽略容抗时,电容会呈现感性。

这就让人想起了共振,如微波炉中的微波频率和水分子发生共振,说明了水分子也有自谐振频率。

谐振跟共振,其实是一个意思。

如何计算电容的自谐振频率?

在实际应用中,我们不可能对每个电容都测一下分布参数,弄等效电路的。一般是用经验公式:自谐振频率f0≈1/C。

怎样知道用多大的去耦电容?

可以用示波器测出LDO输入和输出的干扰信号的频率,再用公式C≈1/f0算出容值。一般要求没那么严格,直接加10uF和104,可以适用于一般的应用场合。

为什么要加一大一小两个电容?

由公式f0≈1/C可以得出,小电容滤高频干扰;大电容滤低频干扰。

为什么小电容要靠近芯片,而大电容则可以远一点?

小电容滤高频干扰,这个高频干扰不一定是由芯片外部输入进来的,也可以由芯片内部产生的。

像CPU、FPGA等,内部若干个MOS管像开关一样在导通、截止,这就形成了很多方波信号,再用傅立叶级数把它展开,就会产生很多奇次谐波。这些谐波的频率很高,属于高频干扰。如果高频干扰在整块电路板上传播,那就相当危险了,应该尽早的把它滤掉,所以要尽量靠近芯片。而低频干扰的影响力没那么大,可以远一点。

此外,大电容还充当了电池的作用,正如,关电视机的时候,电源指示灯要过一会才灭,就是因为这些大电容在给它放电。

去耦电容在多远的距离会失去滤波的作用?

这涉及到去耦半径的计算,有兴趣的读者,可以参考《信号完整性分析》。

为什么有些芯片的电源管脚上会放很多去耦电容?

怎样知道该用多少个电容?

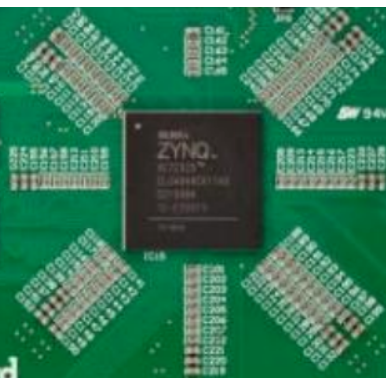

上图就是有名的zedboard上面,ZYNQ附近的去耦电容,像个八卦阵一样,非常优雅的设计。

但是这里却不像我们用单片机、或者LDO那样,加104和10uF那么简单。

上面也说到,CPU、FPGA,内部的MOS管不断地导通、截止,其实这就是动态负载,那么由欧姆定律,U=IR,可以得出,当R突然变小,U不变(先假设电压不变),I突然变得很大(想象一下,上亿个MOS管在同时工作,尽管一个MOS管吸取的电流非常小,但是量多了,总体吸取的电流是非常大的)。

再由功率守恒,P=UI,当P一定的时候(电源芯片提供的功率是不变的),I变大,U变小。这说明了,在电源芯片提供的功率范围内,电源电压是不变的;但是,超出了电源芯片的功率的话,电源电压是随着负载而变的,这也是正好解释了过载现象,只是这里是一个瞬间的过程。

所以才需要加很多去耦电容,去抑制电源电压的瞬间变化(也叫暂态)。加多少个电容,是由瞬态功率决定的。