作者:北华航天工业学院 杨坦 苏静静 赵志辉

指导教师:白旭 杨昭

作品简介

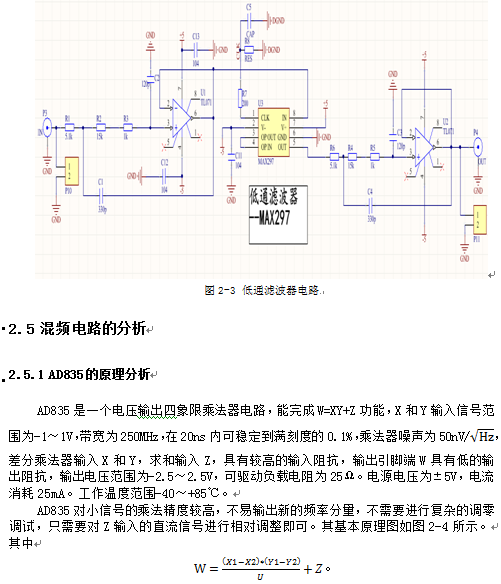

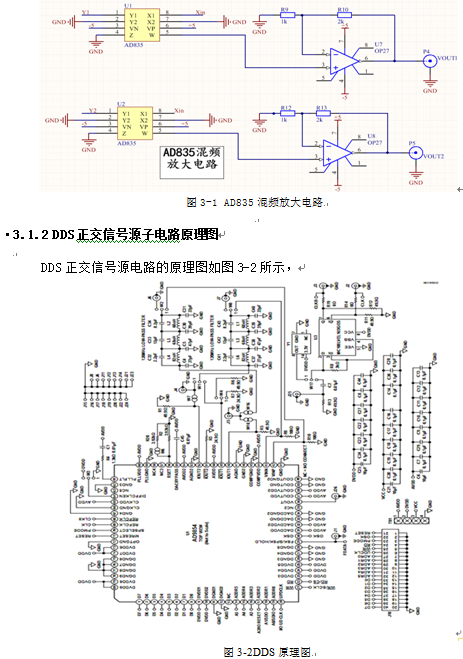

本系统采用零中频正交解调原理设计并实现频率特性测试仪。以控制器STM32F103ZET6作为控制核心,利用DDS专用芯片AD9854产生正交信号,模拟乘法器AD835做混频电路,π型网络做衰减网络,开关电容滤波器MAX297做低通滤波器,再通过OP27放大滤波器的输出信号送入STM32自带的ADC电路进行AD转换,最后用LCD液晶显示屏显示波形, LCD低通滤波器电路作为被测网络,实现了幅频和相频的测试与显示。本系统主要由控制电路,DDS电路,被测电路,混频电路,滤波电路,ADC电路以及显示电路等构成。系统外围电路稳定、可靠,较好的实现了设计目的,达到了各项指标要求。

一. 开发背景

市面上已有的频率特性测试仪都价格不菲,缺乏简易廉价的频率特性测试仪。

二. 结构说明

以控制器STM32F103ZET6作为控制核心,利用DDS专用芯片AD9854产生正交信号,模拟乘法器AD835做混频电路,π型网络做衰减网络,开关电容滤波器MAX297做低通滤波器,再通过OP27放大滤波器的输出信号送入STM32自带的ADC电路进行AD转换,最后用LCD液晶显示屏显示波形, LCD低通滤波器电路作为被测网络,实现了幅频和相频的测试与显示。

三. 功能与使用说明

(1) 通过按键输入可输出0~100MHz的正交信号,频率稳定度≤ ,频率可设置,最小设置单位 100kHz。

(2) 正交信号相位差误差的绝对值≤5º,幅度平衡误差的绝对值≤5%。

(3) 信号电压的峰峰值≥4V,幅度平坦度≤5%。

(4) 可扫频输出,扫频范围及频率步进值可设置,最小步进 100kHz;连续扫频输出,一次扫频时间≤1s。

(5) 能扫频测量并显示幅频特性曲线和相频特性曲线,具有电压增益、相移和频率坐标刻度。

(6) 可进行点频测量;幅频测量误差的绝对值≤0.5dB,相频测量误差的。

绝对值≤5º;数据显示的分辨率:电压增益 0.1dB,相移 0.1º。

四.作品特色

(1) 能够同时显示相频曲线与幅频曲线。

(2) 设计原理简单,易于实现,开发周期短。

(3) 测量准确,系统稳定可靠。

(4) 可通过串口向上位机传输数据。

(5) 能够显示相频曲线。

(6) 能够进行点频测试。

(7) 成本低廉,操作简单。

平台造型说明

设计说明

1系统方案

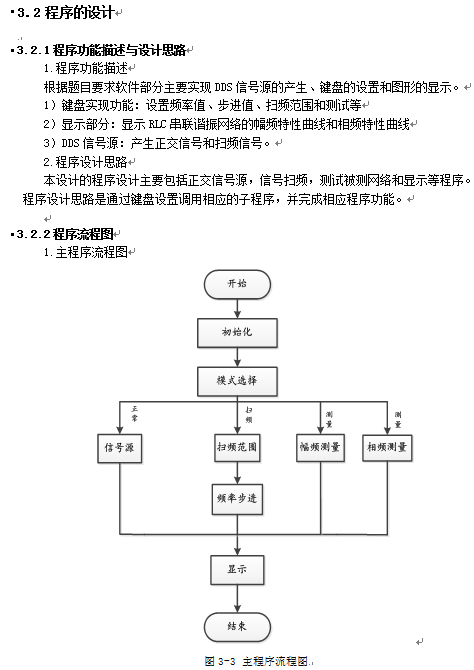

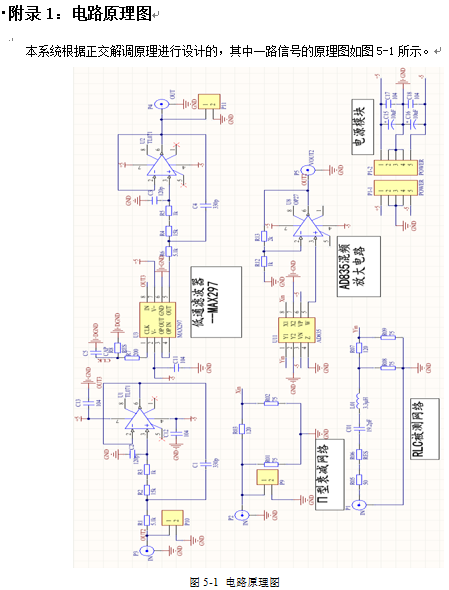

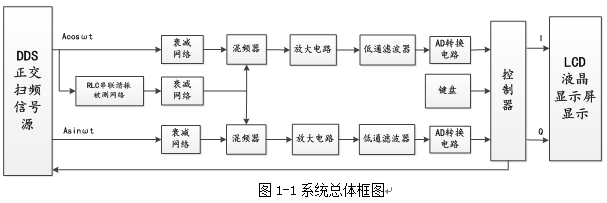

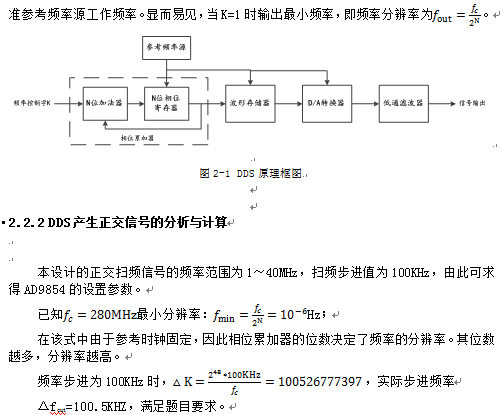

本系统采用零中频正交原理设计频率特性测试仪,主要由DDS模块、RLC串联谐振模块、衰减模块、混频模块、低通滤波模块、放大模块、AD转换模块、显示模块以及键盘模块组成,其系统的总体框图如图1-1所示,下面分别对这几个模块进行论证与选择。

图1-1系统总体框图

1.1 控制器的论证与选择

方案一:采用单片机(AT89C52)作为系统的控制核心。单片机算术运算功能强,软件编程灵活,自由度大,可用软件编程实现各种算法和逻辑控制,但由于设计中编程比较复杂,单片机的硬件设计简单,这就会大大加强软件编程的工作量,可能会导致程序的混乱,且单片机的硬件简单,其口线不足,就可能导致设计不能成功。

方案二:采用 FPGA(现场可编程门阵列)作为系统的控制核心。FPGA 可以实现复杂的逻辑功能,规模大,密度高,它将所有器件集成在一块芯片上,集成度高,减小了体积,提高了稳定性,并且可应用 EDA 软件仿真、调试,易于进行功能扩展。FPGA 采用并行的输入输出方式,提高了系统的处理速度,适合作为大规模实时系统的控制核心。但由于本设计对数据处理的速度要求不高,FPGA 的高速处理的优势不能得到充分的体现,并且由于其集成度高,硬件量大、设计复杂且难度大,可能会影响完成任务的进度。

方案三:采用STM32(STM32F103ZET6)作为系统的控制核心。STM32F103ZET6是STM32系列的增强型芯片,最高72MHz工作频率,工作性能为1.25DMIPS/MHz。片上集成了Flash多达512 KB,SRAM多达64KB的高速存储器和通过APB总线连接的丰富和增强的外设以及多达112个的快速I/O接口。并且拥有2个I2C接口,3个SPI接口(18M位/秒,2个可复用为I2S接口)和5个USART接口。片上还带有3个12位ADC,ADC 最大的转换速率为 1Mhz,1个12位的双通道DAC、11个16位计时器,支持CAN接口、USB2.0接口和SDIO接口。STM32F103嵌入了一个嵌套矢量中断控制器,可以处理43个可屏蔽中断通道,提供16个中断优先级。STM32微控制器可以通过操作库函数开发,开发周期短、便于维护、代码兼容性好、移植简单,接口丰富,工作速度快。由于我们的设计需要使用液晶显示,同时也需要两路ADC同时采集,而STM32能够通过FSMC控制液晶显示,显示速度快,控制简单,并且它有3路ADC,完全能够满足我们的设计要求。

综合以上三种方案,选择方案三。

1.2 DDS正交扫频信号源的论证与选择

方案一:采用锁相式频率合成方案。锁相式合成是将一个高稳定度和高精度的标准频率经过加减乘除运算产生同样稳定度和精度的大量离散频率的技术,它在一定程度上解决了既要频率稳定精确、又要在较大范围内可调的矛盾。但频率受 VCO 可变频率范围的影响,高低频率比不可能做到很高,不能满足题目要求。

方案二:用FPGA和D/A转换器产生符合要求的DDS正交扫频信号。FPGA 的逻辑功能强大,集成度高,减小了体积,提高了稳定度。使用 VHDL 语言,设计灵活,且自由度大,可应用 QuatersII软件仿真、调试、易于功能扩展,但本设计所需要的扫频信号的频率范围为1~40MHz,信号频率比较高,产生的DDS信号精度比较差,稳定性比较差,而且高速的D/A芯片比较难以购买。

方案三:采用直接数字频率合成(DDS)技术。由于DDS采用全数字方式实现频率合成,直接对参考正弦波时钟进行抽样和数字化,然后通过数字计算机技术进行频率合成,因此具有模拟频率合成技术无法比拟的优点。DDS不仅频率转换速度快、频率分辨率高、相位噪声低、输出相位可连续变化,而且易编程,体积小、功耗低。DDS直接频率合成器件的诸多优点使其逐渐成为未来信号源发展方向。由于设计要求能够产生1到40M正交信号,而且各项要求较高,故采用DDS专用芯片AD9854。

综合以上三种方案,选择方案三。

1.3 混频器的论证与选择

方案一:采用二极管平衡混频电路。其优点是噪声低、电路简单,工作频带宽,组合频率少。实际上,由于二极管特性不配对,变压器中心抽头不对称,各端口之间的隔离是不理想的,总会有极少量功率在各端口之间的窜通,这样就会产生组合频率干扰,而且对输入信号的幅度有较高的要求,电路调试困难。

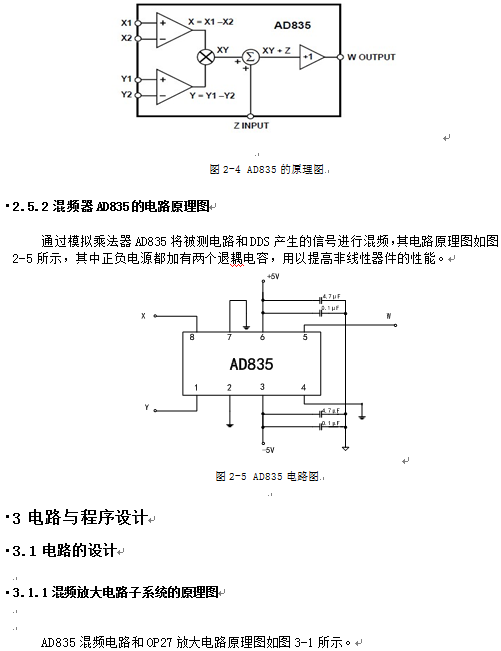

方案二:采用模拟乘法器AD835。乘法器AD835是一个电压输出四象限乘法器,可以实现250M带宽内的混频,能完成W=XY+Z的功能,输出幅值稳定,外围电路少,而且调试简单,这对于我们的设计完全满足要求。

综合考虑采用方案二。

1.4低通滤波器的论证与选择

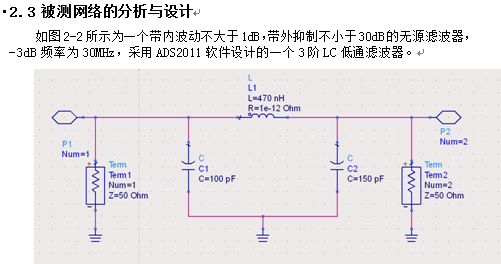

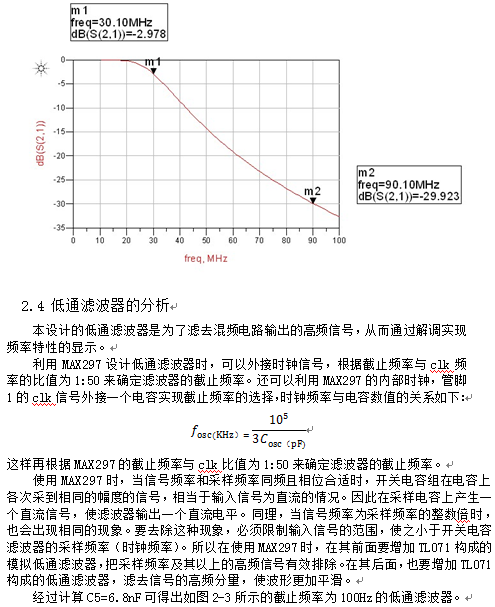

方案一:采用LC构成无源低通滤波器。无源滤波器具有结构简单、成本低廉、运行可靠性较高、运行费用较低等优点,但LC滤波器适合截止频率比较高的滤波电路,采用LC构成无源低通滤波器,其电感值和体积都比较大,不利于集成,同时无源滤波器对负载的影响过于敏感,不利于调谐。

方案二:采用集成运放和RC构成有源低通滤波器。集成运放和RC 组成的有源滤波器,具有不用电感、体积小、重量轻等优点。集成运放的开环电压增益和输入阻抗均很高,输出阻抗小,构成有源滤波电路后还具有一定的电压放大和缓冲作用。但集成运放压摆率和带宽有限,而且必须在合适的直流电源供电的情况下才能使用,所以目前的有源滤波电路的工作频率难以做得很高。一个理想的滤波器应当在要求的通带内具有均匀而稳定的增益,而在通带外则将信号衰减为零,其幅频响应接近矩形,但实际的有源滤波器的通带和阻带都不能达到很好的效果。

方案三:采用滤波器芯片设计低通滤波器。MAX297为MAXIM公司生产的一个8阶低通椭圆型开关电容滤波器,采用输入时钟频率控制输出截止频率的方式实现对模拟信号和数字信号的滤波控制。时钟可调滤波器的截止频率为0.1Hz~50KHz,很容易满足题目要求,而且其带内增益平坦,带外衰减速度很快。

综合以上三种方案,本设计选择方案三。

此文档的相关视频来自:http://v.eepw.com.cn/video/play/id/13511