PCM编译码模块原理

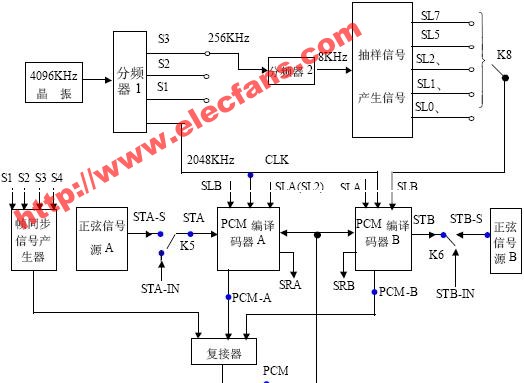

本模块的原理方框图图5-2所示,模块内部使用+5V和-5V电压,其中-5V电压由-12V电源经7905变换得到。

图5-2 PCM编译码原理方框图

该模块上有以下测试点和输入点:

BS PCM基群时钟信号(位同步信号)测试点

SL0 PCM基群第0个时隙同步信号

SLA 信号A的抽样信号及时隙同步信号测试点

SLB 信号B的抽样信号及时隙同步信号测试点

SRB 信号B译码输出信号测试点

STA 输入到编码器A的信号测试点

SRA 信号A译码输出信号测试点

STB 输入到编码器B的信号测试点

PCM PCM基群信号测试点

PCM-A 信号A编码结果测试点

PCM-B 信号B编码结果测试点

STA-IN 外部音频信号A输入点

STB-IN 外部音频信号B输入点

本模块上有三个开关K5、K6和K8,K5、K6用来选择两个编码器的输入信号,开关手柄处于左边(STA-IN、STB-IN)时选择外部信号、处于右边(STA-S、STB-S)时选择模块内部音频正弦信号。K8用来选择SLB信号为时隙同步信号SL1、SL2、SL5、SL7中的某一个。

晶振、分频器1、分频器2及抽样信号(时隙同步信号)产生器构成一个定时器,为两个PCM编译码器提供2.048MHz的时钟信号和8KHz的时隙同步信号。在实际通信系统中,译码器的时钟信号(即位同步信号)及时隙同步信号(即帧同步信号)应从接收到的数据流中提取。此处将同步器产生的时钟信号及时隙同步信号直接送给译码器。

由于时钟频率为2.048MHz,抽样信号频率为8KHz,故PCM-A及PCM-B的码速率都是2Mb,一帧中有32个时隙,其中1个时隙为PCM编码数据,另外31个时隙都是空时隙。

每路PCM信号码速率为64kb/s,一帧中的32个时隙中有29个是空时隙,第0时隙为帧同步码(×1110010)时隙,第2时隙为信号A的时隙,第1(或第5、或第7 —由开关K8控制)时隙为信号B的时隙。

本实验产生的PCM信号类似于PCM基群信号,但第16个时隙没有信令信号,第0时隙中的信号与PCM基群的第0时隙的信号也不完全相同。

由于两个PCM编译码器用同一个时钟信号,因而可以对它们进行同步复接(即不需要进行码速调整)。又由于两个编码器输出数据处于不同时隙,故可对PCM-A和PCM-B进行线或。本模块中用或门74LS32对PCM-A、PCM-B及帧同步信号进行复接。在译码之前,不需要对PCM进行分接处理,译码器的时隙同步信号实际上起到了对信号分路的作用。