运算放大器(简称“运放”)是具有很高放大倍数的电路单元。在实际电路中,通常结合反馈网络共同组成某种功能模块。由于早期应用于模拟计算机中,用以实现数学运算,故得名“运算放大器”。运算放大器是几乎目前所有的电子设备中都要用到的基本器件,因此了解及精通运算放大器设计十分重要。

九层之台,起于累土,首先我们要了解运放的参数。一般运放的datasheet中会列出众多的运放参数,有些易于理解,我们常关注,有些可能会被忽略了。在接下来的一些主题里,将对每一个参数进行详细的说明和分析。力求在原理和对应用的影响上把运放参数阐述清楚。由于本人的水平有限,写的博文中难免有些疏漏,希望大家批评指正。

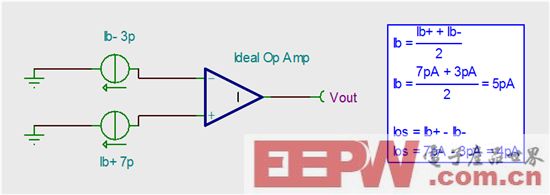

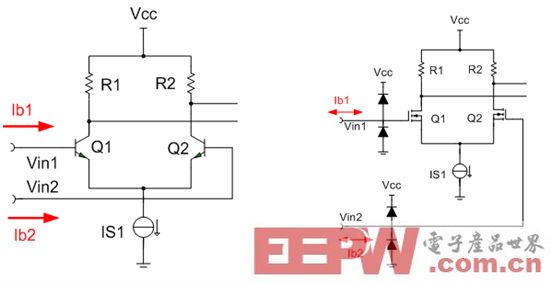

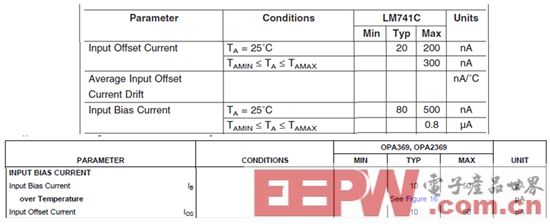

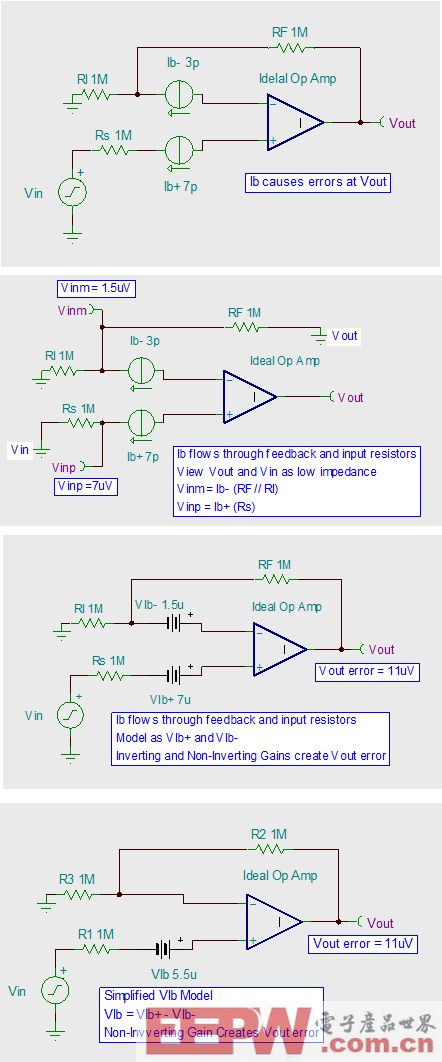

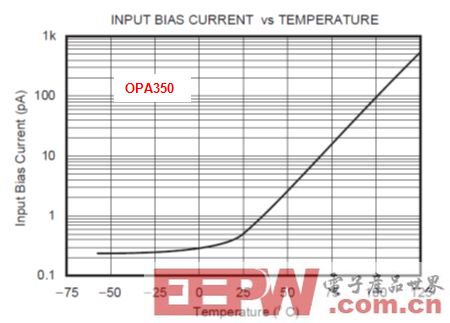

第一节:输入偏置电流和输入失调电流 http://forum.eepw.com.cn/thread/257781/1#2

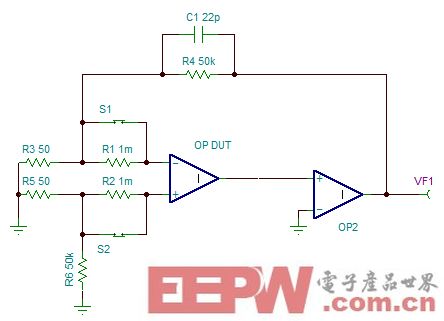

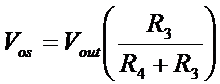

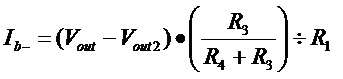

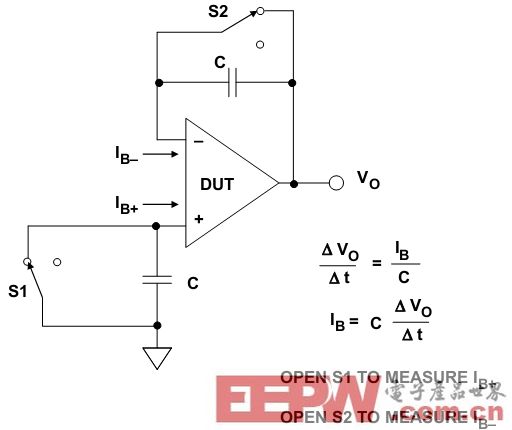

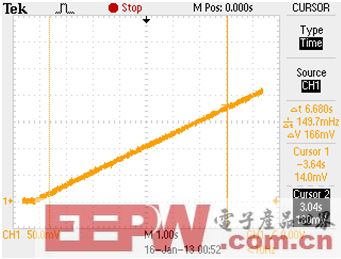

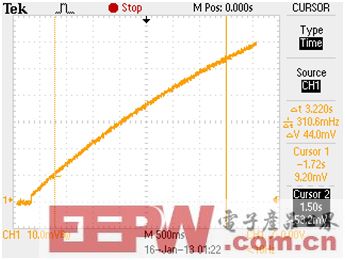

第二节:如何测量输入偏置电流Ib,失调电流Ios http://forum.eepw.com.cn/thread/257781/1#9

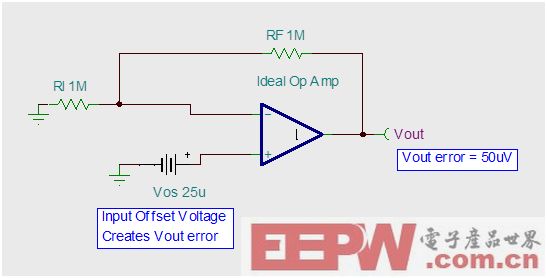

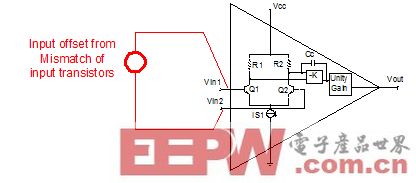

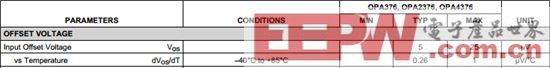

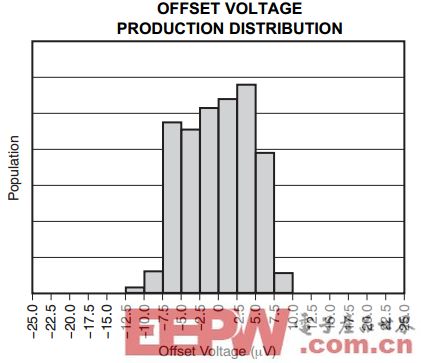

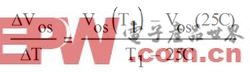

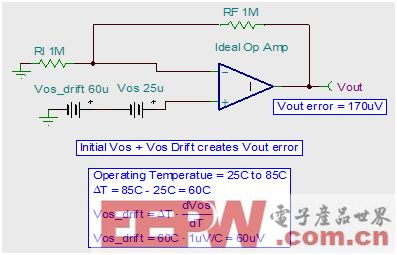

第三节:输入失调电压Vos及温漂 http://forum.eepw.com.cn/thread/257781/1#11

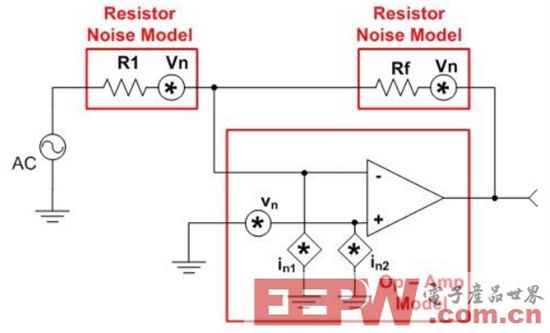

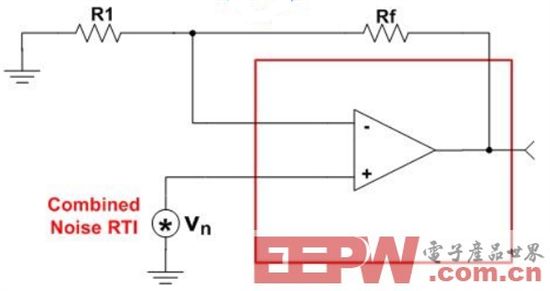

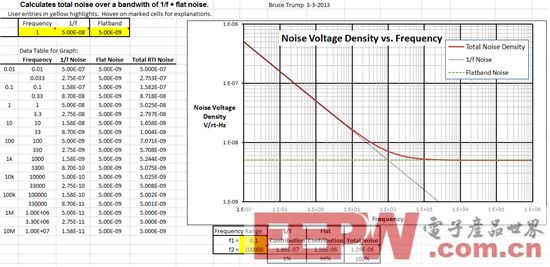

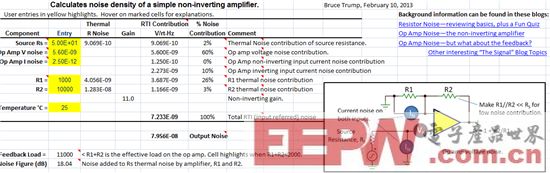

第四节:运放噪声快速计算 http://forum.eepw.com.cn/thread/257781/2#16

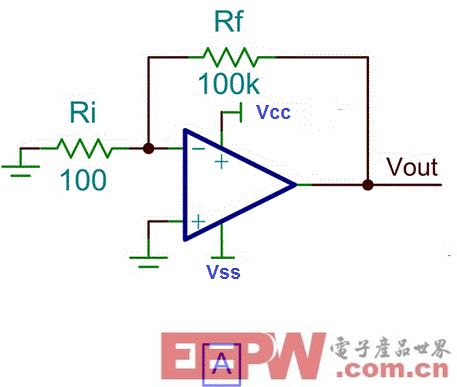

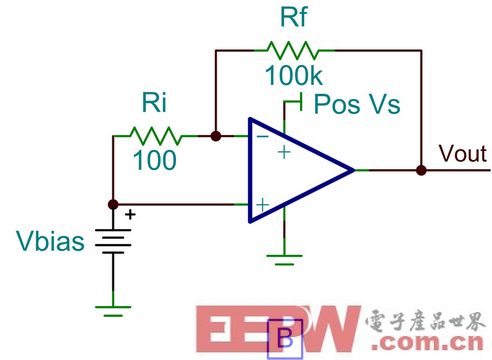

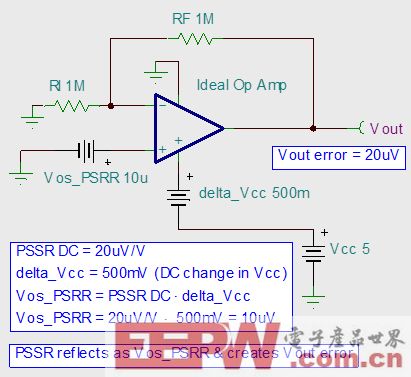

第五节:电源抑制比DC-PSRR http://forum.eepw.com.cn/thread/257781/2#19

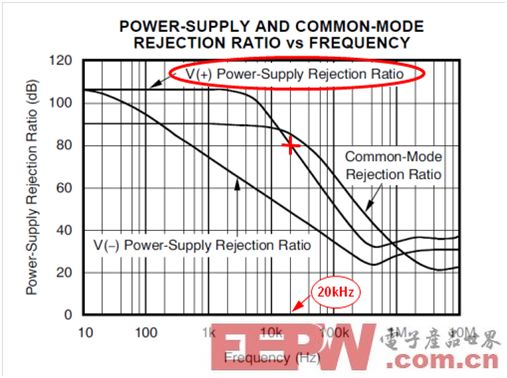

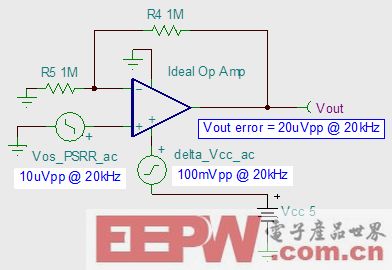

第六节:电源抑制比AC-PSRR http://forum.eepw.com.cn/thread/257781/2#20

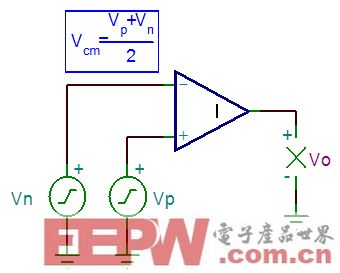

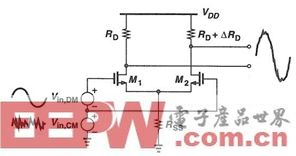

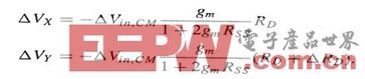

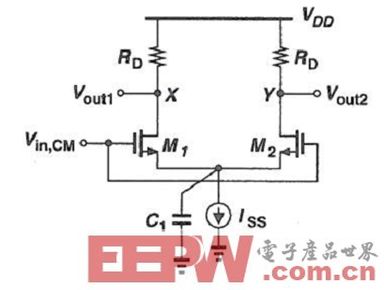

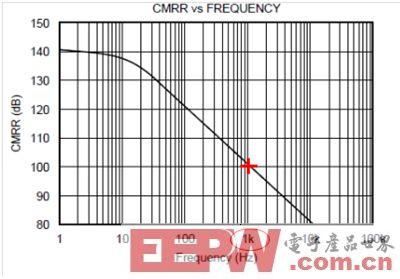

第七节:共模抑制比CMRR http://forum.eepw.com.cn/thread/257781/3#23

第八节:共模抑制比CMRR的影响 http://forum.eepw.com.cn/thread/257781/3#26

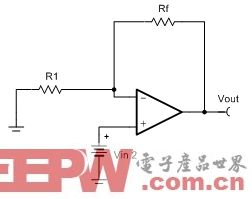

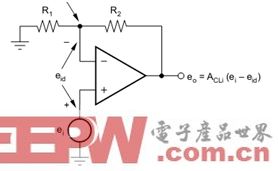

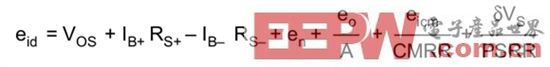

第九节:放大电路直流误差(一) http://forum.eepw.com.cn/thread/257781/3#29

第十节:放大电路直流误差(二) http://forum.eepw.com.cn/thread/257781/3#30

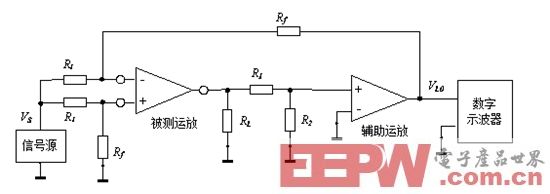

第十一节:输入阻抗和输入电容 http://forum.eepw.com.cn/thread/257781/4#32

第十二节:输入电容Cin的测量 http://forum.eepw.com.cn/thread/257781/4#37

第十三节:轨至轨输入(rail to rail input) http://forum.eepw.com.cn/thread/257781/4#39

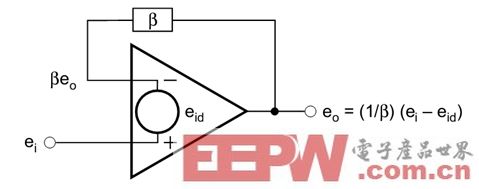

第十四节:轨至轨输入_TI的领先技术 http://forum.eepw.com.cn/thread/257781/4#40

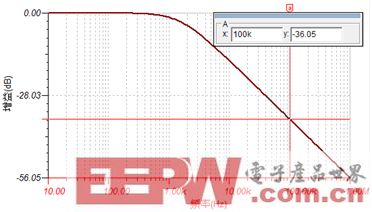

第十五节:开环增益Aol http://forum.eepw.com.cn/thread/257781/5#42

第十六节:增益带宽积(GBW) http://forum.eepw.com.cn/thread/257781/5#43