先说几个名词:

可扩展式处理平台架构, Extensible Processing Platform, EPP, XILINX的ARM+FPGA

这些东东,目前来讲,指的都是一件事,就是XILINX 用28nm HKMG 工艺制成的低功耗,高性能,高扩展性的新型芯片,这款新品里面集成了ARM CORTEX-A9 MPSOC硬核以及相应的SOC系统。

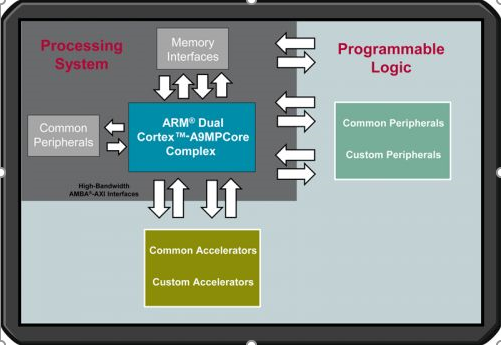

还是先看图吧:

与之有可能相关的一些名词,解释一下:

Cortex-A9 : ARM出的最新款处理器,拥有有主流RISC芯片拥有的所有特点,比如多发射,超标量,乱序,分支预测的等。 主打高性能全功能市场的。

NEON: 这是Cortex-A8, A9等系列配备的用于媒体处理的扩展器, 向量处理,SIMD (单指令多数据)。 你要是还不明白这是什么东东, 当年Intel 发布的带MMX的芯片,就相当于NEON. SIMD的好处是,比如你处理图像,一条指令,就能处理一堆像素,很高效。

SCU: Snoop Control Unit. 侦测控制单元。

中文翻译了以后,你就不知道这是干什么的了。 其实,SNOOP的英文原意就是 “包打听”,“爱偷窥”,就像居委会老大妈,扒在两个小青年的门缝之间偷窥, 专门用来打听两个CPU中,哪一个对cache了写操作,从而可以同步另一个的cache. 因此, 本芯片中的两个Cortex-A9 之所以能够称为Cortex-A9 MPSOC (多核SOC),全靠SCU保持cache的一致性,否则,就是不相关的两个核了。

当然,这个大妈除了管双核Cortex-A9之间的事,还管他们之间对外的事。 比如,他们同时要访问2级缓存L2 cache,冲突了,就要仲裁,调解。 另外,如果硬件加速器需要与他们之间任何一个交流,也要通过ACP和大妈进行协商,就像小区里来了陌生人,大妈先要指使门卫盘问盘问一样。

GIC: Generic Interrupt Controller , 中断控制器。没什么好讲的。

ACP:Accelerator Coherence Port, 加速器一致性接口, 用来管理比如DMA呀, 加解密之类的不带缓存的AXI 外设的, 是一个Slave接口.

AWDT:Application Watch Dog Timer, 应用级看门狗定时器.

SWDT:System Watch Dog Timer, 系统级看门狗定时器 (抑或是软件级看门狗?有点拿不准)

TTC: 这个俺还真不懂, 有知道的朋友吱一声. 从位置上看, 可能是Transaction Timer Controler之类, 也可能是Triple Timer Counter, 也可能是Tick Time Counter.

Coresight Debug: Debug用的口. 比较特别的是,它主要是用来Debug SOC内部的 IP核的. 用这个接口,就可以用JTAG深入芯片内部的各个部件, 以IP为单位,进行DEBUG.

ARM AMBA®-AXI 4 : 这个接口可以有两个master口, 和一个ACP口,交叉连接各种slave.

ASMBL: Xilinx's Advanced Silicon Modular Block, 这个是XILINX的概念, 就是芯片设计模块化, 把逻辑呀,memory呀,时钟啊,DSP块之类的,放在一起,成块状或列状排列, 这样,设计新芯片以及后续测试的时候就会以这些模块为单位进行重用,在此基础上加一些诸如高速I/O这样的不同种类的东东,这样出新产品和新系列就会快很多,这个其实和Structure ASIC有相通之处。 这个概念很早就出来了,大概2003年就有了. 由于字母和 AMBA之类的看上去很像,这里重新辨识一下,以免混淆.

下一篇:Zynq7000启动流程介绍