简介

人工智能 (AI) 现已进入自主系统时代,这些系统将增强人类在计算密集型复杂任务领域的能力。AI 系统既便利又强大,有望解决人类社会面临的各种重大挑战。AI 系统包括三部分:大数据集、数据处理算法和处理数据的计算硬件。

为使 AI 系统切实可用,其必须快速处理大量数据,这样一来就需要强大的计算能力。AI 具有独特的计算能力需求,这就导致 AI 芯片或 AI 加速器市场迅速增长且竞争激烈。能否在这个市场取得成功,取决于能否让产品快速上市,因此就需要使用设计和测试解决方案来应对新型 AI 芯片架构的挑战。本文将重点介绍 AI 硬件的设计,尤其是如何最佳地测试 AI 芯片。Tessent®层次化 DFT 和测试向量生成非常适合 AI 芯片。

它可在较低层级(核心级别)执行 DFT 逻辑插入和测试向量生成,以进行扫描和存储器测试。它可复制 DFT 逻辑并将其与核心复制集成,还能自动将测试向量映射到芯片级别。与 RTL 级测试逻辑插入配合使用时,Tessent 工具相比于传统方法可显著减少DFT 所需的时间。用户实现的扫描测试向量生成速度最多提高了 10 倍,测试向量减少了 2 倍,使用的系统存储器减少了 10 倍。1,2

加速芯片调通方法论的采用,进一步加速了不断发展的 AI 芯片的上市时间。Tessent SiliconInsight®可在DFT 和测试仪领域之间建立直接联系,从而简化了这项极其繁琐的任务。本文阐述了 Mentor Tessent 系列的 IC 测试工具可如何帮助设计人员满足大型先进工艺 AI 芯片的质量和上市时间要求。

AI 竞赛已然开始

openai.com 的数据显示,AI 计算增长需求每 3.5 个月就会翻一倍,自 2012 年以来已增加 300,000 倍。3不同的公司会使用不同的硬件开发技术来满足 AI 计算增长要求。

例如,Graphcore 和 Mythic 等公司的 AI 芯片是基于新型大规模并行架构的 ASIC,此类架构极大地提高了针对 AI 工作负荷的数据处理能力。其他公司(如 Intel、Nvidia 和 AMD)则继续开发和优化现有架构,如 GPU、CPU 和 FPGA 等,以满足 AI 系统的性能需求并保持领先于新兴架构。4

AI 市场非常活跃,超过 50 家初创公司和 25 家老牌半导体公司都在争夺这一新兴市场。5由于 AI 公司的飞速发展,市场竞争也日益激励。

对所有这些竞争者而言,上市时间至关重要。6 设计流程的每个部分—包括 IC 测试和芯片调通所需的一切—都需要朝着尽快将高质量且有效的芯片交付到客户手中这一目标而努力。

AI 芯片特征

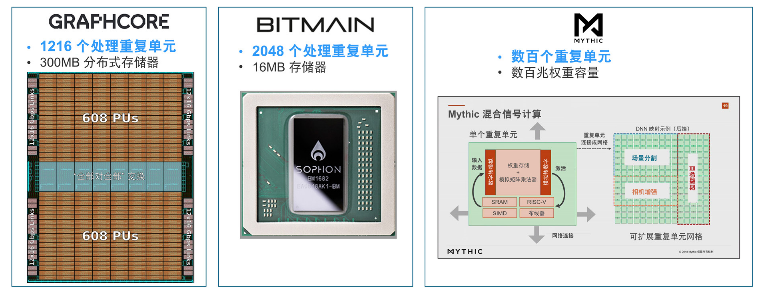

尽管 AI 芯片可以采用不同的实施和架构,但有几个关键设计特征一般是共通的。图 1 显示了 AI 芯片的一些例子。AI 芯片架构和测试要求对 DFT 实施策略具有一定的影响。无论何种架构,AI 芯片通常都有以下设计特征:

•含数十亿门电路的大型设计

•大量复制的处理核心

•分布式存储器

图 1:AI 芯片示例。图片由 Graphcore、Bitmain 和 Mythic 提供。

可大幅缩短 AI 芯片上市时间的 DFT 解决方案要求

为大幅缩短 AI 芯片的上市时间,DFT 解决方案有三个关键要求:

•利用 AI 芯片的规则性

•在 RTL 中执行 DFT 插入

•消除 DFT 到测试的迭代

利用 AI 芯片的规则性

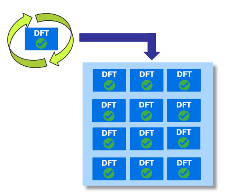

AI 芯片通常包含大量相同的核心。DFT 利用 AI 芯片的规则性意味着所有 DFT 工作—包括测试插入、测试向量生成和验证—在核心级别都需只完成一次。然后会自动复制完整的Sign-off 核心,以完成芯片级 DFT 实施,如图 2 所示。

图 2:以层次化 DFT 方法复制完整的已 Sign-off 的核心

实现一个核心的 Sign-off 并复制该核心以完成芯片的过程要比在芯片级别执行 DFT 快得多。这种方法将 DFT 从流片的关键路径中剥离出来,避免其对项目计划造成影响。

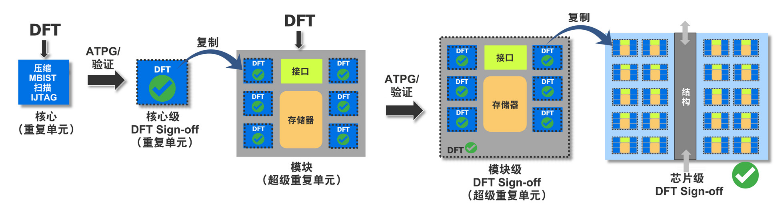

Tessent 层次化 DFT 是一种理想的解决方案,它能利用 AI 芯片的规则性,并允许在不同层级对模块进行完整的 DFT Sign-off。如图 3 中所示,共有三个层级:核心(重复单元)、模块(超级重复单元)和芯片。核心(重复单元)会在模块(超级重复单元)中经多次实例调用,而后者又会在芯片级别经多次实例调用。

图 3:Tessent 层次化 DFT 支持在不同的设计层级进行完整的 DFT Sign-off。

在层次化 DFT 方法论中,DFT 实施、ATPG 和扫描测试向量验证是在核心级别执行的,因此完成后即被认为已 Sign-off。对于接口逻辑和存储器,可在模块级别重复相同的过程。芯片实施完成后,核心和模块的测试向量将由 Tessent 软件自动重新映射到顶层。由于核心和模块是复制的,因此只需针对其中一个核心和一个模块执行 Sign-off 流程。这样将比在完成全部物理设计工作后对整个芯片执行所有 DFT 工作和 Sign-off 要快得多。在 IC 制造完成后的故障诊断期间,Tessent 层次化 DFT 也很有用。它支持核心级诊断,可显著加速诊断和失效分析流程。这种层次化诊断方法论可与包含重复的相同处理核心的 AI 芯片架构完美匹配。

Tessent 层次化 DFT 采用如下独特的技术:

•强大的测试向量重定向和合并功能

•IJTAG 即插即用,用于核心复制和集成

•IJTAG 自动化,用于芯片级 DFT 配置和管理

IJTAG 因其为片上仪器提供的灵活性和自动化而迅速成为 IP 集成和测试的基本标准。Tessent IJTAG 支持Tessent 层次化 DFT 的自动化,并从两个重要方面补充层次化 DFT 方法:1) IJTAG 基础架构的层次化验证;2) 将核心级 BIST 和测试设置 IJTAG 测试向量重新映射到顶层。

对于层次化验证,首先在核心级别验证在该级别插入的 IJTAG 网络,然后再验证各更高级别的 IJTAG 网络。此外,当在下一较高级别(父级别)复制核心时,核心的多个实例的 IJTAG 网络会在父级别自动集成和验证。IJTAG 网络的层次化验证可确保 IJTAG 网络中的任何错误都能在设计流程中尽早发现,从而避免对设计的日程安排造成影响。至于 IJTAG 测试向量重映射,用于扫描测试的测试设置向量(如扫描模式、低功耗配置等)和 BIST 测试向量是在核心级别生成和验证。然而,这些测试向量最终会应用于芯片级别。使用 Tessent IJTAG,核心级 IJTAG 测试向量会自动从核心级别重新映射到芯片级别,这比从顶层生成整个芯片的 IJTAG 测试向量要快得多。在十大半导体主要厂商中,有七家已在使用 Tessent 层次化 DFT 解决方案。

…未完待续…