对许多工程师来说,“时序要求”一词在头脑中唤起的是这样一幅图像:用文本编辑器编写或用约束条件编辑器输入的复杂时序语言,随后是在综合和实施工具间进行的数次反复。Xilinx于8月27日推出的ISE4.1i版本提高了可编程逻辑设计系统生产力的度量标准。除了继续改进工程师用来定义其时序要求的约束类型和方法之外,ISE4.1i更加强调“速度”。“速度”来自具有增强时序工具的快速编译引擎,可支持达到更高性能的时钟。这是通过为设计人员提供一个更加与用户友好和智能的环境来做到的。ISE4.1i通过提供一组称为“主动时序收敛”(“ProacTIveTImingClosure”)的新功能,重新定义了可编程逻辑设计系统的新标准。

主动时序收敛

达到时序收敛是逻辑设计成功的重要标志。由于设计人员的大量时间都花费在试图达到时序要求方面,因此改进时序驱动的编译、实施设计流程,和报告时序处理结果的工具可极大地帮助逻辑设计人员变得更具生产力。

物理综合

对可编程逻辑来说,物理综合不断成长,现已成为一项成熟的技术,可提供使用目标器件时的物理布局信息和网络表,然后再交给实施工具进行处理。

通过与Synplicity合作,Amplify物理优化器(PhysicalOpTImizer)可以利用详尽的、可提供优化过程所需要的布线估计的物理设计知识。其精度允许工程师在尝试完成时序收敛时估计其综合结果的适用性。通过采用这种“两次反复”(TwoPass)方法,设计人员可容易地将时钟性能提高45%以上。此外,Xilinx的目标是达到“一次”完成时序收敛。到那时,综合、布局和布线、分析以及重新综合过程将完全自动化。工具可从错误中进行学习,从而使时序收敛成为一个真正的“按一下按钮即可完成”的系统(如图2所示)。

新布局和布线技术

ISE4.1i大大增强了其时序处理技术。新的布局和布线技术算法也采用了“智能”的多次尝试方法,因此任何具有可行的时序要求的设计都可自动收敛。这样,工具根据时序要求对网络进行优先次序排列并进行布线,对几乎成功的设计布线进行分析、注意异常情况,并计划出处理这些困难的时序问题的新策略,同时保持成功完成时序收敛的区域不动。ISE4.1i中布局和布线算法在一年内将编译速度提高为两倍。ISE4.1i可达到每分钟10万系统门和每小时300万系统门的编译速度。

HDL分析

利用在高效率FPGA设计方面积累的多年经验,Xilinx现在提供了可模拟设计问题并做出可达到更高性能的修改建议的“设计向导”。ISE4.1i可分析RTL源代码及实施工具生成的时序报告,指出设计人员不符合高速设计要求从而会影响设计的最高时钟速度(Fmax)的不良代码和编程习惯。

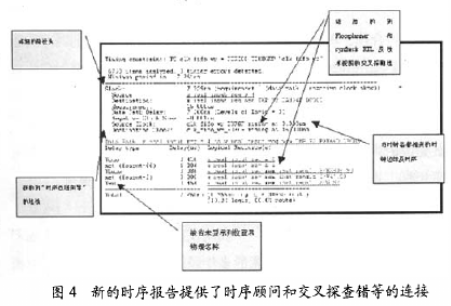

交叉探测检错

对时序报告进行交叉探测检错是ISE4.1i版本的一项重大突破。用户可从时序报告中选择有问题的地方,然后源代码工具将会显示出有问题的网络。这一新的扩展功能将问题定位从传统的时序报告扩展到合作伙伴综合工具以及模块划分工具(如图3所示);这进一步缩短了在不同工具和GUI间搜索同一网络所花费的时间,从而加快了设计调试时间。同时,时序分析器功能也增强了,设计人员可通过不同的选项,包括网络源、网络终点和线路,寻找和发现问题区域,这也进一步提高了开发系统的易用性。最重要的是,ISE4.1i增加了时序顾问功能(TImingAdvisor),可为如何改进时序关键的网络提供建议(如图4所示)。

最后,但也相当重要的是,数百万系统门的FPGA设计正变得越来越普遍。Xilinx意识到需要解决挑战ASIC设计人员多年的设计验证瓶颈。因此,ISE4.1i在业界第一个支持形式验证工具,包括Synopsys公司的FormalityTM和Verplex的ConformalLEC,以及市场上的领先静态时序分析器,SynopsysPrimetimeTM。通过推出这一系列“主动时序收敛”功能,并支持多种验证策略,和改善用户界面,XilinxFPGA设计人员可在设计过程中快速设计、实施和检验高密度设计,极大地加快他们的产品上市时间。