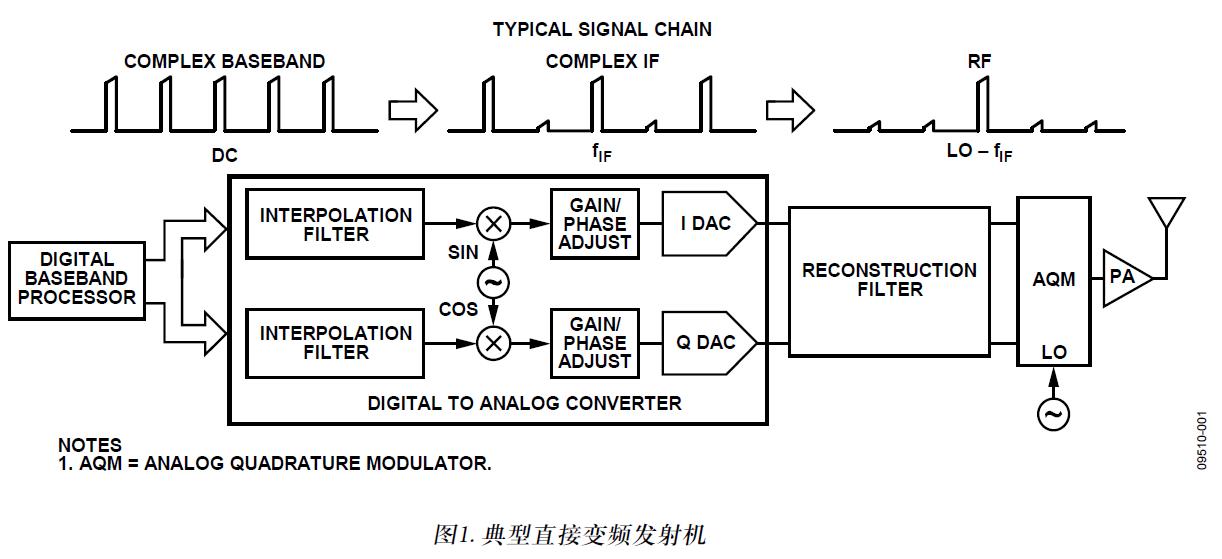

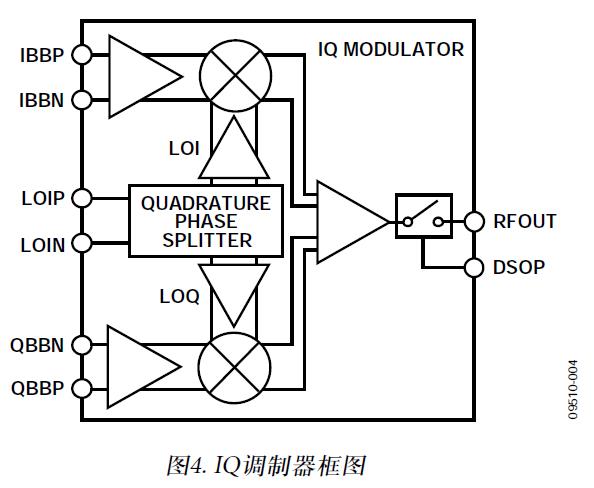

直接复调制逐渐成为在蜂窝基站、WiMAX、无线点对点等终端应用中部署发射器信号链的首选架构。这种技术直接将数模转换器的输出IQ信号调制到RF载波上(直接转换),从而摆脱中间IF级和相关滤波器。图1显示典型的直接转换发射器。

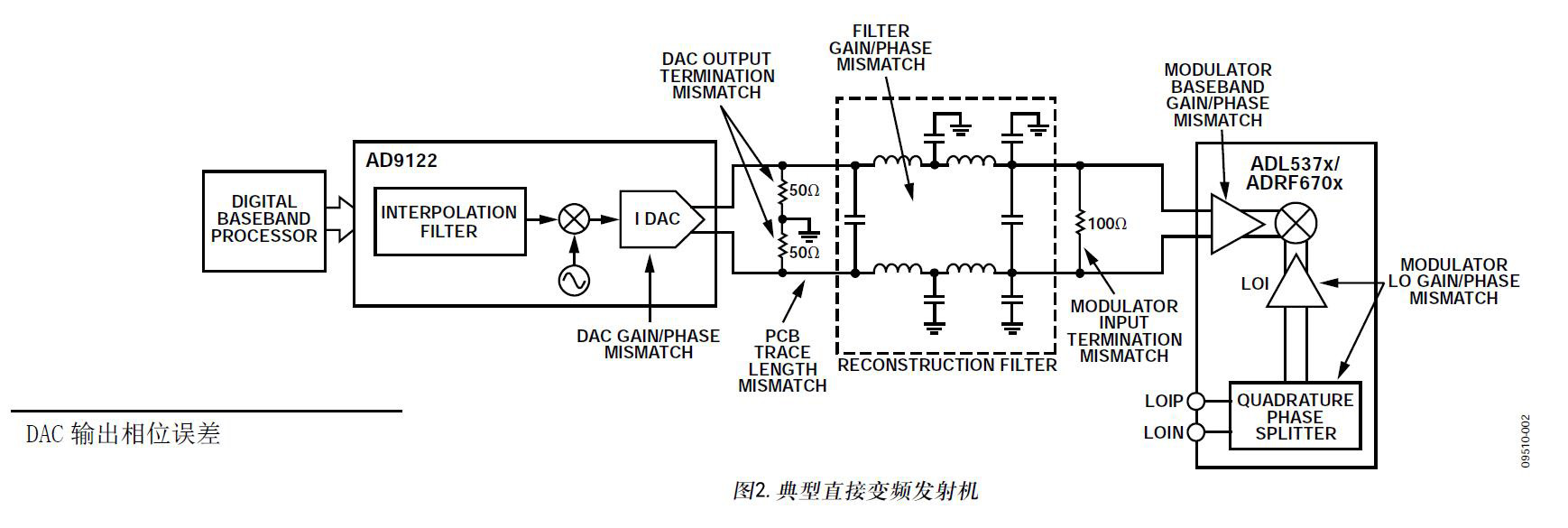

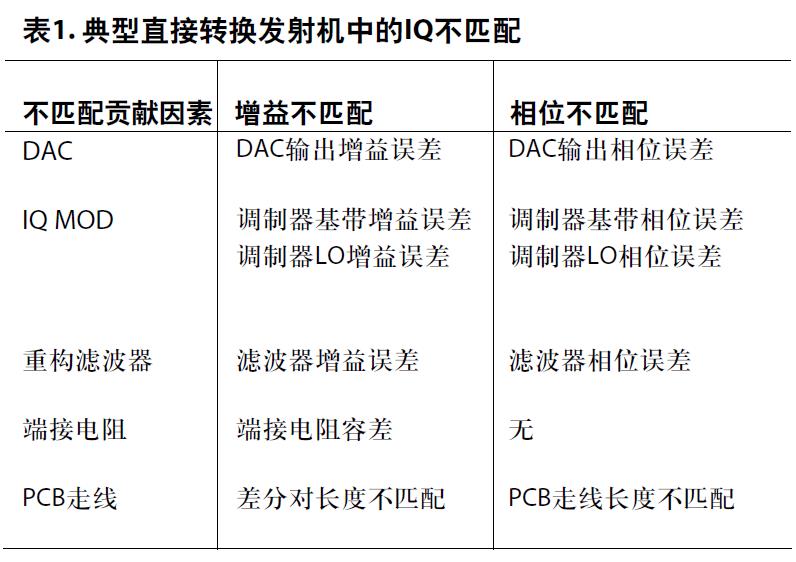

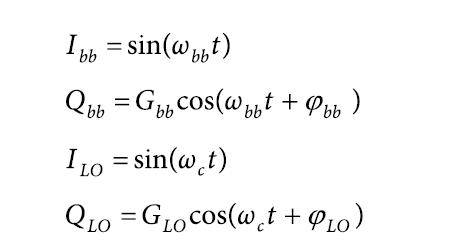

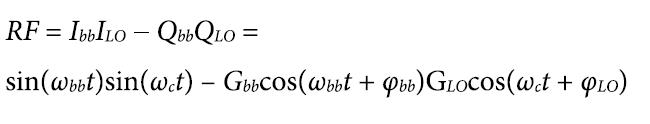

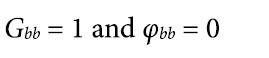

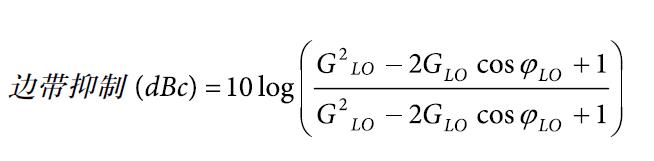

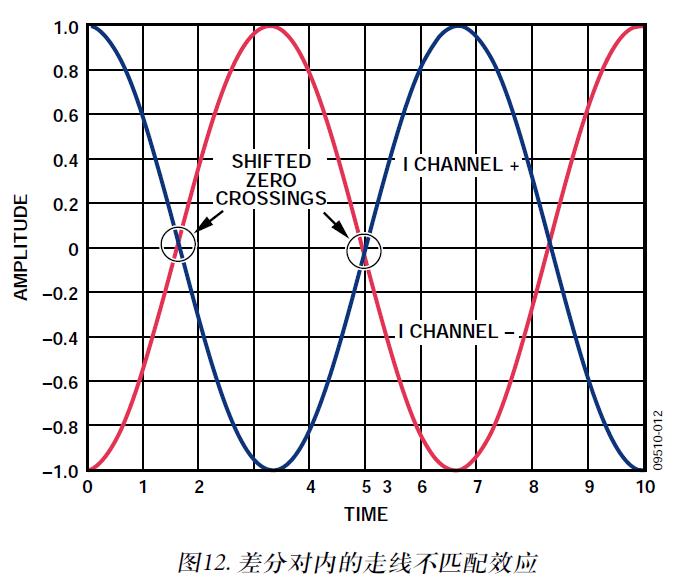

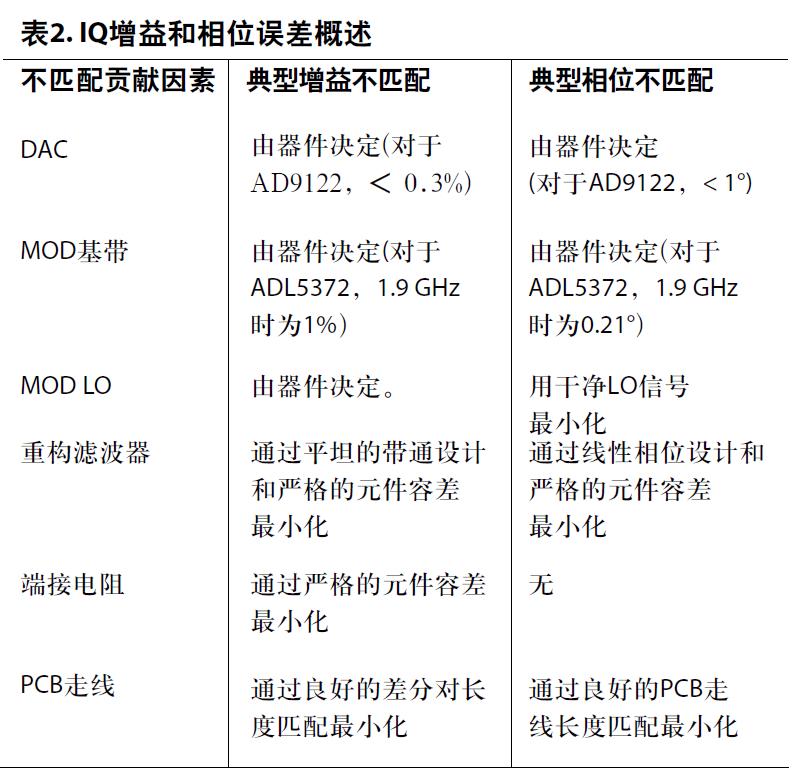

在模拟调制过程中,IQ信号的增益和相位不匹配会直接影响边带抑制性能,这会导致接收器端的误差矢量幅度(EVM)增大,从而提高比特误差率(BER)。

我们要考虑造成边带抑制不理想的主要原因,以及有关器件选择和PCB设计/布局的设计。

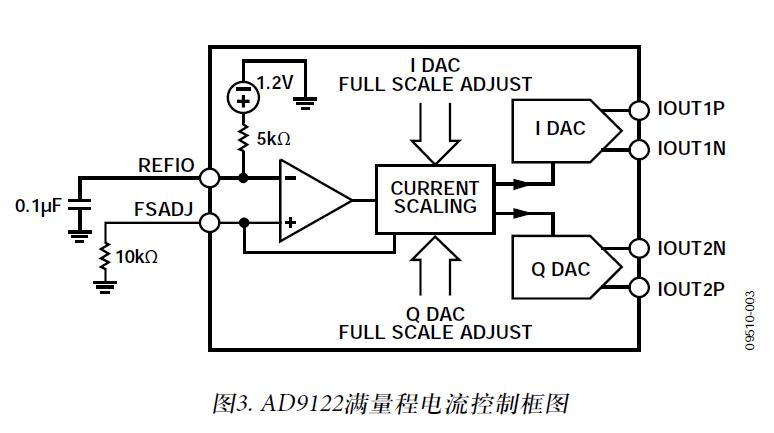

此方案中的无线发射机示例由ADI公司的AD9122 TxDAC+和模拟正交调制器(例如ADL5375、ADL5372)和/或ADI公司的ADRF670x组成。

所提供信息同样适用于其他ADI公司高速DAC产品,如AD9125、AD9148、AD9788和AD9779A。