摘要:随着芯片集成度的提高,对一些功能复杂的系统芯片功耗的管理,已经引起大家越来越多的重视,如何控制好SoC的功耗将成为芯片能否成功的重要因素。本文提出一种通过动态管理时钟的策略,达到降低整个SoC芯片功耗的目的;同时,分析动态管理时钟方案中可能会出现的一些问题,并给出解决方案。

关键词:系统芯片 毛刺 AMBA 总线 时滞

引 言

??随着集成电路技术的飞速发展和对消费类电子产品——特别是便携式(移动)面向客户的电子产品的需求,推动了SoC(System on Chip)的飞速发展,也给人们提出了许多新的课题。对于电池驱动的SoC芯片,已不能再只考虑它优化空间的两个方面——速度(performance)和面积(cost),而必须要注意它已经表现出来的且变得越来越重要的第三个方面——功耗,这样才能延长电池的寿命和电子产品的运行时间。

SoC中CMOS电路功耗有:一是静态功耗,主要是由静电流、漏电流等因素造成的;二是动态功耗,主要是由电路中信号变换时造成的瞬态开路电流(crowbar current)和负载电流(load current)等因素造成的,它是SoC芯片中功耗的主要来源。因此,解决好SoC中的动态功耗是降低整个SoC芯片功耗的关键。本文后面所提到的功耗就是指SoC芯片中的动态功耗。

如何降低SoC中的功耗,从不同的层面分析会得出不同的解决方案。从芯片的系统级(architecture)角度考虑,有低功耗总线设计、低功耗存储系统设计、低功耗时钟网络设计、开发系统的休息模式、时钟门控等技术;从芯片的行为级(RTL)角度考虑,有信号门控、预前计算、操作数分离、状态机优化、并行和流水结构等技术;从芯片的门级(gate)角度考虑,有缓冲插入、提取因子、单元缩放、管脚交换、相位配置等技术[4]。从越高的抽象层次去考虑功耗问题,芯片功耗优化的幅度就越显著。

本文所提出的基于动态配置时钟的SoC低功耗管理是从芯片的系统级角度考虑的。在最后的实验中,它非常明显地降低了整个芯片的功耗。

1 动态配置时钟的SoC低功耗管理原理

基于微处理器应用的SoC设计,其复杂程度变化很大:在一些应用中可能需要用到所有的硬件资源,但是在其它的一些应用中可能只需要用到其中一部分硬件资源;在一些应用中可能需要很高的工作频率,而在其它的一些应用中却可以大大降低工作频率。动态管理SoC系统时钟的思想就是:不仅动态地管理SoC内部模块的时钟源供给,还可以动态地配置SoC系统的时钟频率。

动态地管理SoC内部模块的时钟源供给就是,根据不同的应用,管理SoC内部的硬件资源。简而言之,就是进行内部模块的开和关的操作。关闭单个模块,可以通过对每个模块设置一个使能位,然后对这个使能位编程做到关闭或打开那个模块。但这样做不是最佳的,原因有二:其一,每个模块的接口部分必须是始终打开的,否则,CPU核无法随时对它的内部寄存器进行编程;其二,通过模块使能位只是关闭了它的功能操作,而并没有把它模块内的时钟树关闭掉,也就是说它里面的时钟树依然处于激活状态,而时钟树所造成的功耗占单个模块功耗的很大一部分。其实大多数模块都是同步系统,系统的所有操作都是在时钟信号的节拍下进行的[5],关闭时钟源能同时达到关闭模块和降低功耗的目的。

动态地配置SoC系统的时钟频率则是以不牺牲系统的性能为前提,动态地管理系统的工作频率来降低SoC的功耗。时钟频率是影响动态功耗的重要因素:。它的工作频率越高,功耗也就越大。但在很多时候,所有的模块并不是工作在同一时钟频率,或者同一个模块在不同的时段可以工作在不同的时钟频率。这些就是动态地配置SoC系统的时钟频率的前提。

图1是整个SoC中的时钟网络(时钟树)。图中的功耗管理模块(power management module)完成这种功能。

2 芯片的低功耗工作管理模式

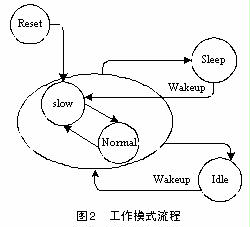

为了更好地实现动态配置时钟的SoC低功耗管理策略,芯片在其工作中开发出了其低功耗管理机制中的四种工作模式:Slow、Normal、Idle和Sleep。下面结合图2所示的工作模式流程图来说明它的工作机制。

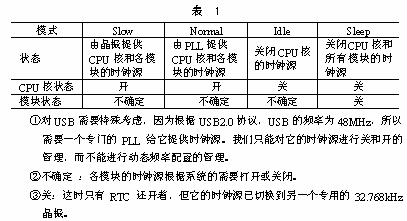

表1为四种工作模式的状态。

(1)Slow模式

当系统复位以后或当系统关掉PLL不需要高速时钟运行时,系统进入到Slow模式。在Slow模式下,系统中的CPU核和所有模块的时钟源都来自晶振。如果这时系统认为有必要关掉某些模块,那么,就可以通过配置功耗管理模块内部的寄存器,把相应模块的时钟源使能位关掉。

(2)Normal模式

如果在某些应用中需要高速时钟,那么就应该切换到Normal模式。在Normal模式下,系统中的CPU核和所有模块的时钟源都来自PLL。当然,在这种模式下也可以根据系统的应用关掉某些模块。如果系统需要调整时钟的频率,可以通过动态配置PLL来实现。但是在动态配置PLL过程中,要注意这样一个问题:因为PLL有一个时钟锁定的时间,在这段时间内,它输出的时钟波形是不规则的,此时不能使用它作为芯片的时钟源。为了保证系统的正常运行,可以暂时把系统的时钟源切换到晶振状态,待PLL的时钟输出稳定以后再把系统的时钟源切换到PLL状态。

(3)Idle模式

如果CPU核在当前状态下已经处理完所有任务,在很长一段时间内都将处于空闲状态,那么系统应该进入到Idle模式。在Idle模式下,只会关闭CPU核的时钟源,而所有的模块都保持原状。但在这种模式下,不可动态配置PLL,以得到不同的时钟频率;也不可以动态地管理各模块的时钟源,因为这个时钟Core已经休眠了,它没办法对功耗管理模块内部的寄存器进行配置。无论前一个状态是Slow模式还是Normal模式,系统都可以进入到Idle模式下;而当系统退出Idle模式时,它应该退回到前一个工作模式。当系统重新需要CPU核进行事务处理时,可以通过一个唤醒信号让系统退回到Slow模式或Normal模式。

(4)Sleep模式

如果整个系统都已经处理完所有的事务,并且在很长的一段时间内都将处于空闲状态,那么系统应该进入到Sleep模式。在Sleep模式下,关闭CPU核和所有模块的时钟源。虽然可以从Slow模式或Normal模式切换到Sleep模式,但是当它退出Sleep模式时,系统只能回到Slow模式。因为为了进一步降低整个芯片的功耗,在Sleep模式时会同时关闭PLL,所以在它退出时只能回到Slow模式,然后根据当前的应用决定有没有再切换到Normal模式的必要。当系统需要再次进行事务处理时,可以通过一个唤醒信号唤醒整个SoC芯片系统。

3 功耗管理模块的实现

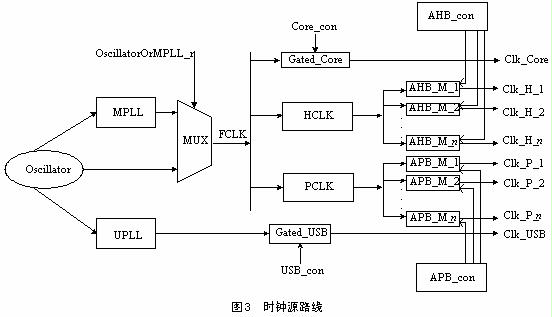

功耗管理模块主要由一个状态机、一些多路选择器和一些门控时钟电路组成。状态机的责职就是完成各种模式之间的切换和送出PLL的控制信号。多路选择器主要完成各种时钟源之间的选择,而门控时钟电路则完成CPU核和各模块时钟源的打开和关闭功能。图3是功耗管理模块中时钟源路线。

从图3中可以清楚地看出,在功耗管理模块中例示了两个PLL:一个是主PLL(MPLL),它提供整个SoC中除USB模块以外的所有模块的时钟源;另一个是次PLL(UPLL),它只对USB提供时钟源。MUX完成晶振时钟和PLL时钟的选择,被选中的时钟(FCLK)同时送到CPU核、HCLK和PCLK,然后根据各个模块的需要门控地送出时钟源。这是基于AMBA总线结构的SoC。根据AMBA总线的协议,CPU核、AHB上的模块和APB上的模块的时钟频率可以配置成倍比关系[6]。经过HCLK分频的时钟源只提供给AHB上的模块,而经过PCLK分频的时钟源只提供给APB上的模块。AHB_con 、APB_con、Core_con和USB_con一起管理SoC内部模块的时钟源供给。

4 动态时钟管理中的问题及消除方法

动态地配置整个系统的时钟频率,虽然可以很方便地控制好整个SoC芯片的功耗,但同时也带来了一些负面影响。功耗管理单元中的多路选择器和门控时钟电路是最有可能产生毛刺的,而毛刺对同步数字系统是致命的。它会导致同步的失败、数据的丢失、寄存器进入亚稳态,更为严重的是,使整个同步系统的功能失败。毛刺的产生是因为那些输入信号的时序匹配出现了问题,没有按照既定的顺序出现,或者说那些信号装转换的时机不合适。因此在RTL设计时要保证做到时序的匹配,以降低毛刺产生的可能性。

在功耗管理模块中有三种情况需要用到多路选择器:

a. 由Slow模式切换到Normal模式;

b. 在Normal模式下重新配置PLL;

c. 由Normal模式切换到Slow模式。

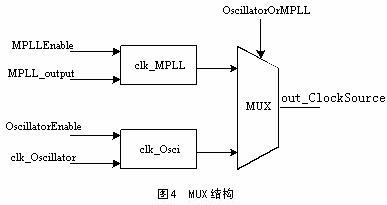

图4是功耗管理模块中的一个二选一MUX。它的控制信号是OscillatorOrMPLL,两个选择源是clk_MPLL和clk_Osci,输出是out_ClockSource。当OscillatorOrMPLL为“1”时,MUX选中clk_Osci;当OscillatorOrMPLL为“0”时,MUX选中clk_MPLL。在MUX选择其中任何一个时钟信号之前,clk_MPLL或clk_Osci必须已经稳定下来了。强调一下,这里的稳定不是指已经输送出完整的时钟信号,而是输送出高电平或低电平。这样当选择开关达到它们那一方时,接受到的是没有毛刺的且对整个SoC不会产生操作的时钟信号。虽然在这时因为这种操作把SoC的频率降了下来,但这是暂时的(大约2~3个晶振时钟周期),因此对整个SoC性能的影响是微乎其微的。接下来被选中的信号(clk_MPLL或clk_Osci)才开始输送出没有毛刺的时钟信号,从而最终送出的时钟信号是去除了毛刺的。

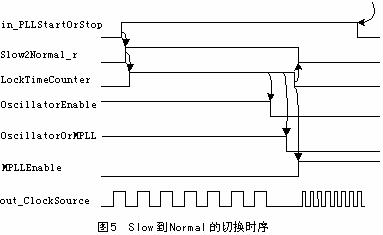

图5是系统从Slow模式切换到Normal模式时的时序图。通过配置功耗管理模块的内部寄存器打开PLL,即in_PLLStartOrStop信号,由它触发Slow2Normal_r信号,表明当前将要从Slow模式过渡到Normal模式。然后,由这个信号触发Lock Time 计数器开始计数(计数值由PLL的IP提供商所给的公式中确定),接着先把晶振时钟的使能信号关掉,再把多路选择器打到MPLL那一方。最后,把PLL时钟的使能信号打开,这时得到的就是经过倍频的PLL时钟。

从时序图可以清晰看出,在时钟源切换的过程中,最终送出的时钟(out_ClockSource)频率会很明显地降低下来(大约是晶振时钟频率的1/3或1/2);但是如果选择的晶振时钟频率在10MHz以上,则不会对整个SoC芯片的性能产生影响。

至于门控时钟电路,已经有许多人在这方面作了很广泛的研究,本文不再对此作过多的解释[7]。

5 结 论

本文提出了一种SoC芯片的低功耗管理策略。其基本思想是,首先从全局考虑,在满足性能的前提下,根据各种应用环境动态地配置SoC芯片的时钟频率。然后,从局部单独考虑单个模块,通过判断它当前的工作状态决定是否打开其时钟源。

该低功耗管理方案已经应用于我们设计的一款SoC芯片——Garfield。经过表2所列Power Compiler的功耗分析,可以清晰地看出:在Slow模式下的功耗仅为Normal模式下功耗的17%左右,而在Sleep模式下的功耗更低。

参考文献

参考文献

1 Bill Moyer. Low-Power Design for Embedded Processors

2 Jerry Frenkil, Sequence Design Inc. Santa Clara, CA A multi-level approach to low-power IC design. IEEE Spectrum (Volume 35, Number 2, February 1998)

3 Secareanu Radu M. David Albonesi and Friedman Eby G. A Dynamic Reconfigurable Clock Generator. Motorola, Inc, Semiconductor Products Sector, Digital DNA Laborites, Tempe, AZ 85284 University of Rochester, Department of Electrical and Computer Engineering, Rochester, NY 14627-0231

4 Nassiri Hamid R. Low power design. Synopsys SUNG

5 Rabaey Jan M. A Design Perspective——数字集成电路设计透视. 1999

6 Caldari M, Conti M, Crippa P, et al. Dynamic Power Management in an AMBA-Based Battery-Powered System. Departimento di Elettronica e Automatia, University of Ancona Via Brecce Bianche, I-60131 Ancona, ITALY

7 Sujit Dey, Anand Raghunathan, Jha Niraj K, et al. Controller-based power management for control-flow intensive designs. 1999

8 MIPS Technologies Inc. Darren Jones. How to Successfully Use Gated Clocking in an ASIC Design

9 AMBA Specification 2.0 . ARM corporation