物联网跨越多个应用领域,设计团队的要求可能因最终应用领域而异。虽然功率、性能和成本是电子元件硅设计中要满足的标准优先事项,但汽车和航空航天/国防等应用领域将安全性添加到设计优先事项列表中,而在其他领域,安全性是关键或现场可升级性需要被考虑。

验证、原型设计和软件开发是跨这些领域和设计要求的共同主题。为了允许嵌入式软件开发,经典的早期验证技术(如模拟)通常被认为太慢,而使用 QEMU 等虚拟平台的抽象有时被认为不够准确。

长期以来,基于 FPGA 的原型设计一直是硅前软件开发的首选平台。与它的老大哥硬件仿真相比,在 Cadence Palladium Z1 企业仿真平台等工具中,它的执行性能从 MHz 级扩展到 10 兆赫兹甚至 100 兆赫范围,而且成本更低,允许将其复制给软件团队的更多成员。

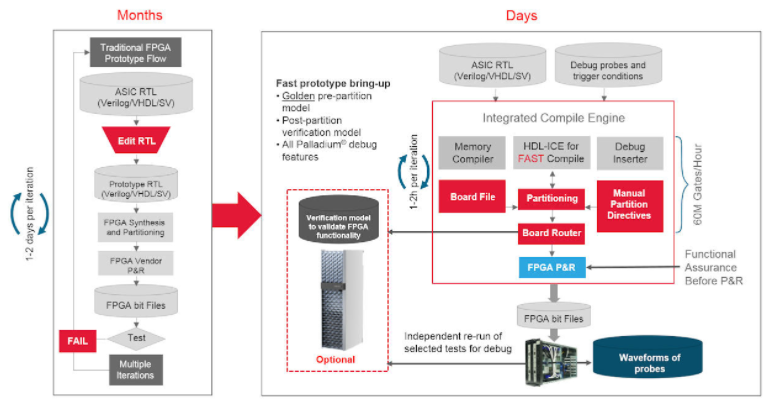

传统上,基于 FPGA 的原型的障碍一直是它的启动过程,有时需要几个月的时间才能提供给软件开发人员。原因是需要将 ASIC 设计从其实际的硅目标技术重新映射到 FPGA 提供的结构中,这需要重新映射部分设计。

首先,ASIC 中的存储器需要映射到 FPGA 中可用的资源中,或者映射到包含特定附加存储器(如 DDR)的子卡中。处理 ASIC 的时钟可能是一场噩梦,在 PCB 和 FPGA 上更复杂的设计中需要同步 10 多个时钟。跨多个 FPGA 对设计进行分区绝非易事,而且通常需要使用低压差分信号 (LVDS) 技术在同一引脚上多路复用多个信号。

[Palladium Z1 和 Protium S1 平台的 Cadence 多结构编译流程。]

传统上,较大的公司拥有原型设计团队,专门负责设计团队正在开发的 RTL 版本并将其映射到 FPGA 中。然而,随着设计复杂性的增加,执行上述所有任务变得越来越困难,而软件开发人员则不耐烦地在团队上空盘旋以访问它。

借助基于 Protium S1 FPGA 的原型设计平台,Cadence 重新审视了原型设计,并专注于将原型设计时间从数月缩短至数周甚至数天。它通过在 Palladium Z1 仿真和基于 Protium S1 FPGA 的原型设计之间实现一致性,以及重新使用一些仿真前端进行原型设计来做到这一点。

复杂的手动内存建模已使用仿真中已知的内存模型自动化;编译流程负责 FPGA 之间的分区和时钟同步。可以在仿真中验证要映射到 FPGA 架构的网表,从而节省宝贵的布局布线时间。一旦在基于 FPGA 的原型设计中以比仿真快约 5 倍的速度识别出缺陷,就可以将相同的设计推回仿真,以利用那里提供的更好的调试功能。

作为还包括形式验证、仿真和仿真的 Cadence 验证套件的一部分,基于 FPGA 的原型设计刚刚通过自动化进行了重新发明,并可供更广泛的物联网设计开发人员使用。