前言

本操作如何固化ZYNQ PL端程序到FLASH分享---基于广州星嵌电子科技有限公司设计研发的Zynq7015平台。

FLASH型号

板载QSPI FLASH一颗,具体型号为:MT25QL256ABA1EW9-0SIT。

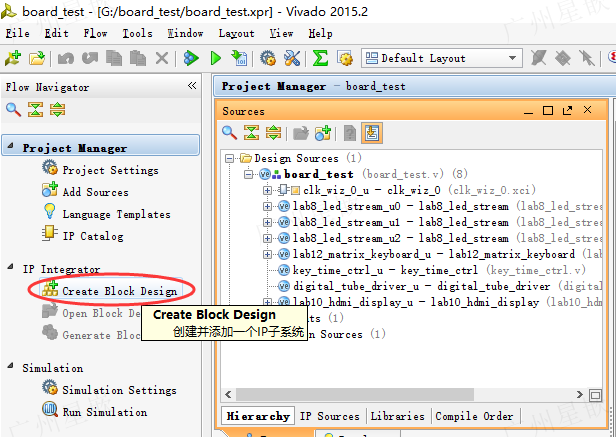

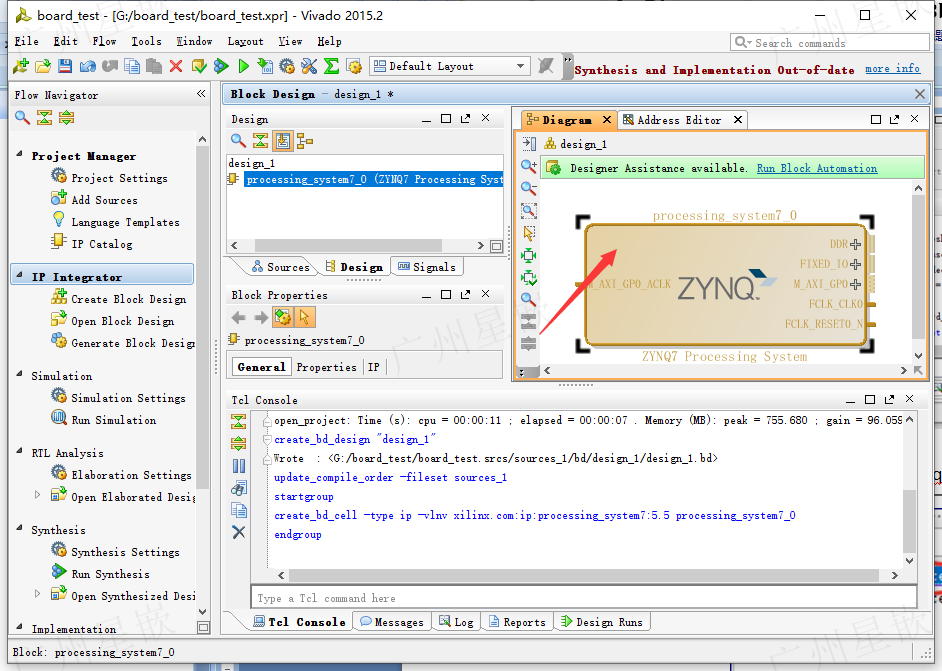

首先,打开已经完成的Vivado设计例程,点击Project Manager下面的IP Integrator -> Create Block Design,创建Block Design设计文件:

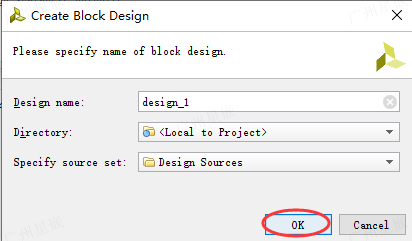

在弹出的对话框中,点击OK:

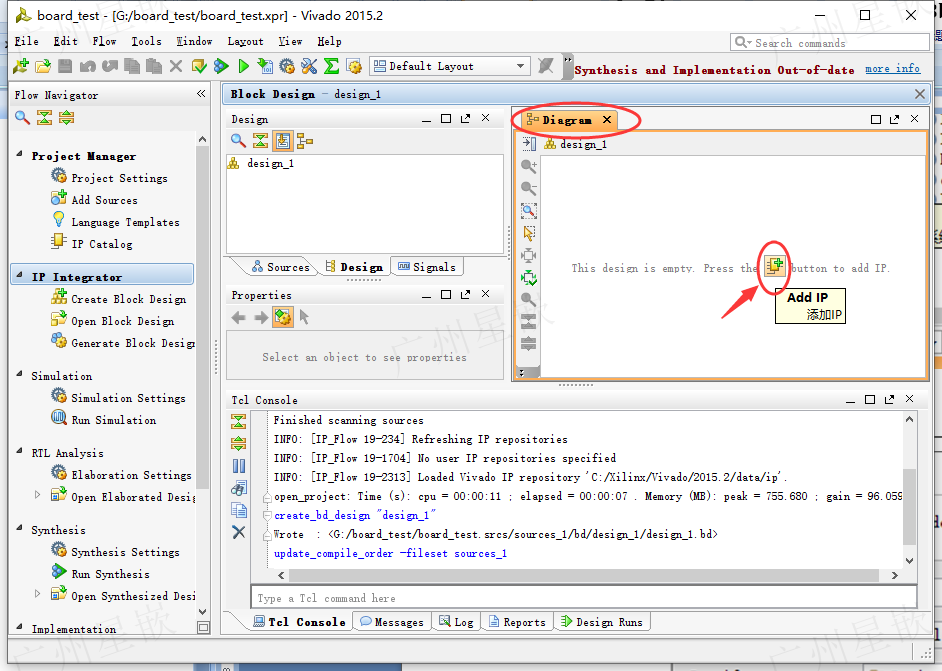

在Diagram窗口,点击中间加号按钮,添加IP:

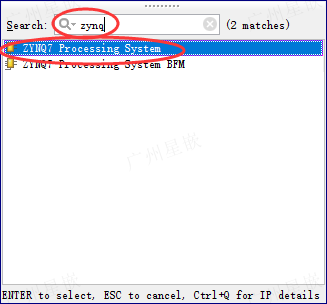

在弹出的IP添加窗口的搜索栏中,输入zynq字样,然后双击选中ZYNQ7 Processing System:

添加好ZYNQ7 Processing System IP核后,双击该IP核,对此IP核进行配置:

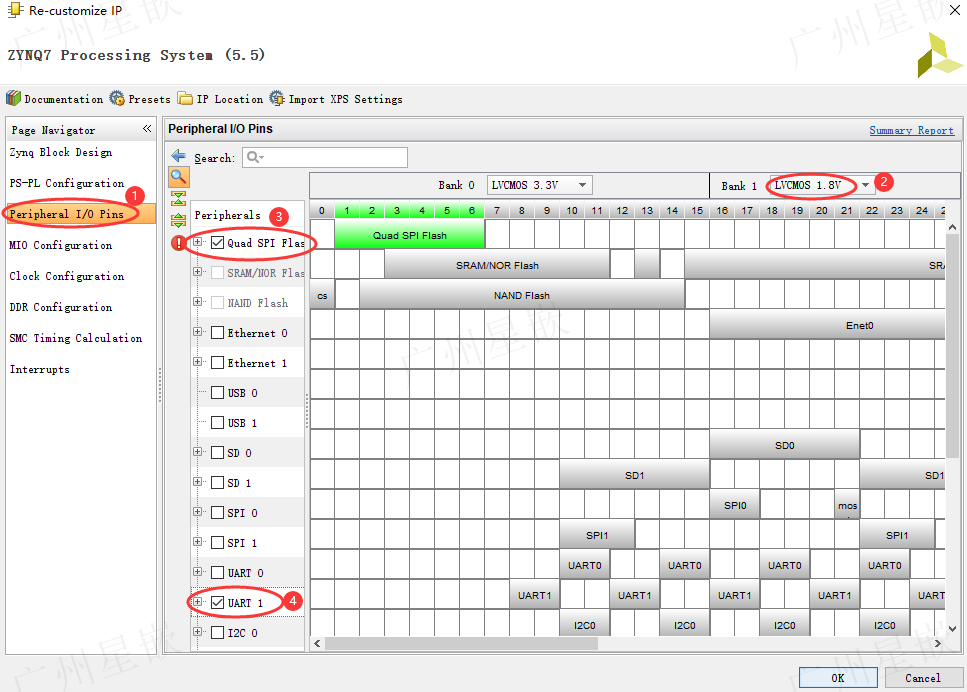

设置ZYNQ7 Processing System IP核的外设IO:

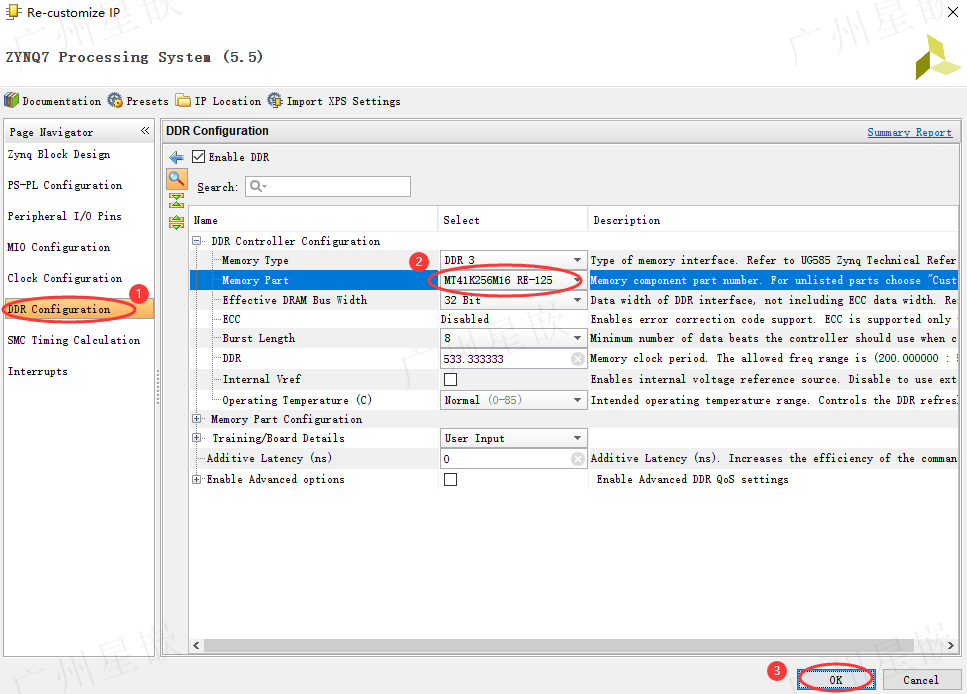

设置ZYNQ7 Processing System IP核的DDR内存,然后点击OK,完成IP核配置:

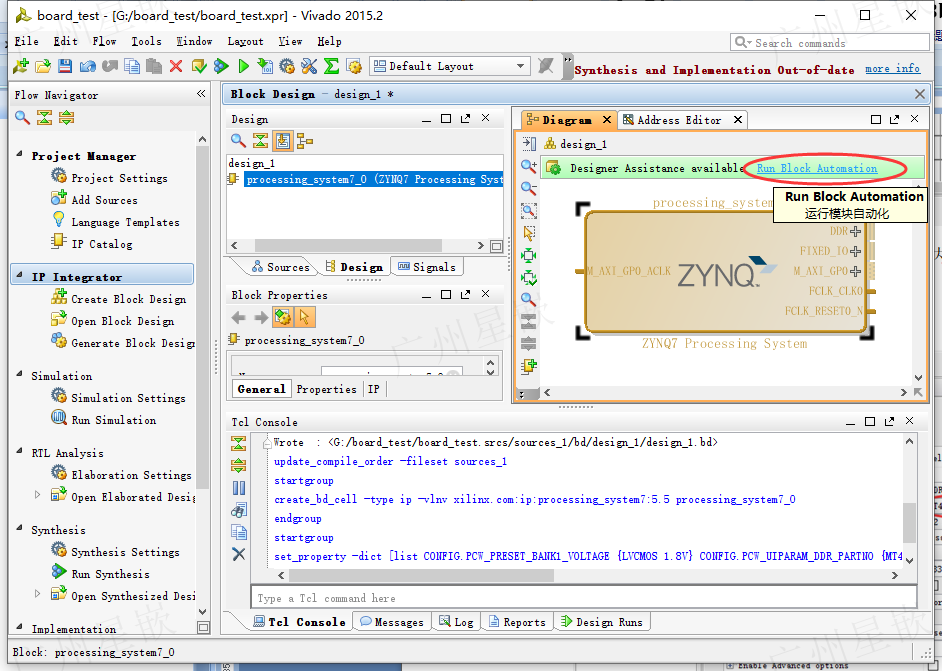

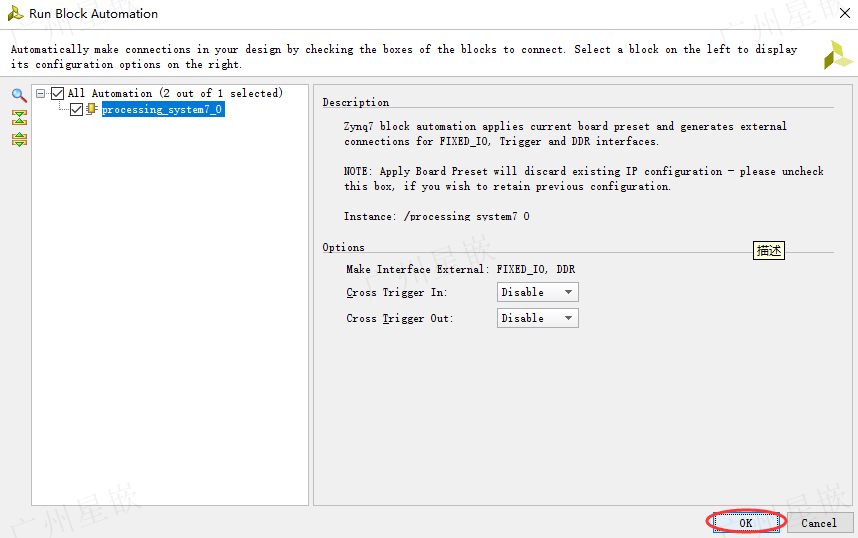

点击Run Block Automation,运行模块自动化,并在弹出的对话框中直接点击OK:

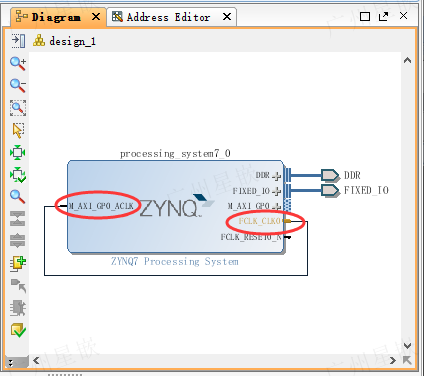

使用鼠标左键,单击FCLK_CLK0,并拖动鼠标至M_AXI_GP0_ACLK,将这两个管脚短接起来:

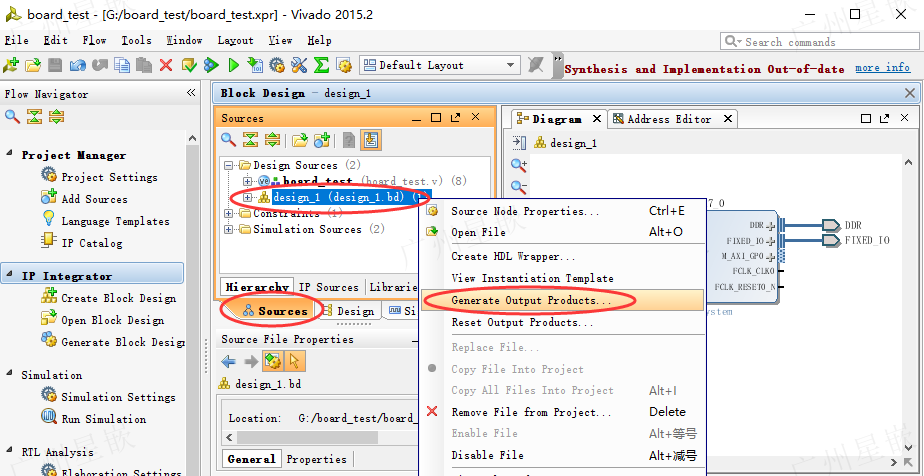

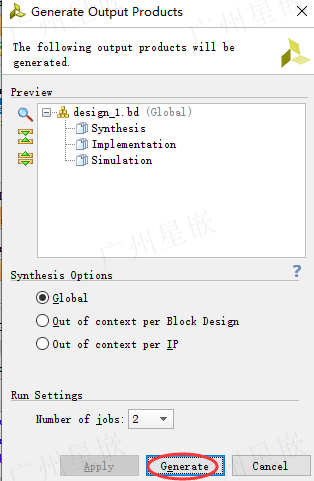

在Sources窗口,右键点击design_1.bd文件,在弹出的菜单中,选择Generate Output Products…,并在随后弹出的对话框中点击Generate:

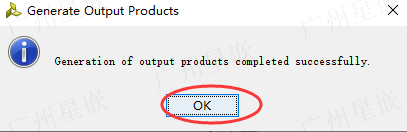

输出文件生成完毕后,点击OK:

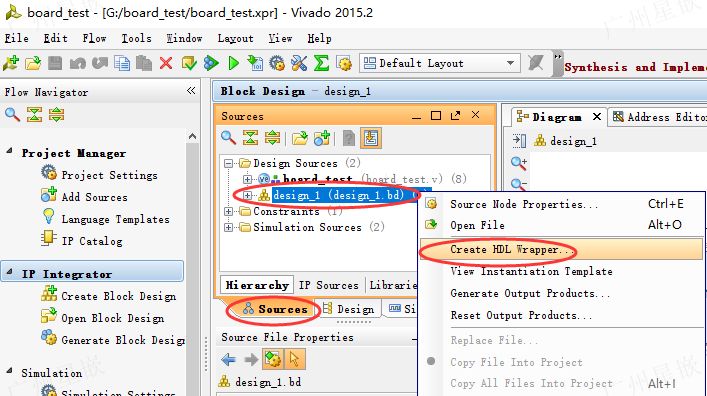

在Sources窗口,右键点击design_1.bd文件,在弹出的菜单中,选择Create HDL Wrapper…,并在随后弹出的对话框中点击Generate:

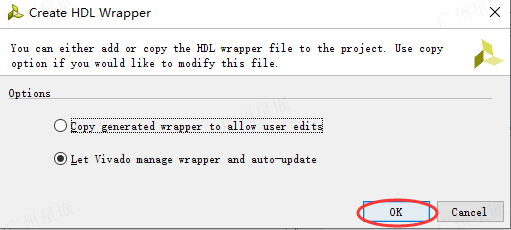

在弹出的对话框中直接点击OK:

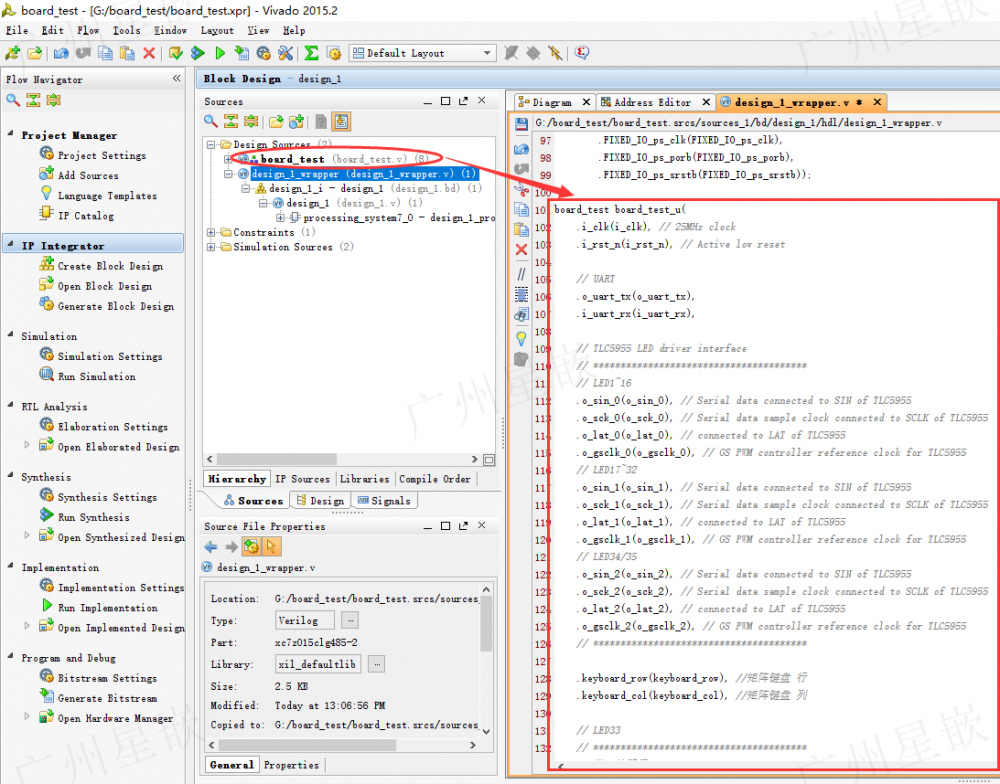

修改顶层文件

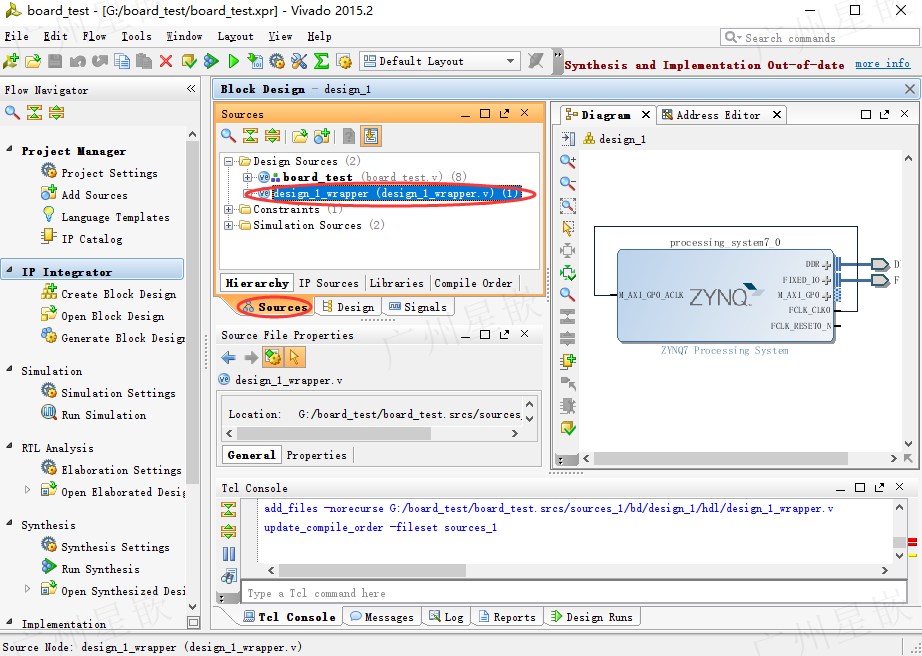

在Sources窗口,双击打开刚刚生成的design_1_wrapper.v文件:

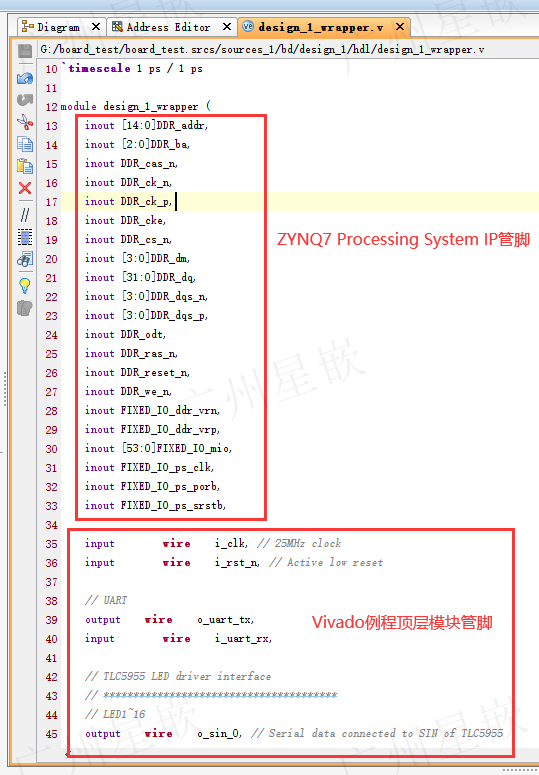

将Vivado之前的工程顶层模块例化到design_1_wrapper.v设计文件中:

整理design_1_wrapper.v模块的输入、输出管脚,并将Vivado例程顶层模块的管脚添加进来:

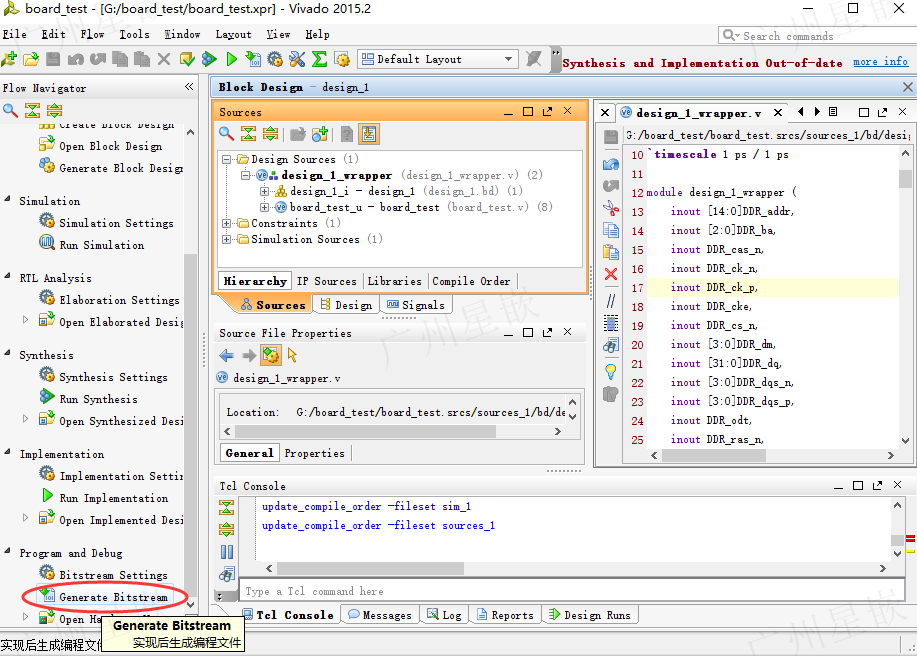

生成下载bit流文件

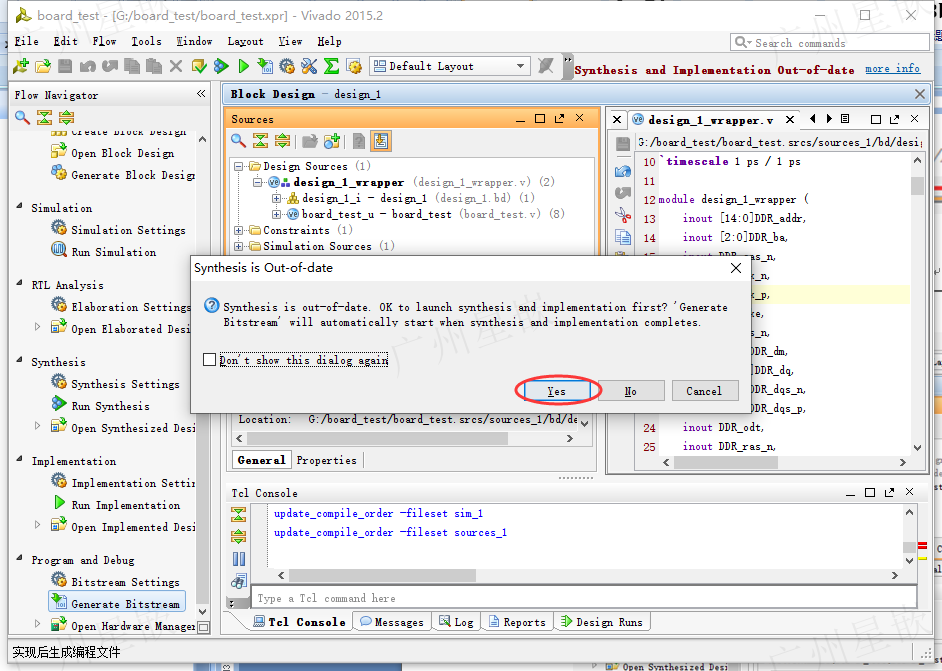

点击Generate Bitsteam,生成bit流文件,在弹出的对话框中选择Yes:

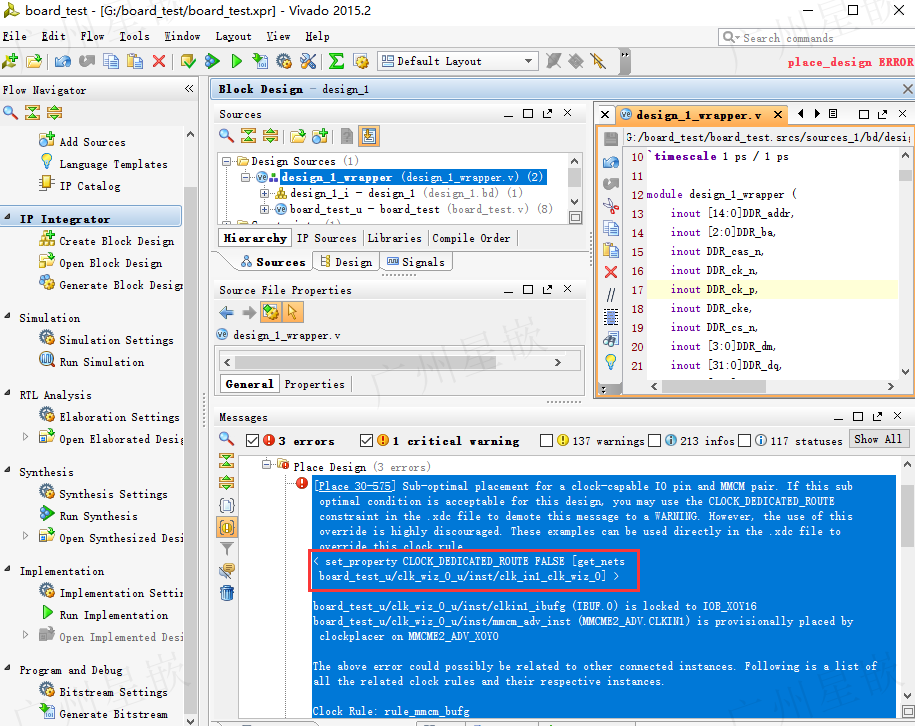

如果在生成bit流文件过程中,产生了如下错误,则按照错误提示,添加时钟约束,如下示例红框中所示,将红框里面的内容复制到约束文件中:

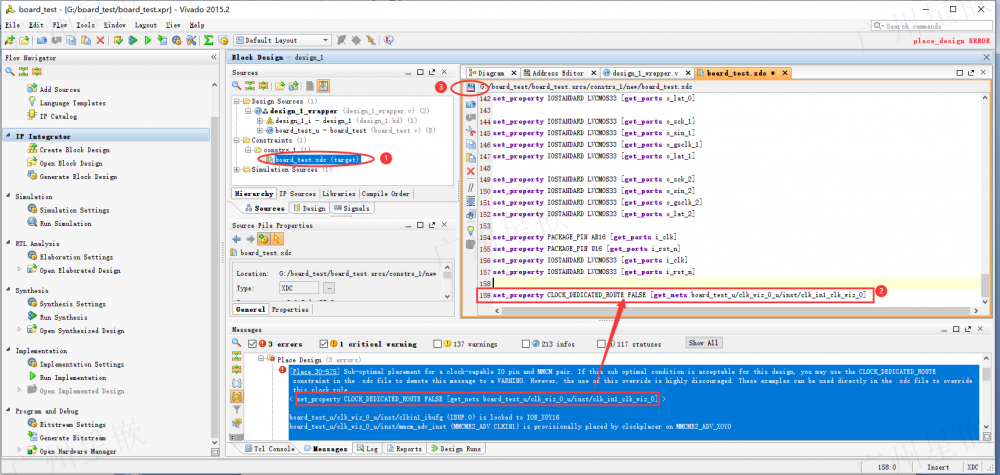

双击Constraints -> constrs_1下面的xdc约束文件,xdc约束文件打开后,将错误提示内容复制到xdc约束文件中,然后点击保存:

然后,再次点击Generate Bitsteam,生成bit流文件,在弹出的对话框中选择Yes。

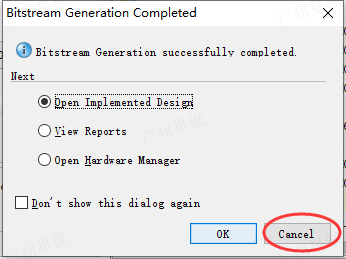

bit流文件生成完成后,在弹出的窗口中点击Cancel:

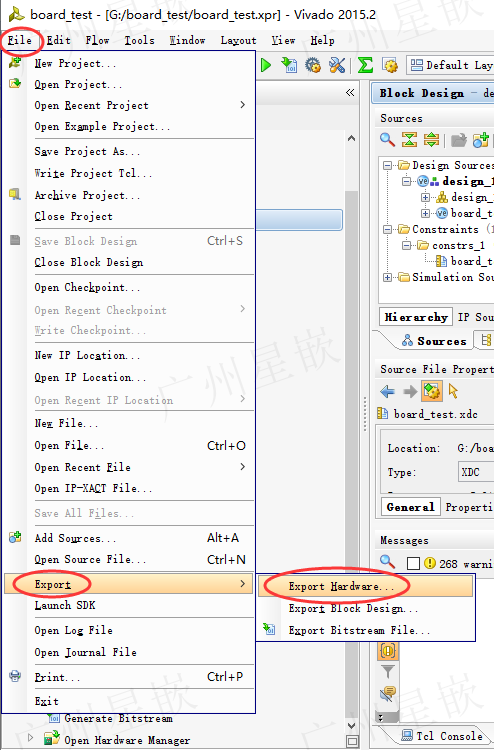

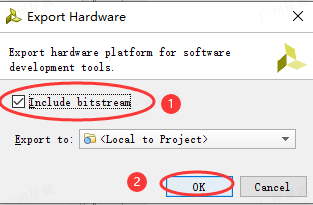

点击File -> Export -> Export Hardware…:

在弹出的对话框中,选中Include bitstream,然后点击OK:

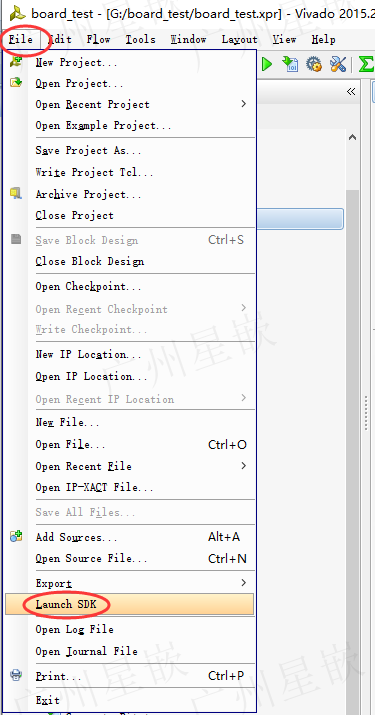

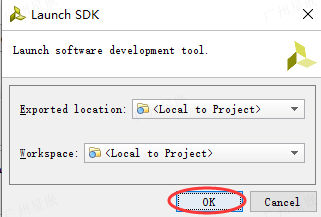

点击File -> Launch SDK,并在弹出的对话框中点击OK:

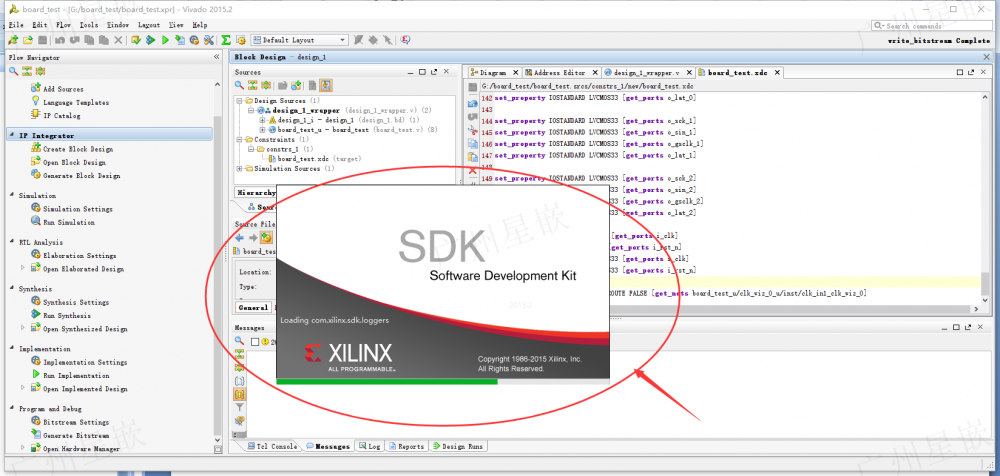

随后,SDK软件被打开:

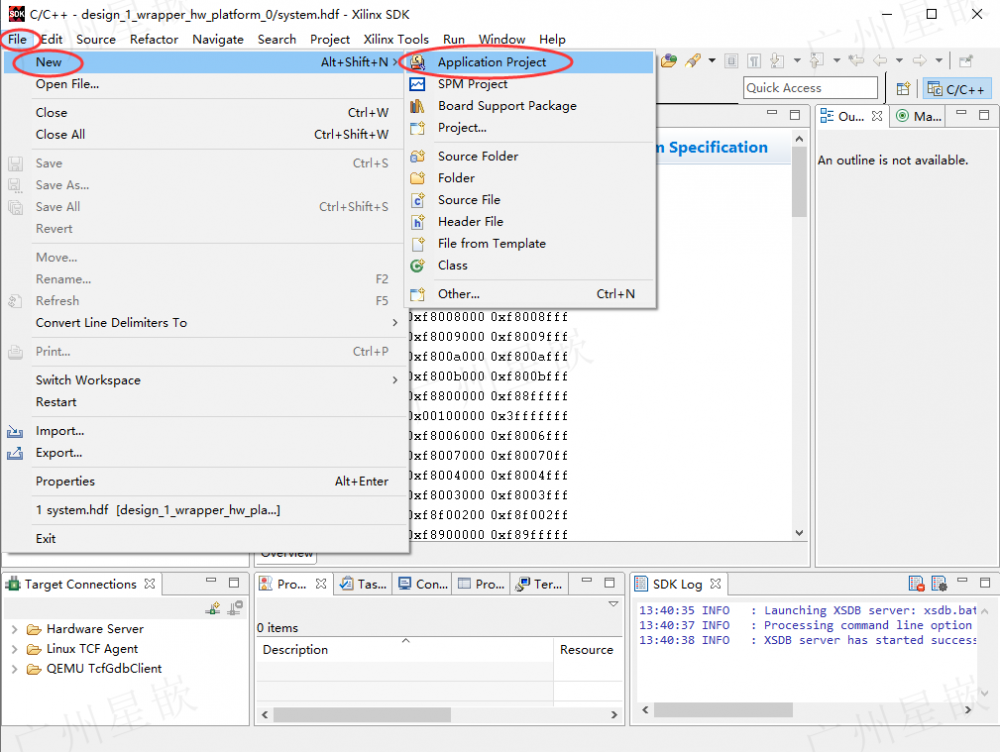

在Xilinx SDK软件界面,点击File -> New -> Application Project:

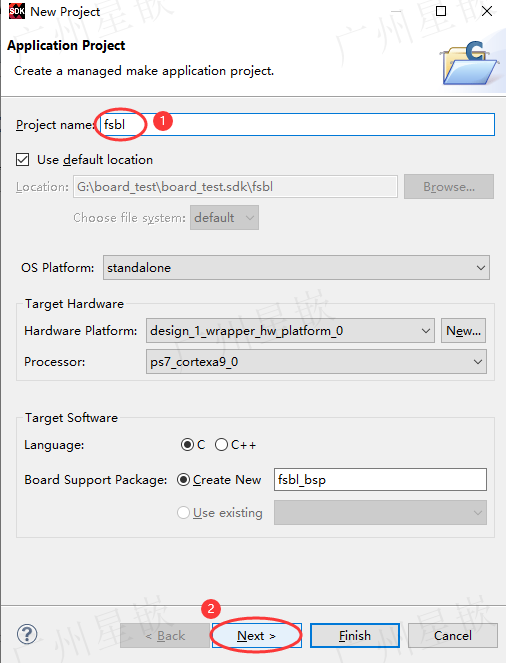

用户自定义fsbl工程名,如下示例fsbl,然后点击Next:

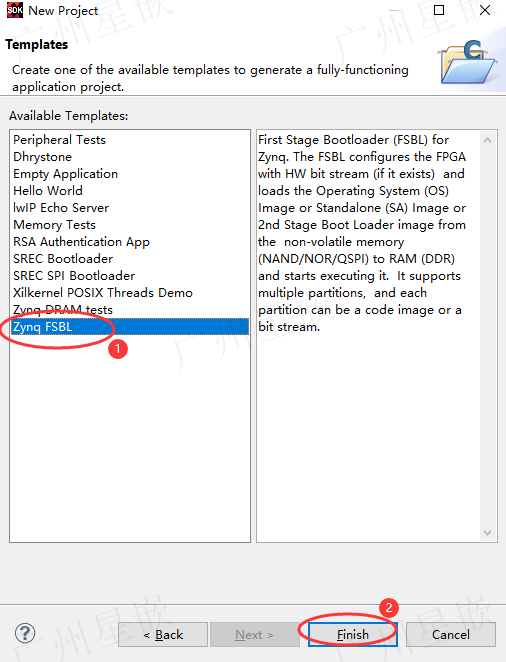

选择Zynq FSBL模板,并点击Finish:

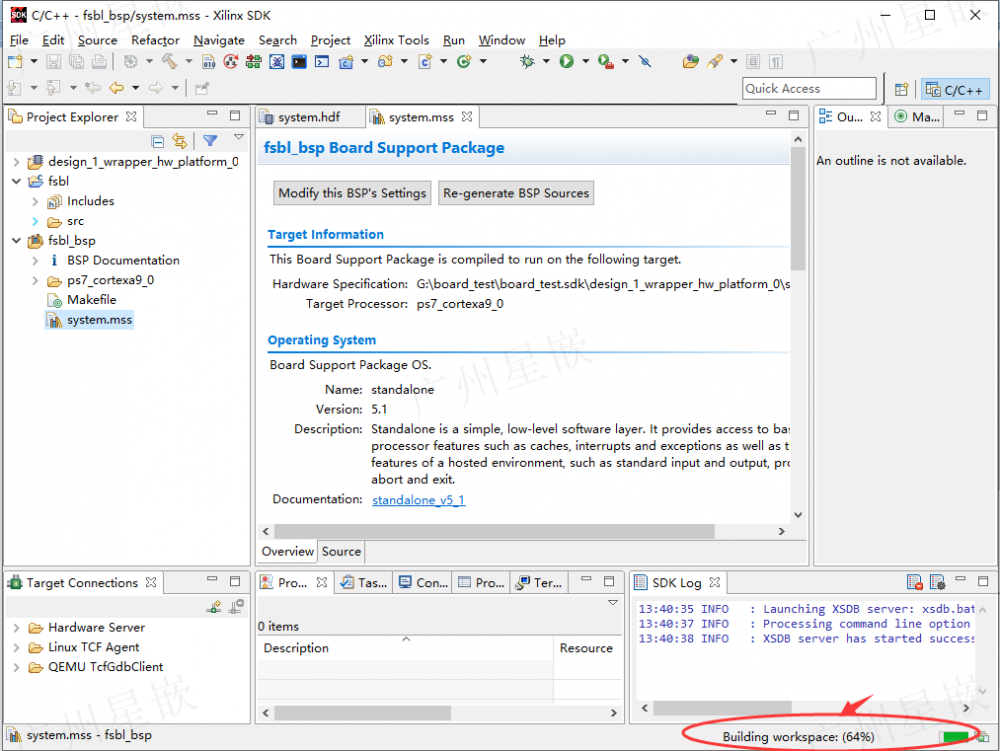

等待Build进度条完成:

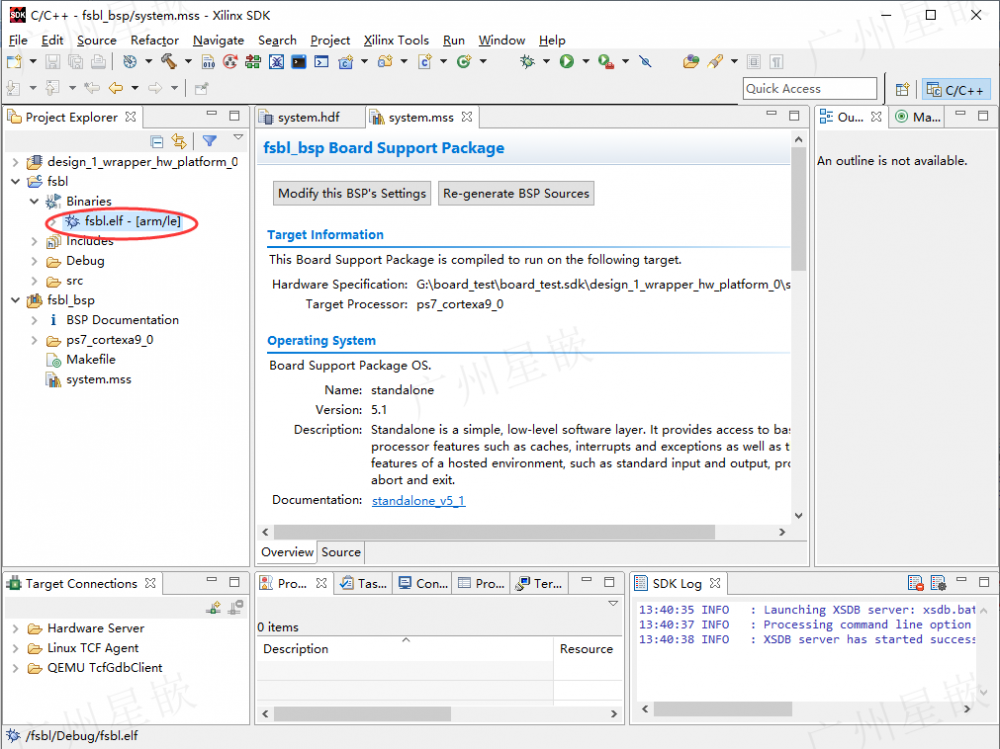

fsbl工程Build进度条完成后,在fsbl -> Binaries目录下面会生成一个fsbl.elf文件:

生成下载镜像文件BOOT.bin

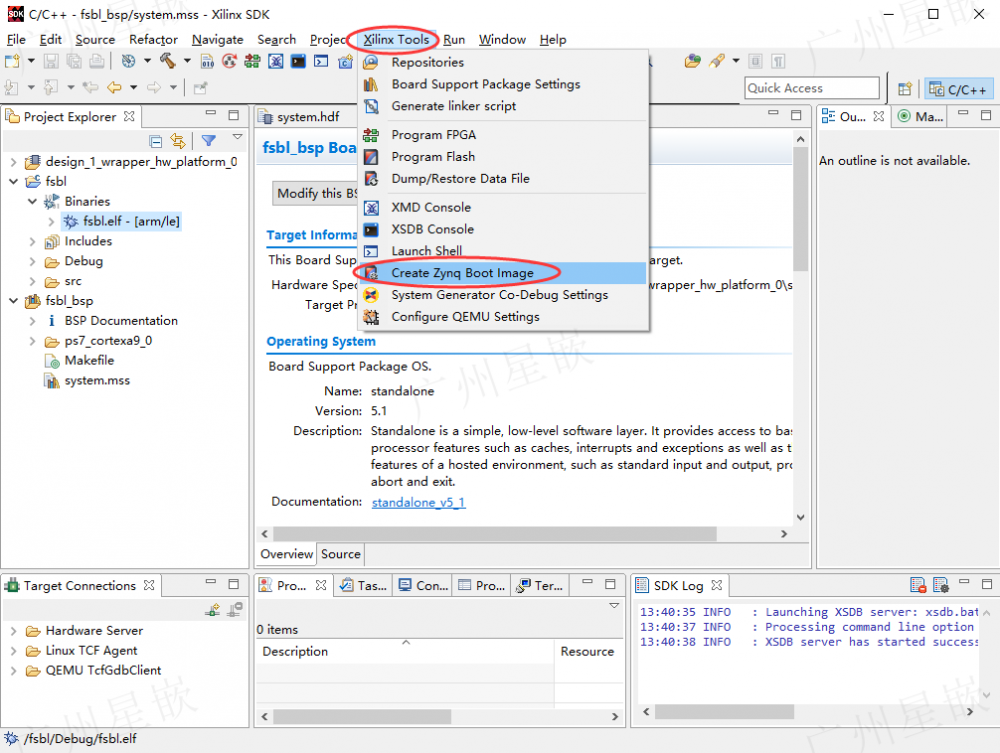

点击Xilinx Tools -> Create Zynq Boot Image:

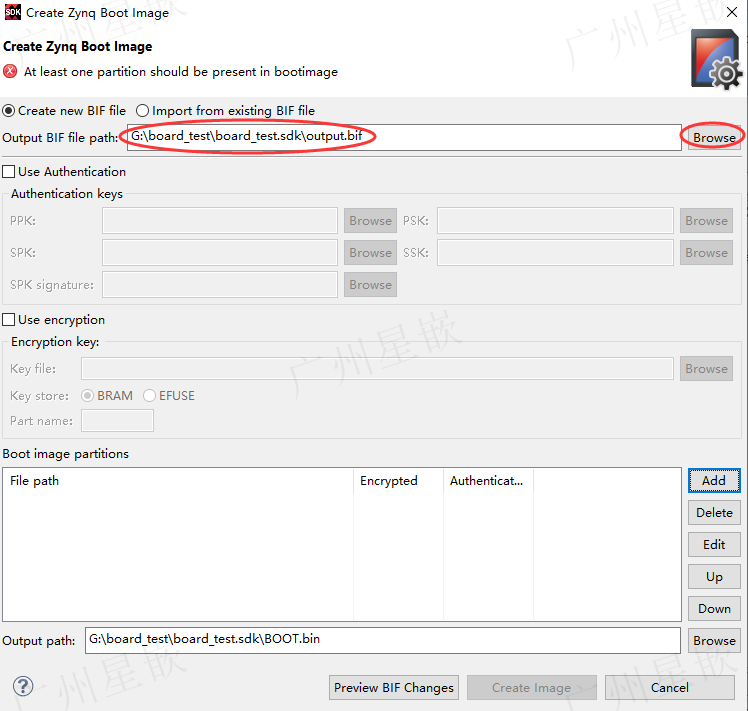

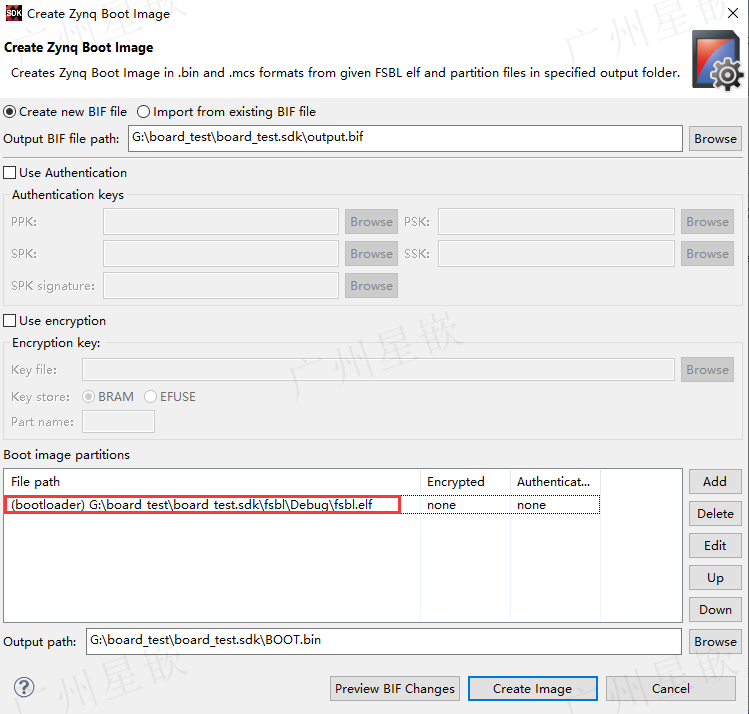

指定bif文件存放路径,用户自定义位置:

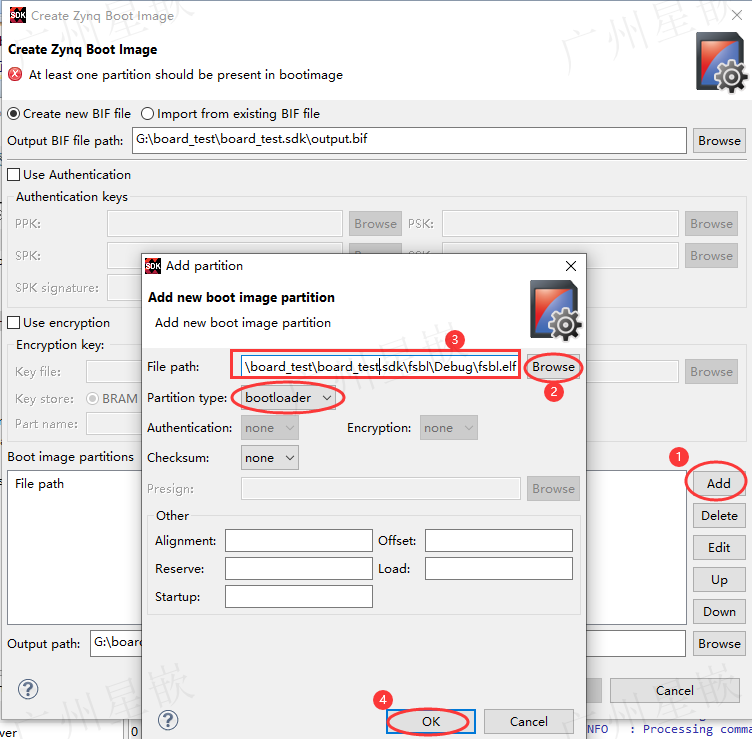

添加FSBL文件,将刚刚生成的fsbl.elf文件添加到Boot image partitions中:

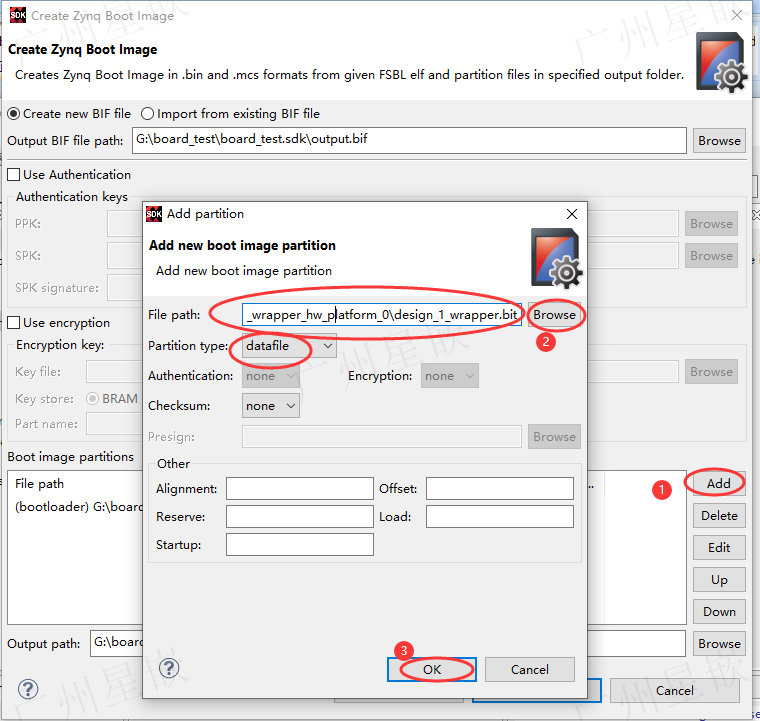

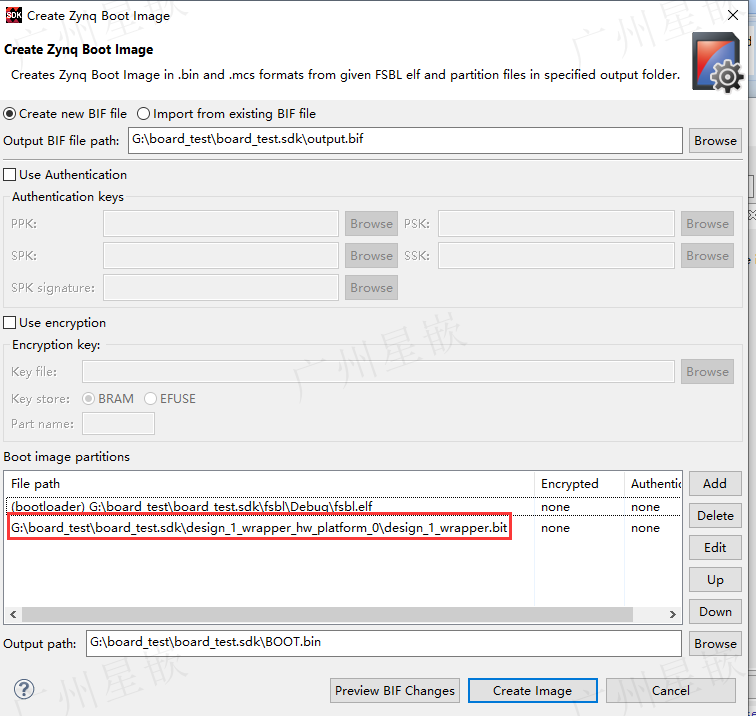

添加bit流文件,将bit流文件添加到Boot image partitions中:

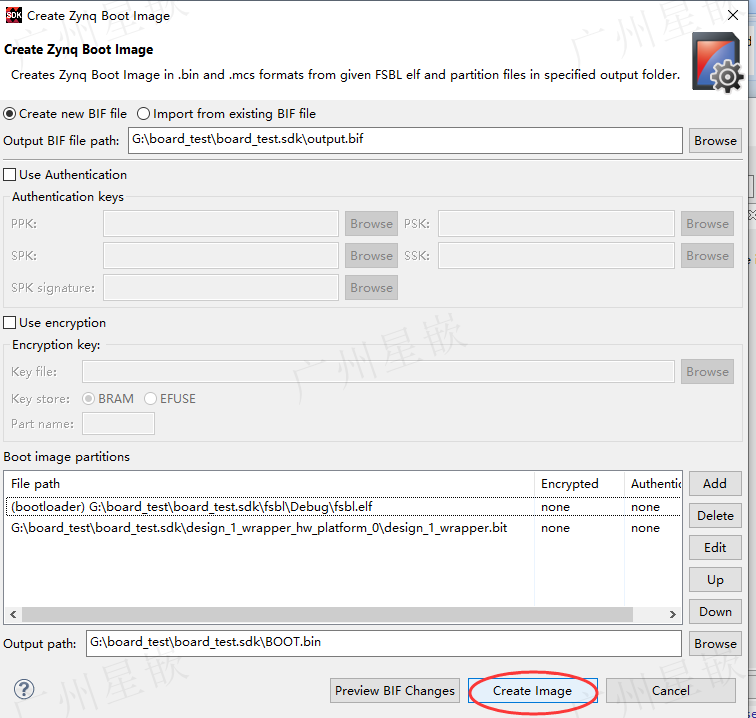

最后,点击Create Image,生成镜像文件BOOT.bin:

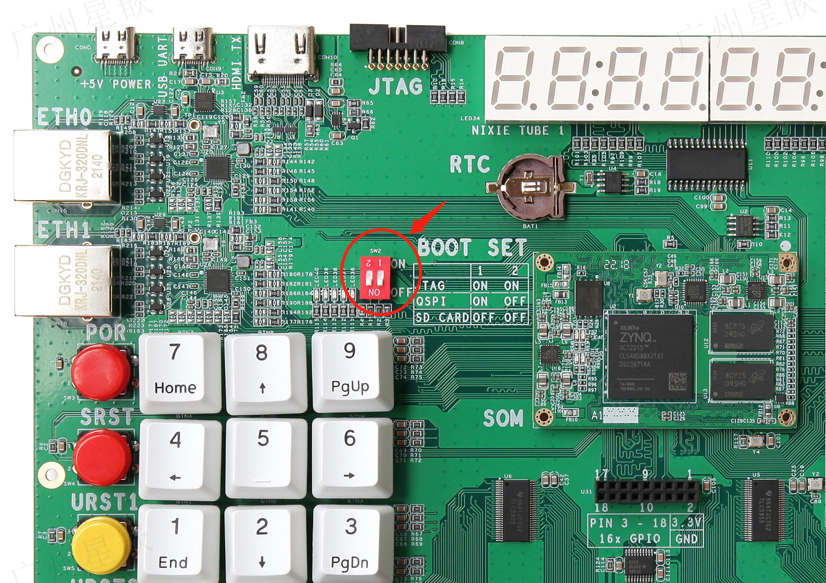

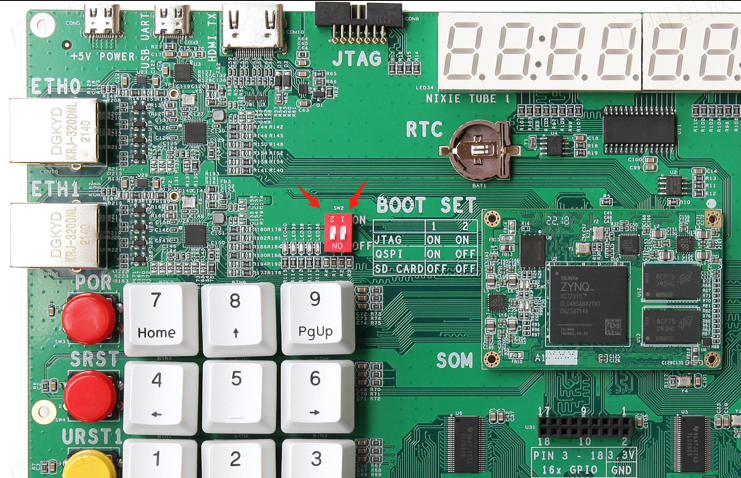

烧写FLASH前,需确保下载模式配置为JTAG模式,即开发板SW2拨码开关的2位拨码均需要拨到ON的位置,如下图红框所示:

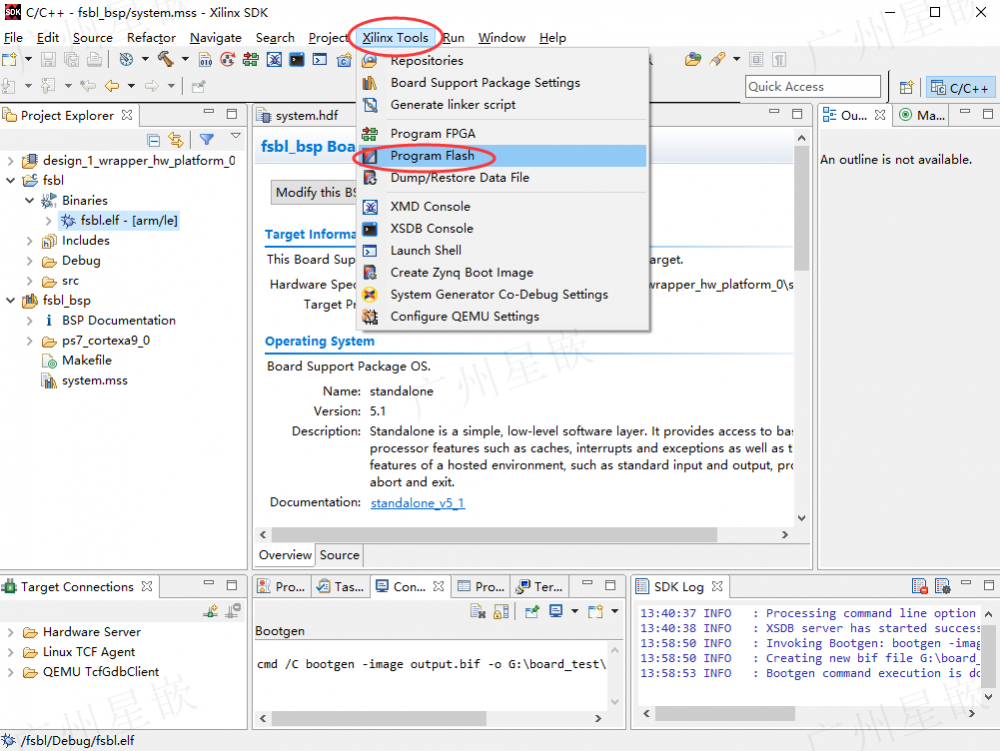

开发板上电,然后点击Xilinx Tools -> Program Flash:

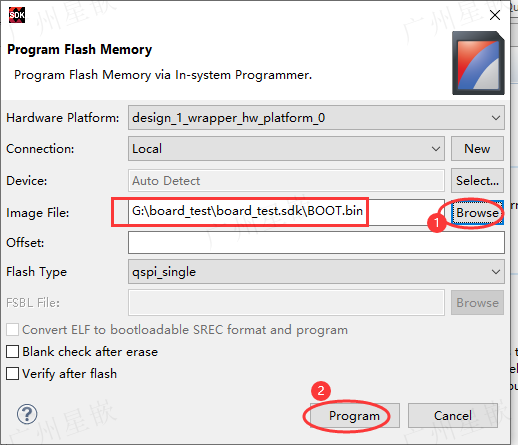

点击Browse,选择刚刚生成的镜像文件BOOT.bin,然后点击Program:

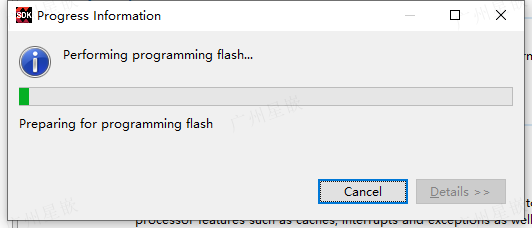

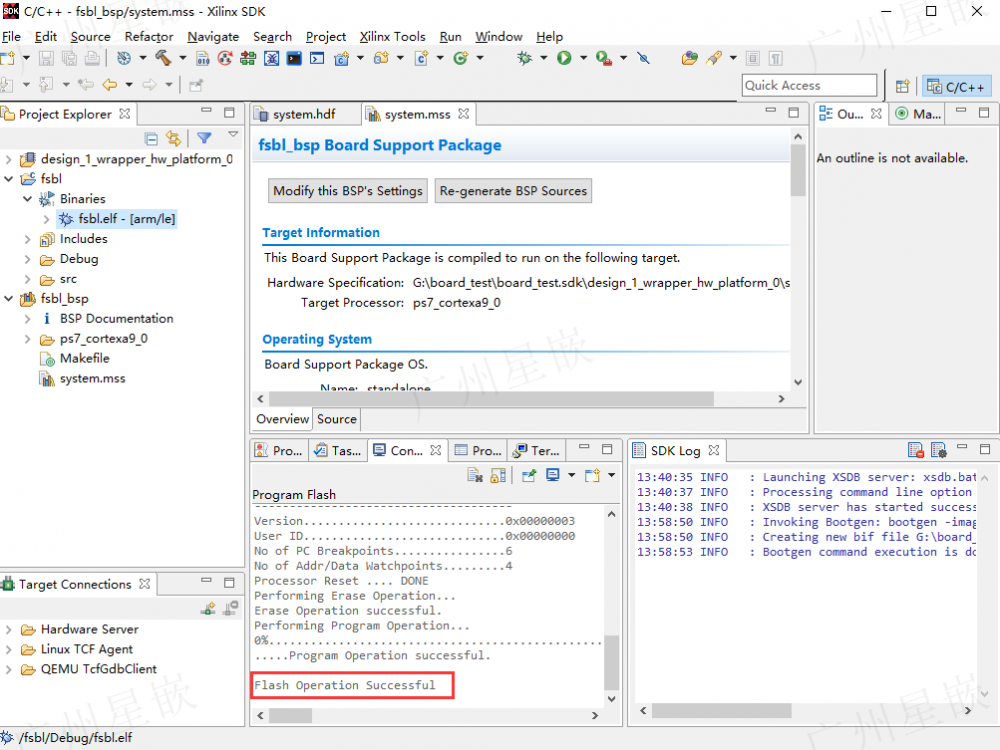

等待烧写完成:

FLASH烧写完成后,在控制台输出Flash Operation Successful信息:

程序固化检验

烧写完FLASH后,给开发板断电,并将SW2拨码开关设置为QSPI FLASH启动模式,即1号拨码位拨到ON位置,2号拨码位拨到ON的对立面,如下图红色箭头所示:

开发板上电,查看实验程序是否运行起来。