系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。

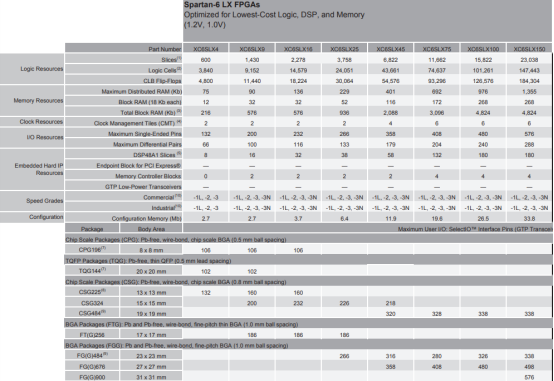

XC6SLX9系列器件采用嵌入式内存结构,用以满足设计时需要芯片上内存的需求。设计者可以配置这些内存块成为各种内存功能,如:RAM、移位寄存器、ROM和FIFO缓冲区等。

SANXIN-B02的FPGA为XC6SLX9-2TQG144C, 此款FPGA共包含216K bit的内存。

M9K的内存块支持以下特性:

1. 每一个内存块有8192个bit(包括校验的话,就是9216bit)

2. 独立的读写使能

3. 端口可配置

4. 支持单端口和双端口模式

5. 支持字节使能功能

6. 支持时钟使能功能

7. 在RAM和ROM模式下,支持初始化数据

- 设计要求

在FPGA内部构建深度为256,宽度为8的ROM。在不同的地址中放入与地址值大小相等的数据,即:0地址放0,1地址放1······

设计原理

ROM(read only memory)只读存储器,此种存储器不支持写操作,只支持读操作。在存储器建造时,将数据刻录进去。ROM能够实现掉电不丢失。

本次设计ROM是利用FPGA片内嵌入的M9K构成的,所以不能够实现掉电不丢失。

由于设计ROM深度为256,故而地址的宽度为8位。

本次构建为ROM,所以在构建ROM之前应当首先设计好初始化文件(coe文件)。

ROM工作原理为,在时钟上升沿采样到rden为1时,将addr所指示的存储空间的数据进行输出。

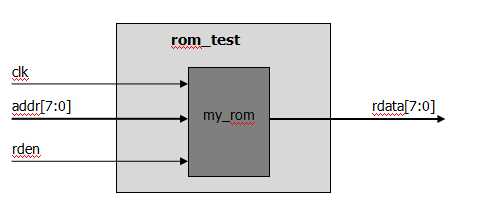

设计架构和信号说明

本模块命名为rom_test。

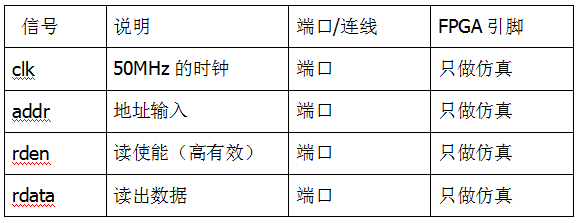

制作初始化文件

建立工程后,首先我们要生成一个coe文件,方法有很多,比如:matlab、excel表格生成数据等等。然而我们的coe文件是有一定格式的,格式如下:

memory_initialization_radix=16;

memory_initialization_vector=

第一行是规定数据的进制,如果是16进制,就在等号后面写上16,二进制就写2,其他同理。第二行是数据,在第二行下面开始把数据一个一个的写出来,数据之间用逗号隔开,最后一个数据后面加分号。

内容编写完成后,另存为.coe文件。如图:

我们这里数据从0到255,地址默认。

点击保存,coe文件就已经制作完成。

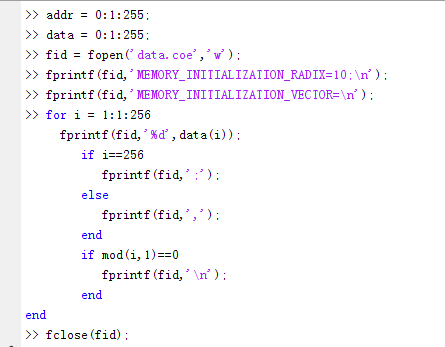

当然,如果数据很多,我们是不可能一个一个的来写的,那么我们有没有其他的方法呢,肯定是有的。下面向大家介绍一种简单的方法,那就是用MATLAB来写coe文件。

首先我们打开MATLAB,在命令窗口输入以下代码:

代码输入无误后,保存文件,会看到有一个名字为data.coe的文件生成。我们用编辑器打开,会看到我们的数据文件是没有问题的。

调用ip core之 rom

ISE工具中,调用IP核的方法跟新建文件类似,所以我们在调用IP核的时候,点击Hierarchy中的rom_test,右键选择New Source。选择文件类型为IP (CORE Generator & Architecture Wizard)。文件名为my_rom。

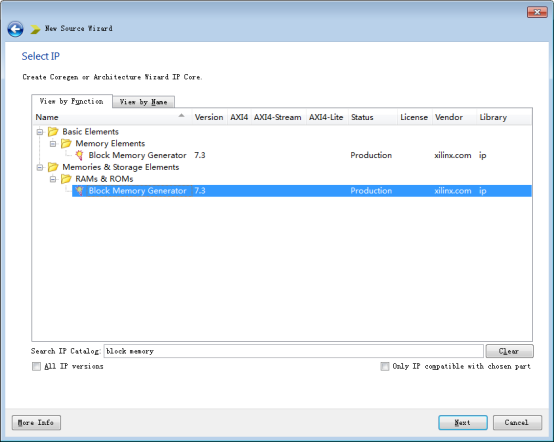

在搜索界面,搜索block memory。会看到有两个选项,我们选择RAMs & ROMs里面的Block Memory Generator7.3。点击Next。然后点击Finish。

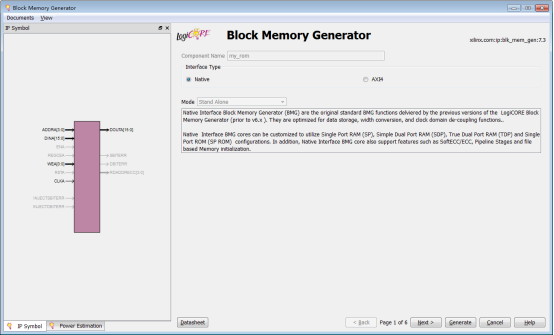

然后我们会看到如图界面,点击Next。弹出如下图示:

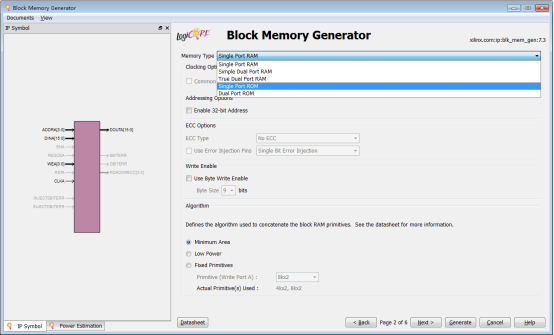

存储器类型选择单端口ROM。

ROM分为单端口(1-port)和双端口(2-port)。ROM是一个只读存储器,通过给予地址和读使能,就可以得出对应的地址的数据。在FPGA中,ROM可是配置两套端口,这两套端口相同,都可以通过给予地址和读使能,得出对应的地址的数据,并且相互独立,但是共用同一段存储空间。

在此选择ROM :1-port。点击Next

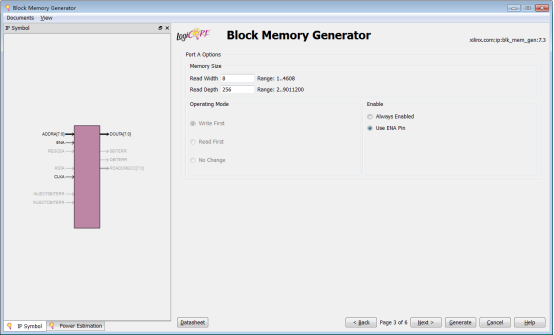

这里我们以我们之前设置的数据文件为例,数据位宽为8,数据深度为256,使能ENA打开,如图设置。点击next。

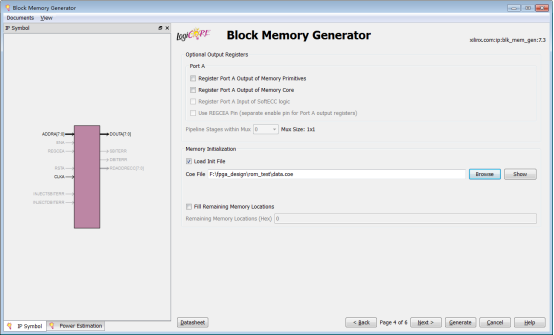

此界面为数据设置界面,因为ROM为只读存储器,所以我们需要在使用前提前配置好数据。这里就需要我们之前做好的.coe文件。在Memeory Initialization下方把Load Init File勾选上。点击Browse,找到我们的文件位置。选好之后,点击Next。

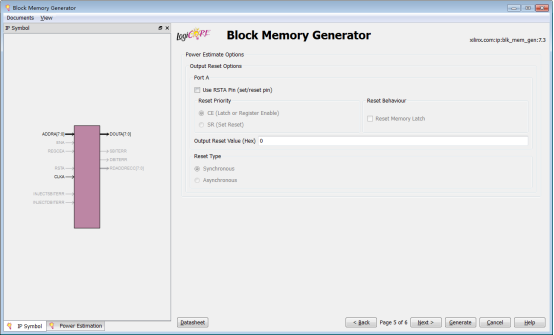

此界面是配置端口的界面,第一栏是复位端口的设置,我们这里不使用该端口,保持默认设置,点击Next。

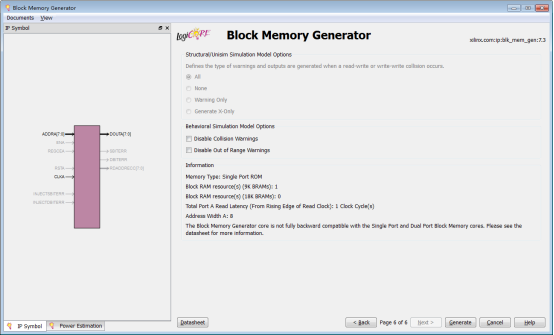

此界面保持默认设置,点击Generate。

编写设计顶层

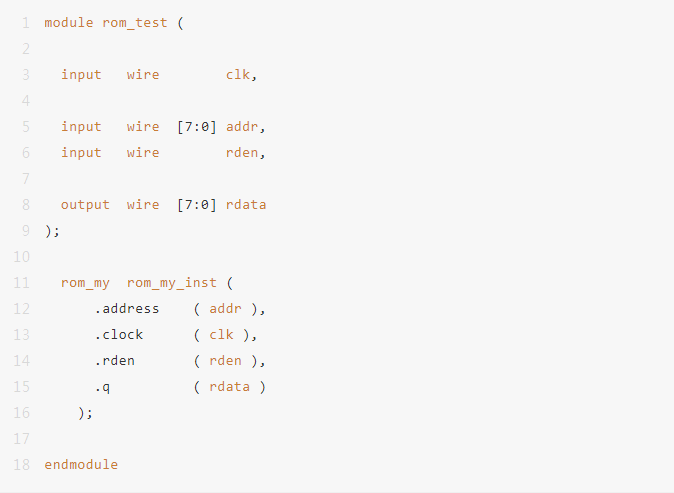

顶层模块负责例化my_rom。my_rom的例化代码在ipcore_dir -> my_rom.veo中。

设计代码为:

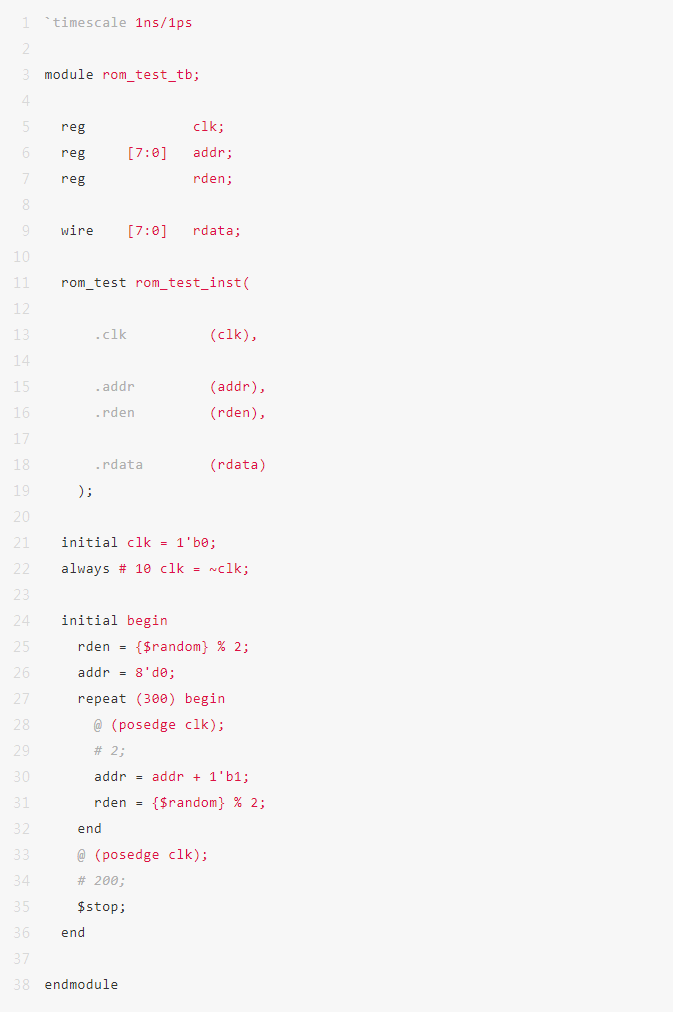

RTL仿真

设计仿真文件时,将所有的地址轮询一遍,查看输出的数据是否正确,rden信号设置为随机值,在不同的地址随机决定是否读出。

仿真代码为:

repeat语句为重复语句,相当于把begin end中间的语句重复执行N次。

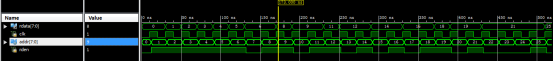

仿真编译通过后,运行仿真。

从波形图中可以看出,当rden为高电平时,rdata输出数据,当rden为低电平时,rdata不输出新数据。

将ROM设置为双端口时,addr、rden和rdata会多出一套,操作时序和方法是相同的。