module ADCNT(D,Clk,Busy,CS,ConvSTA,ConvSTB,ConvSTC,RD,Lock0,Q);

input [15:0] D;

input Clk,Busy;

output ConvSTA,ConvSTB,ConvSTC;

output RD,Lock0,CS;

output [15:0] Q;

reg [15:0] REGL;

reg ConvSTA,ConvSTB,ConvSTC;

wire CS;

wire [15:0] Q;

reg Lock,RD;

parameter st0=4'b0000,st1=4'b0001,st2=4'b0010,st3=4'b0011,st4=4'b0100,st5=4'b0101;

parameter st6=4'b0110,st7=4'b0111,st8=4'b1000,st9=4'b1001,st10=4'b1010,st11=4'b1011;

parameter st12=4'b1100,st13=4'b1101;

reg [3:0] current_states, next_states;

assign CS= 0;

assign Q= REGL;

assign Lock0= Lock;

always@(current_states or Busy)

begin

case(current_states)

st0:begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<=0;

next_states<=st1;

RD=1'b1;

case(current_states)

//st0:next_states<=st1;

st3:next_states<=st4;

st4:next_states<=st5;

st5:next_states<=st6;

st6:next_states<=st7;

st7:next_states<=st8;

st8:next_states<=st0;

//default next_states<=st1;

endcase

end

st1:begin

ConvSTA<= 1; ConvSTB<=1; ConvSTC<= 1;

Lock<= 0;

next_states<= st2;

RD<= 1;

end

st2:begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 0;

RD<= 1;

if(Busy==0)

begin

next_states<= st3;

RD<=1;

end

else

next_states<= st2;

end

st3: begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 1; next_states<= st0; RD=0;

//第1路转换结果传输

end

st4: begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 1; next_states<= st0; RD=0;//第2路转换结果传输

end

st5: begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 1; next_states<= st0; RD=0;//第3路转换结果传输

end

st6: begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 1; next_states<= st0; RD=0;//第4路转换结果传输

end

st7: begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 1; next_states<= st0; RD=0;//第5路转换结果传输

end

st8: begin

ConvSTA<= 0; ConvSTB<= 0; ConvSTC<=0;

Lock<= 1; next_states<= st0; RD=0;//第6路转换结果传输

end

default:begin

next_states<= st0;

end

endcase

end

always@(posedge Clk)

begin

current_states<= next_states;

end

always@(posedge Lock)

begin

REGL <= D;

end

endmodule

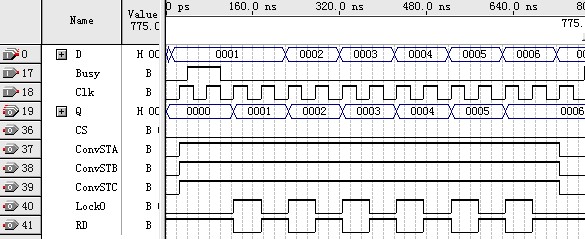

想把AD7656输入的D传到REGL中,AD7656传输6路数据,现在是无法正确传输数据,下面是AD7656的时序图

实际的仿真结果如下,现在出现问题是两个CONVSTX间隔中只有一个RD低电平,且传输的数据时序也不对。

还请大家帮忙看看?谢谢

我要赚赏金

我要赚赏金