各位朋友大家好,小弟正自学CPLD。

学习中遇到了不少困难,下面的疑问还请各位帮忙解答。

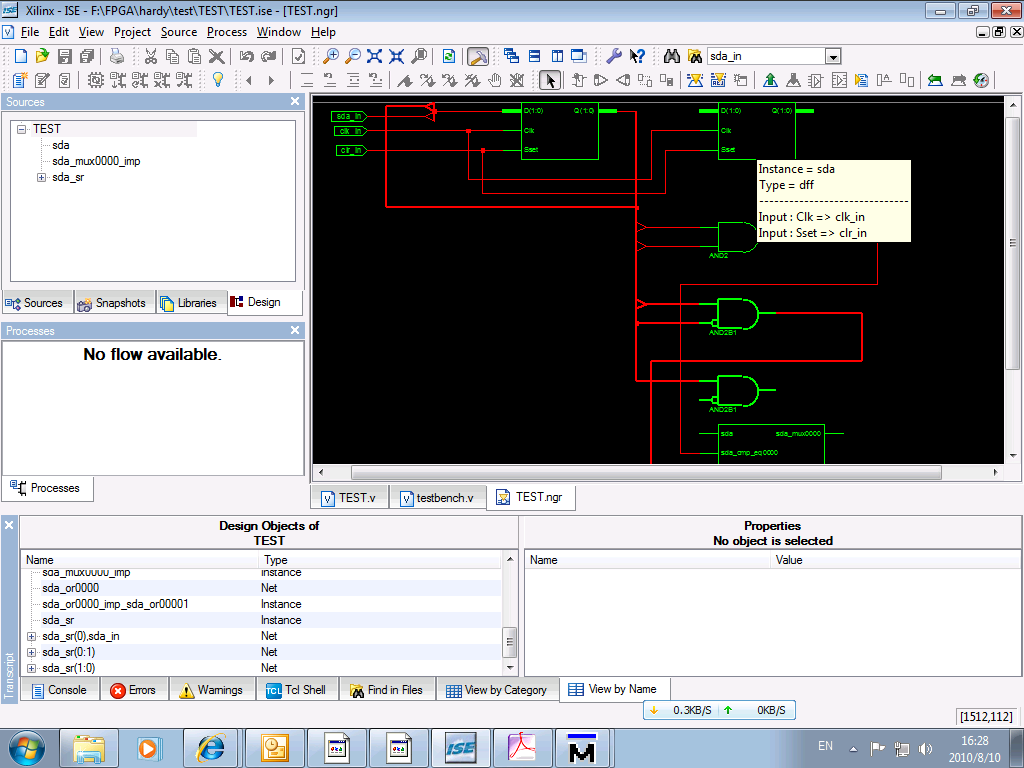

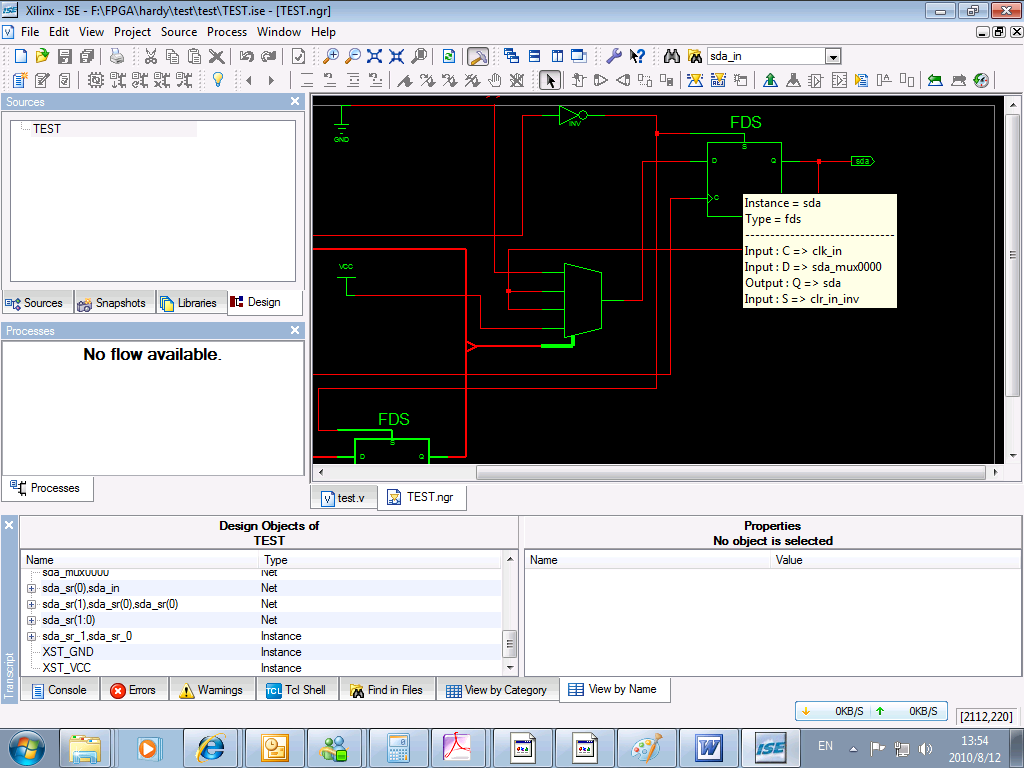

如下代码所示,我用modelsim仿真发现是正常的,sda可以正常的根据sda_in的输入而变化,但我看到xst综合后底层的元件,发现并没有wire连给sda输出,只有一个instance=sda,且D端无输入,且Q端并无输出。请大位大虾帮忙,可能大家稍微指点可解我心头之郁闷

谢谢

`timescale 1ns / 1ps

module TEST(clk_in,sda_in,clr_in,sda);

input clk_in,sda_in,clr_in;

output sda;

reg sda;

reg [1:0] sda_sr;

always @ (posedge clk_in)// or posedge clr_in)

if (!clr_in)

begin

sda_sr [1:0] <= 2'b11; // Start up assuming quiescent state of inputs

sda <= 1;

end

else

begin

sda_sr <= {sda_sr[0],sda_in};

if (sda_sr == 2'b00) sda <= 0;

else if (sda_sr == 2'b11) sda <= 1;

end

endmodule

共7条

1/1 1 跳转至页

合仿真疑惑

关键词: 仿真 疑惑

共7条

1/1 1 跳转至页

我要赚赏金

我要赚赏金