看看。。。。

本来是显示字符的:CHA(通道A)

突然又觉得好歹也是VGA啊,你不能把这么个大液晶屏当12806使吧,,怎么着都得显示个图片出来吧~~~~说干就干

拿张PLMM的壁纸,

在网上下了个图片转MIF的软件,坑爹的,没有转256色格式的功能,只有256灰度的,好吧,黑白电视机的画面还是蛮怀念的,计算了一下,EP2C5有36(好像是36,反正不会多于36)个M4K,4*1024*36bit,真可怜,存储一个满屏的画面都不行,最后敲定128*100像素的照片,直接转成MIF,效果如下,,真坑爹,,,

金泫雅妹纸,,你怎么了,你百变大咖啊!你这让那个我情何以堪!!!哎~~~~~~~估计是现在的液晶显示器不只是灰度显示了,于是只好用其他的软件先把图片转换成.c,然后在把它编辑成.hex的,,于是真的就显示出来了。。。

实在是小,,,进一点

SOF,POF文件下载:

——回复可见内容——

verilog在楼下的楼下

verilog程序:

module vga

#(

//------------水平扫描常量--------------

parameter LinePeriod = 12'd1040,

parameter H_SyncPulse = 10'd120,

parameter H_BackPorch = 10'd61,

parameter H_ActivePix = 10'd806,

//------------垂直扫描常量--------------

parameter FramePeriod = 12'd666,

parameter V_SyncPulse = 10'd6,

parameter V_BackPorch = 10'd21,

parameter V_ActivePix = 10'd604

)

(

input clk,

input rst,

output H_Sync,

output V_Sync,

output [2:0] VGA_R,

output [2:0] VGA_G,

output [1:0] VGA_B

);

//-----------------水平扫描计数-----------------

reg[11:0] X_cnt;

always @(posedge clk or negedge rst) begin

if(!rst)

X_cnt <= 12'b1;

else if(X_cnt == LinePeriod) X_cnt <= 12'b1;

else X_cnt <= X_cnt + 1'b1;

end

//-------------水平扫描信号HSYNC计产生-------------

reg H_Sync_r;

always @(posedge clk or negedge rst) begin

if(!rst) H_Sync_r <= 1'b1;

else if(X_cnt == 12'b1) H_Sync_r <= 1'b0;

else if(X_cnt >= H_SyncPulse) H_Sync_r <= 1'b1;

end

assign H_Sync = H_Sync_r;

//-----------------垂直扫描计数-----------------

reg[11:0] Y_cnt;

always @(posedge clk or negedge rst) begin

if(!rst) Y_cnt <= 12'b1;

else if(Y_cnt == FramePeriod) Y_cnt <= 12'b1;

else if(X_cnt == LinePeriod) Y_cnt <= Y_cnt + 1'b1; //水平扫描完后垂直

end

//-------------垂直扫描信号VSYNC计产生-------------

reg V_Sync_r;

always @(posedge clk or negedge rst) begin

if(!rst) V_Sync_r <= 1'b1;

else if(Y_cnt == 12'b1) V_Sync_r <= 1'b0;

else if(Y_cnt >= V_SyncPulse) V_Sync_r <= 1'b1;

end

assign V_Sync = V_Sync_r;

//----------------有效显示区标志-------------------

wire valid;

assign valid = (X_cnt>=(H_SyncPulse+H_BackPorch))&&(X_cnt<(H_SyncPulse+H_BackPorch+H_ActivePix))&&

(Y_cnt>=(V_SyncPulse+V_BackPorch))&&(Y_cnt<(V_SyncPulse+V_BackPorch+V_ActivePix));

wire[9:0] x_dis;

wire[9:0] y_dis;

assign x_dis = X_cnt - (H_SyncPulse + H_BackPorch );

assign y_dis = Y_cnt - (V_SyncPulse + V_BackPorch );

/**************VGA色彩信号产生***************

RGB = 000 黑色 RGB = 100 红色

= 001 蓝色 = 101 紫色

= 010 绿色 = 110 黄色

= 011 青色 = 111 白色

*******************************************/

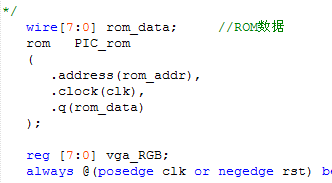

reg[15:0] rom_addr; //ROM地址

wire[7:0] rom_data; //ROM数据

rom PIC_rom

(

.address(rom_addr),

.clock(clk),

.q(rom_data)

);

reg [7:0] vga_RGB;

always @(posedge clk or negedge rst) begin

if(!rst)

begin

vga_RGB <= 8'b0;

rom_addr <= 16'b0;

end

else if(valid)

begin

if((x_dis >= 10'd336 && x_dis < 10'd464) && (y_dis >= 10'd250 && y_dis < 10'd350))

begin

vga_RGB <= rom_data;

rom_addr <= rom_addr + 1'b1;

if(rom_addr == 12799) rom_addr <= 16'b0;

end

else vga_RGB <= 8'b000_001_11;

end

else vga_RGB <= 8'b0;

end

assign VGA_R = vga_RGB[7:5];

assign VGA_G = vga_RGB[4:2];

assign VGA_B = vga_RGB[1:0];

endmodule

(首先做这个实验你焊接的晶振应该是Y2)

Cyclone II器件中最多有四个锁相环Cyclone II 的PLL功能强大,可以用作零延时缓存器、频率合成器、抖动衰减器、一个低斜扇出缓冲器,支持时钟转换、可编程切换、可编程占空比,减少时钟延时、时钟偏斜。

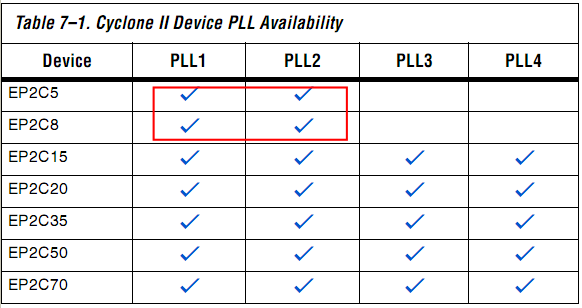

器件中的可用PLLs个数

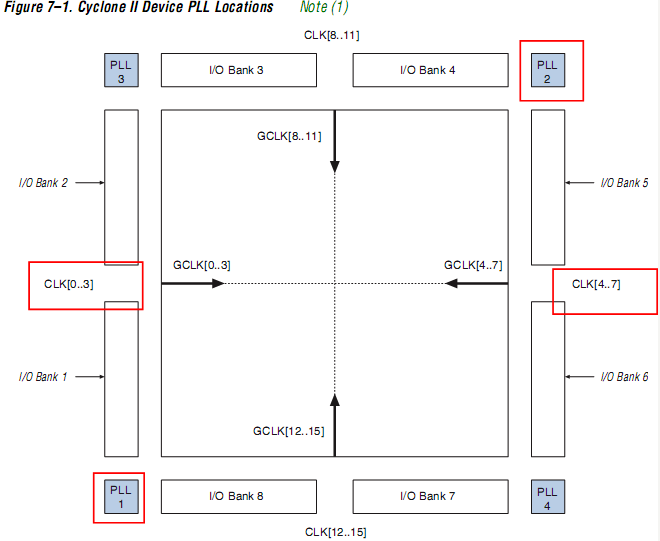

Cyclone II器件中PLL的位置

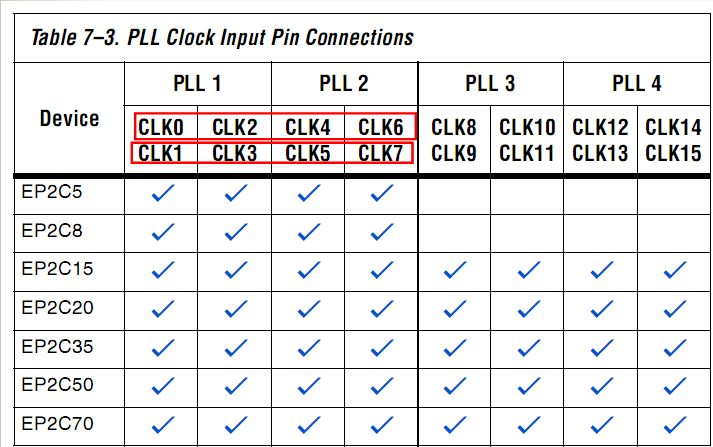

EP2C5和EP2C8只有8个全局时钟和两个PLL,如上图红色所标出的。

PLL的参考时钟

在Cyclone II器件中,多达四个管脚可以驱动PLL,PLL具有内部延时块可以补偿从输入到PLL的延时。每个PLL的输入可以由四个单端输入和两个差分输入时钟输入来供给。

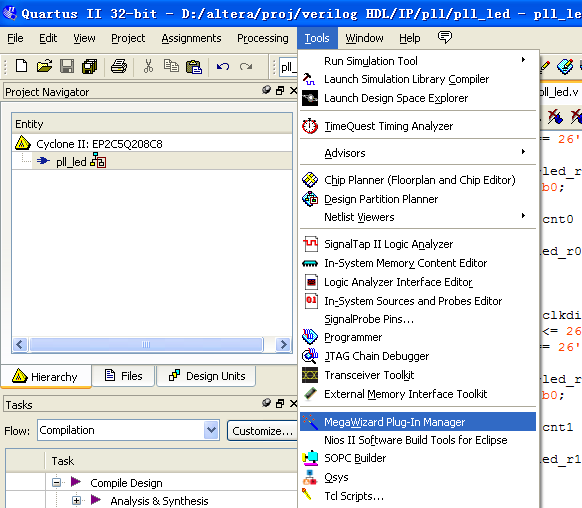

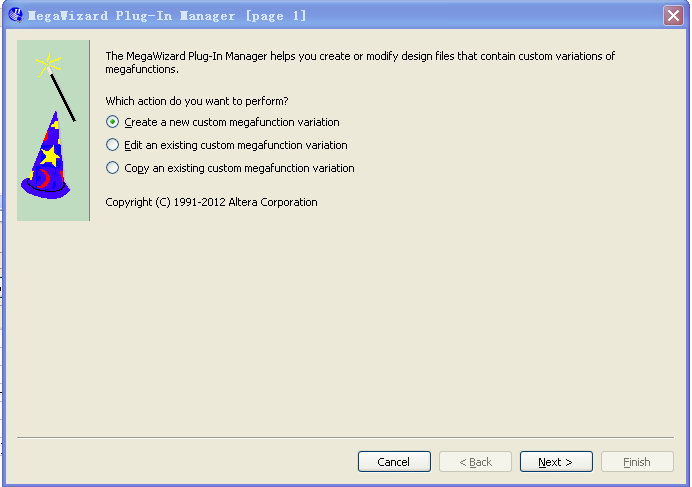

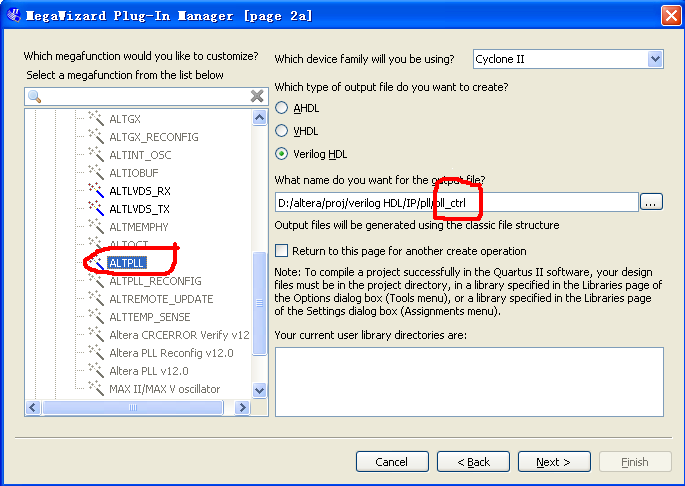

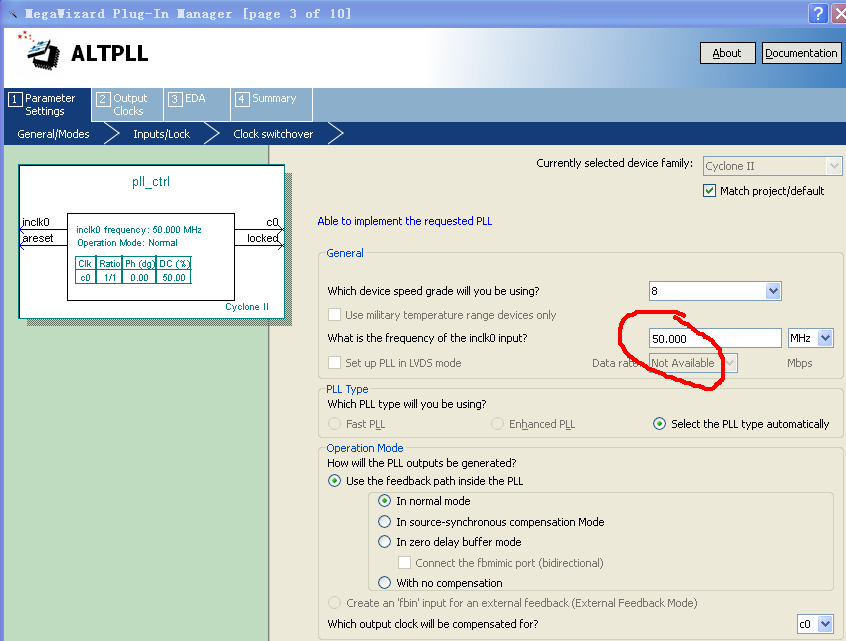

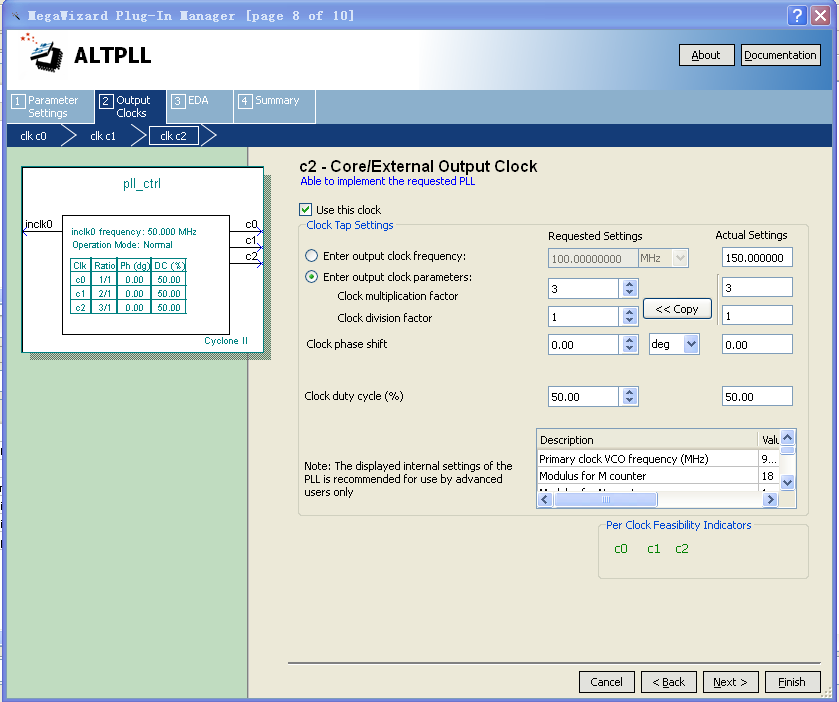

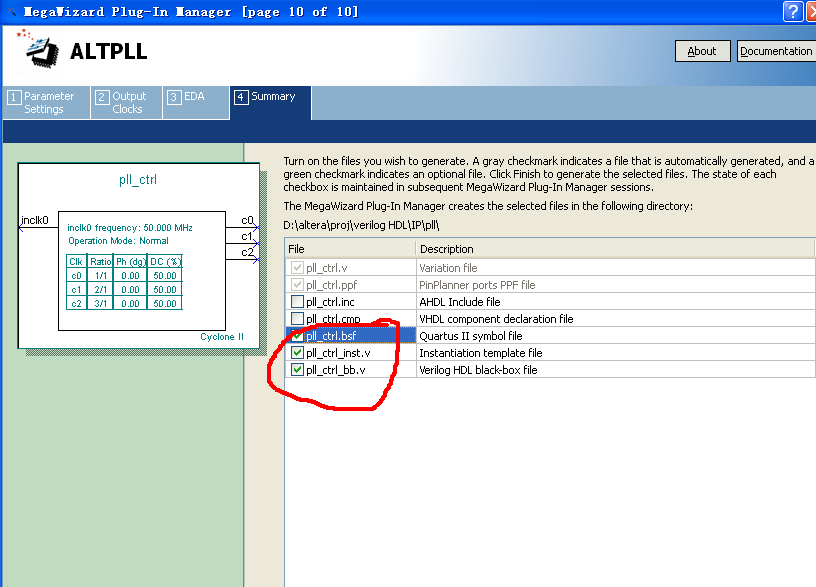

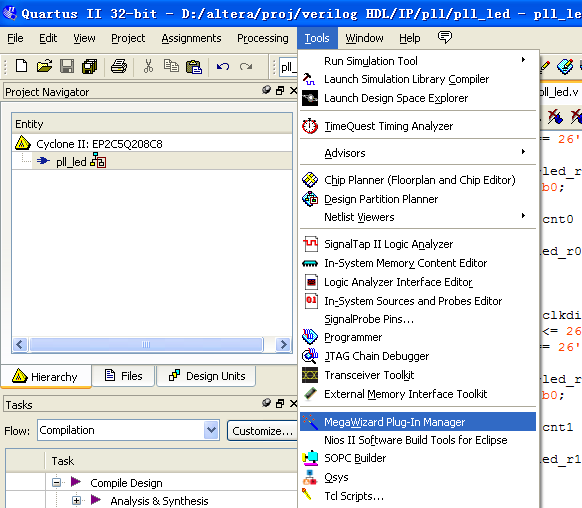

下面是PLL核添加过程:

到这一步,PLL算是添加完了,c0输出50Mhz、c1输出100Mhz、c2输出150Mhz的时钟信号。接下来是调用了。

verilog程序:

module pll_led(clk,clk2, rst, led);

input clk;

input clk2;

input rst;

output [4:0] led;

wire clkdiv0;

wire clkdiv1;

wire clkdiv2;

pll_ctrl PLL_DIV

(

.inclk0(clk),

.c0(clkdiv0),

.c1(clkdiv1),

.c2(clkdiv2)

);

wire clkdiv3;

wire clkdiv4;

wire clkdiv5;

pll_ctrl2 PLL_DIV2

(

.inclk0(clk2),

.c0(clkdiv3),

.c1(clkdiv4),

.c2(clkdiv5)

);

reg [25:0] cnt0;

reg led_r0;

always @(posedge clk or negedge rst) begin

if(!rst) cnt0 <= 26'b0;

else if(cnt0 == 26'd25_000_000)

begin

led_r0 <= ~led_r0;

cnt0 <= 26'b0;

end

else cnt0 <= cnt0 + 1'b1;

end

assign led[0] = led_r0;

reg [25:0] cnt1;

reg led_r1;

always @(posedge clkdiv0 or negedge rst) begin

if(!rst) cnt1 <= 26'b0;

else if(cnt1 == 26'd25_000_000)

begin

led_r1 <= ~led_r1;

cnt1 <= 26'b0;

end

else cnt1 <= cnt1 + 1'b1;

end

assign led[1] = led_r1;

reg [25:0] cnt2;

reg led_r2;

always @(posedge clkdiv1 or negedge rst) begin

if(!rst) cnt2 <= 26'b0;

else if(cnt2 == 26'd25_000_000)

begin

led_r2 <= ~led_r2;

cnt2 <= 26'b0;

end

else cnt2 <= cnt2 + 1'b1;

end

assign led[2] = led_r2;

reg [25:0] cnt3;

reg led_r3;

always @(posedge clkdiv2 or negedge rst) begin

if(!rst) cnt3 <= 26'b0;

else if(cnt3 == 26'd25_000_000)

begin

led_r3 <= ~led_r3;

cnt3 <= 26'b0;

end

else cnt3 <= cnt3 + 1'b1;

end

assign led[3] = led_r3;

reg [25:0] cnt4;

reg led_r4;

always @(posedge clkdiv3 or negedge rst) begin

if(!rst) cnt4 <= 26'b0;

else if(cnt4 == 26'd25_000_000)

begin

led_r4 <= ~led_r4;

cnt4 <= 26'b0;

end

else cnt4 <= cnt4 + 1'b1;

end

assign led[4] = led_r4;

endmodule

观察LED灯的闪烁频率。

说明:调用了两个PLL,我们的板子上的晶振输入FPGA的引脚是CLK2(Y2)和CLK7(Y1),是要中只有接入Y2晶振的PLL模块才有效。你可以分配引脚试试。

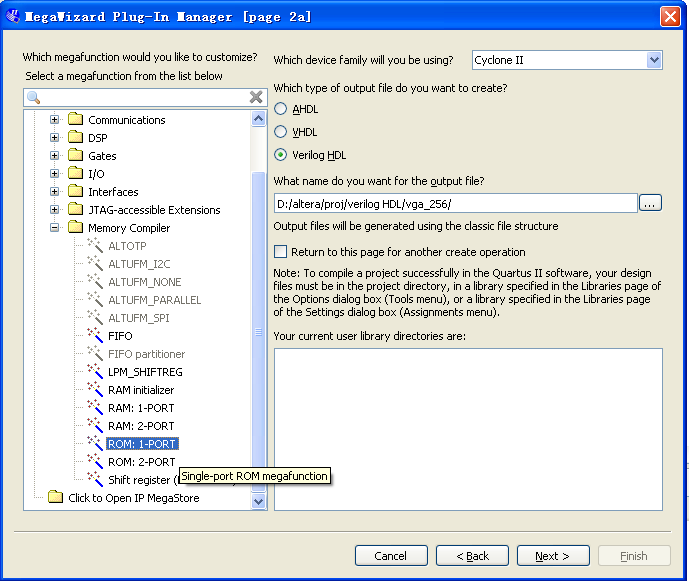

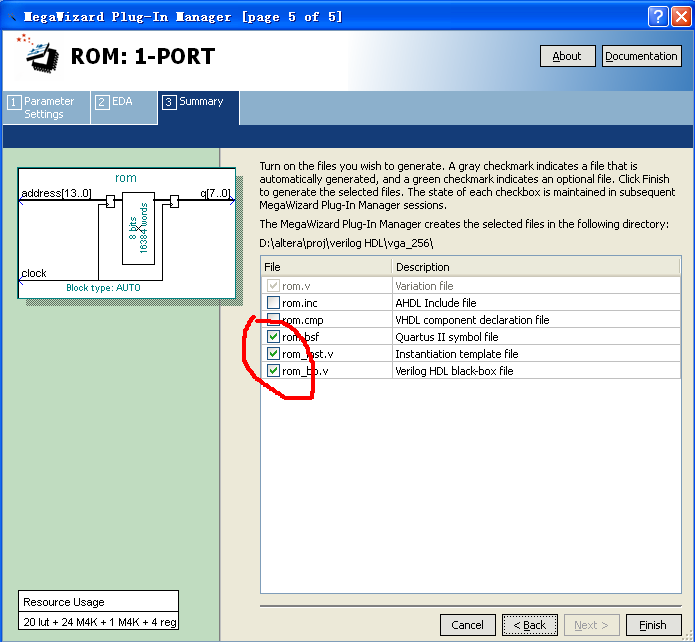

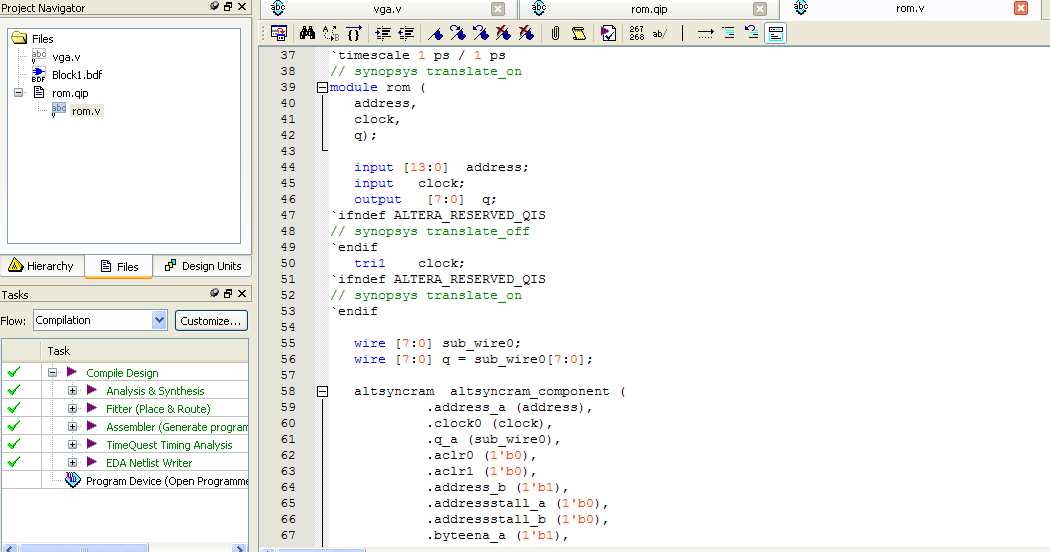

51FPGA的教程中12864实验中使用到了rom,但没介绍怎么调用rom。我在VGA的图片的256色显示中也使用了rom,在这里给大伙介绍一下。

使用IP核使用引导。

有两块ROM,选择其一。如上图所示。

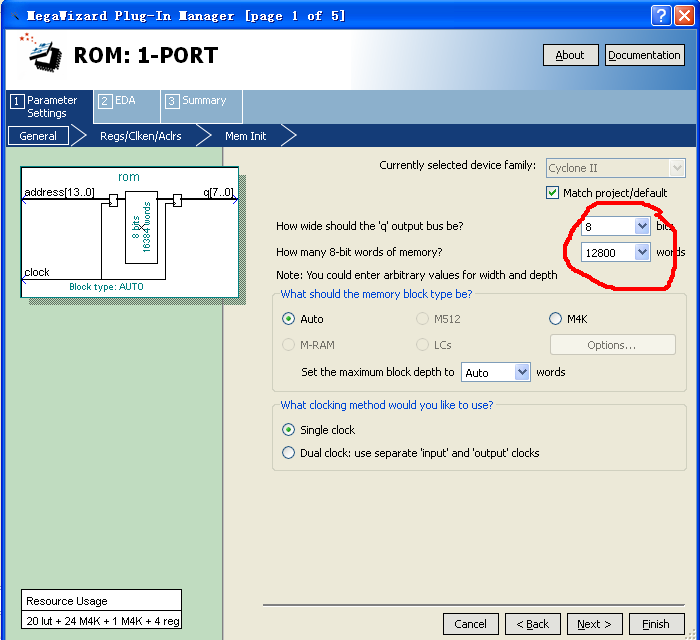

注意红色标识处,在这里填好你的位宽和字数,一定要与你的.mif(.hex)文件的位宽和字数一致。单色显示的位宽应该是1,我256色的VGA,所以填的是8。图左下角是你能用的空间,M4K=1024*4bit,要确保你使用的空间不溢出,否则编译报错。如上图所示。

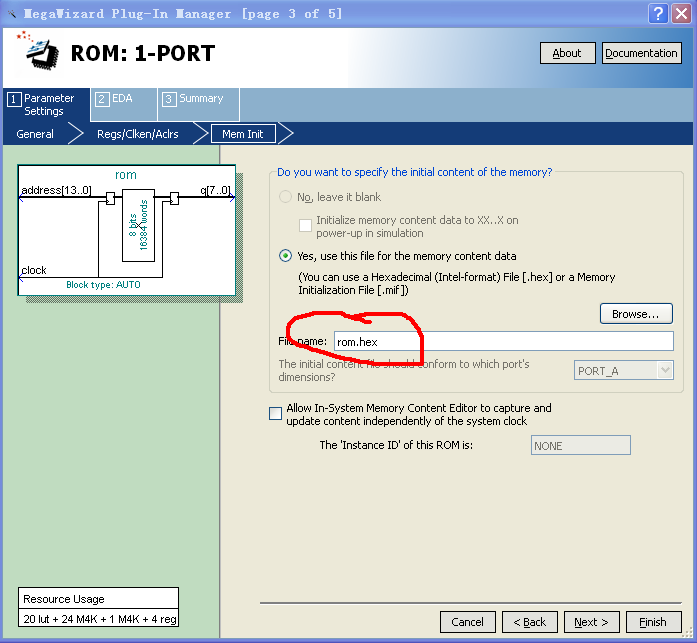

在这里添加已编译好的mif文件,51fpga介绍了hex的制作过程。如上图所示。

到这里就finish了,

在你的工程文件下会自动生成一个rom.v(名字你自己定义)的文件如下图所示

在top层中调用:

详细的见:VGA的256色显示的源代码http://forum.eepw.com.cn/thread/221172/16#155

回复

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| Chaos-nano:专为低资源单片机设计的轻量级协作式异步操作系统(ATMEGA328P轻量级操作系统)—— 详细介绍被打赏¥16元 | |

| FPGA配置被打赏¥10元 | |

| Chaos-nano协作式异步操作系统:赋能MicrochipAVR8位单片机的革新之路被打赏¥15元 | |

| 基于esp32开发时串口工具的注意点被打赏¥24元 | |

| 基于FireBeetle2ESP32-C5开发板的舵机控制被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】MAX78000开发板制作的电子相册被打赏¥32元 | |

| 基于FireBeetle2ESP32-C5开发板的超声波测距及显示被打赏¥21元 | |

| FireBeetle2ESP32-C5上RTC电子时钟的实现被打赏¥25元 | |

| 【分享开发笔记,赚取电动螺丝刀】MAX78000开发板读取SD卡被打赏¥23元 | |

| 【S32K3XX】Standby RAM 重启后数据异常问题调查被打赏¥38元 | |