我的LED灯——作业1

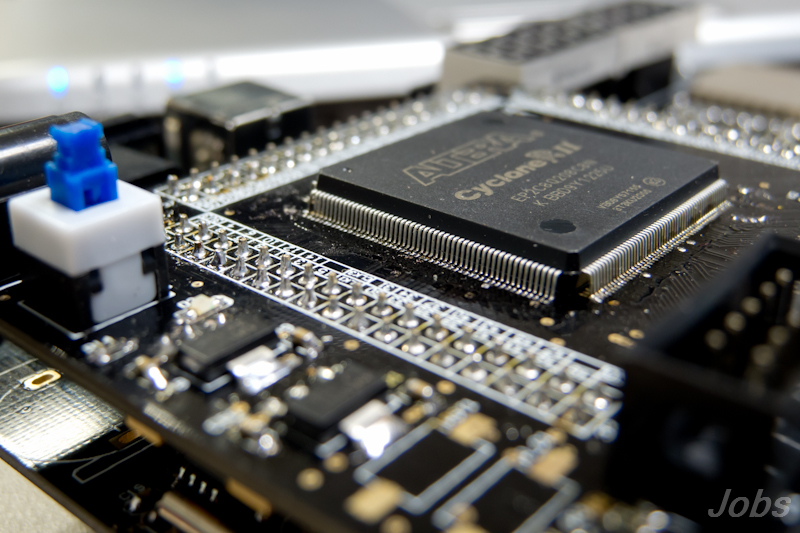

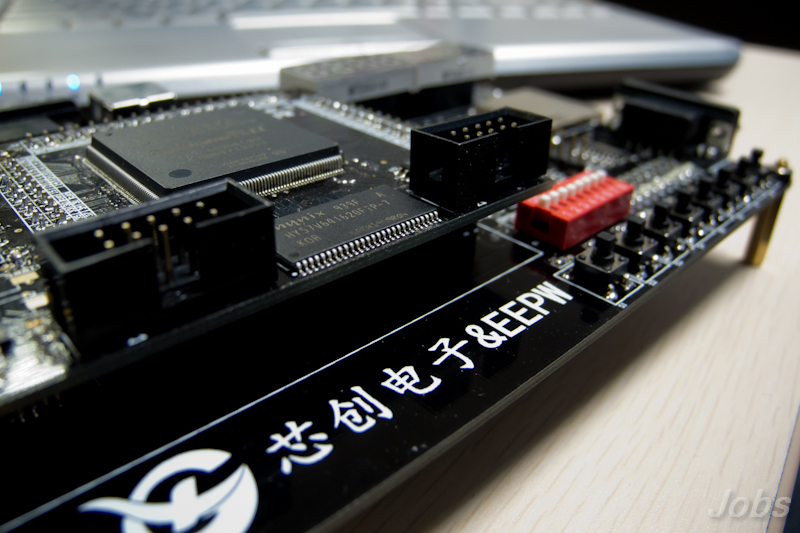

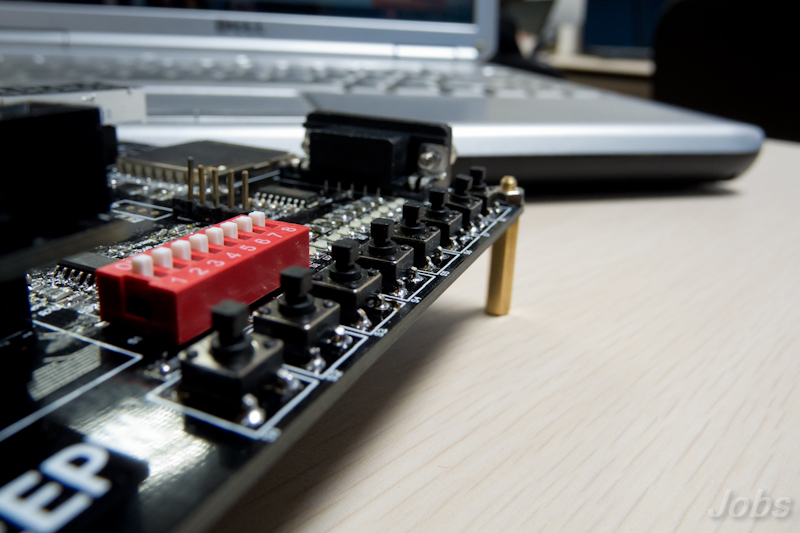

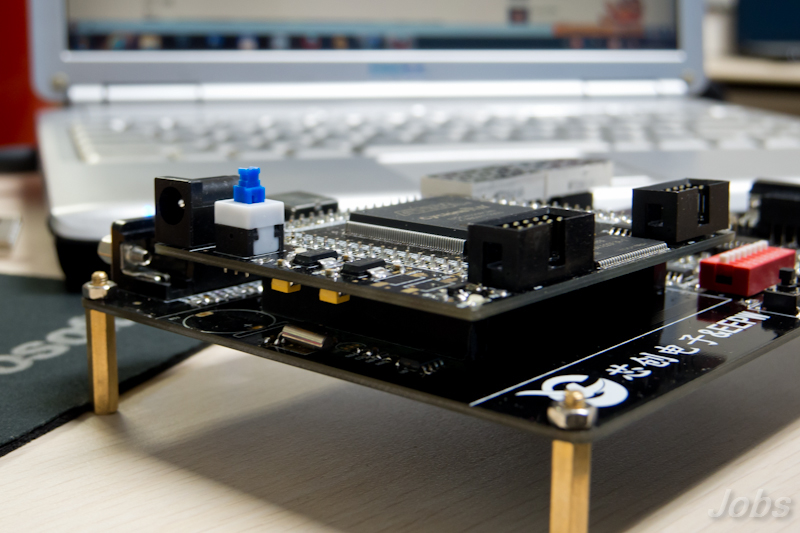

实验目的: 熟悉QuartusII软件及FPGA初学 熟悉verilog语言 实验内容: 将LED灯间隔点亮,此为常亮。 源代码如下:

module led_show(led);

output [7:0] led; assign led = 8'b10101010; endmodule 将LED灯以每隔0.5秒闪烁,源代码如下:module led_flicker(sys_clk, sys_rstn, led);

input sys_clk; input sys_rstn; output [7:0] led; /* LED输出信号 */ reg [7:0] led; reg [24: 0] delay_cnt; always @(posedge sys_clk or negedge sys_rstn) begin if(!sys_rstn) delay_cnt <= 25'd0; else begin if(delay_cnt == 25'd24999999) delay_cnt <= 25'd0; else delay_cnt <= delay_cnt + 1'b1; end endalways @ (posedge sys_clk or negedge sys_rstn)

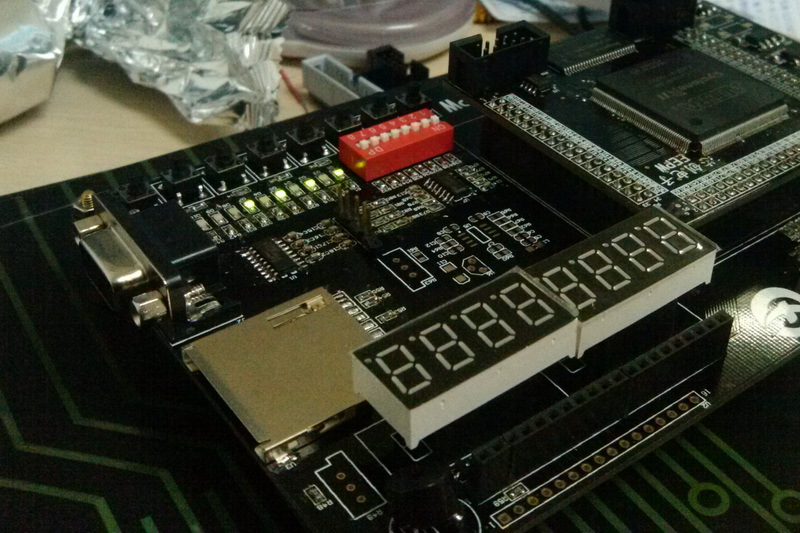

begin if(!sys_rstn) led <= 8'b11111111; else begin if(delay_cnt == 25'd24999999) led <= ~led; else led <= led; end end endmodule 实验结果: 完成LED灯交替常量显示 根据教程所示,将LED灯以1Hz交替显示。(视频省略)

作业:

LED灯以0.5Hz的频率闪烁,此时只须要更改1Hz的时钟计数周期即可,源代码如下:

根据教程所示,将LED灯以1Hz交替显示。(视频省略)

作业:

LED灯以0.5Hz的频率闪烁,此时只须要更改1Hz的时钟计数周期即可,源代码如下:

module led_flicker(sys_clk, sys_rstn, led);

input sys_clk; input sys_rstn; output [7:0] led; /* LED输出信号 */ reg [7:0] led; reg [25: 0] delay_cnt; always @(posedge sys_clk or negedge sys_rstn) begin if(!sys_rstn) delay_cnt <= 26'd0; else begin if(delay_cnt == 26'd4999999) delay_cnt <= 26'd0; else delay_cnt <= delay_cnt + 1'b1; end endalways @ (posedge sys_clk or negedge sys_rstn)

begin if(!sys_rstn) led <= 8'b11111111; else begin if(delay_cnt == 26'd4999999) led <= ~led; else led <= led; end end endmodule 完成编译,并成功在fpga开发板上显示。Cheer~~回复

| 有奖活动 | |

|---|---|

| 2026年“我要开发板活动”第三季,开始了! | |

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| RTOS怎么选?让我来给你答案!被打赏¥15元 | |

| 【S32K3XX】Flash驱动使用被打赏¥26元 | |

| 【FreeRtos】第一个任务的启动过程被打赏¥21元 | |

| 【分享开发笔记,赚取电动螺丝刀】FPB-RA6E2开发板的WDT功能测试被打赏¥22元 | |

| 关于cmakelist特性presets的使用被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】M5STACK系列屏幕质量测试程序,竟然有块亮斑?被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】快速搭建瑞萨FPB-RA6E2开发板开发环境被打赏¥14元 | |

| 【分享开发笔记,赚取电动螺丝刀】在音频测试中顺序的调整可改变功效被打赏¥18元 | |

| 【分享开发笔记,赚取电动螺丝刀】点阵显示模块及其应用-----献给新年的小礼物被打赏¥22元 | |

| 基于地奇星开发板的数码管模块显示技术被打赏¥23元 | |