我选择第二(一)种方案:申请PCB板,购买组委会提供的元器件包

实验名称:基于CPLD的计数器及时钟设计

实验概要:完成功能:实时时钟芯片读取时间,按键可设置闹铃值并修改时间值,12864显示时钟(指针)、闹铃值、当前温度。并实现一个计数器可以用来测速等功能。

关注这个CPLD的DIY很久了,以前学过的51,STM8,PIC等都是C语言编程,虽说有一定的编程基础,但Verilog HDL只是在学校接触过,并不熟悉,想通过贵网站的DIY活动实现这个实验,能熟练掌握CPLD对各种外设、总线的操作。自己的方向是高速数据采集,也想为以后的FPGA学习打下基础。希望我能从这次活动中有所收获。

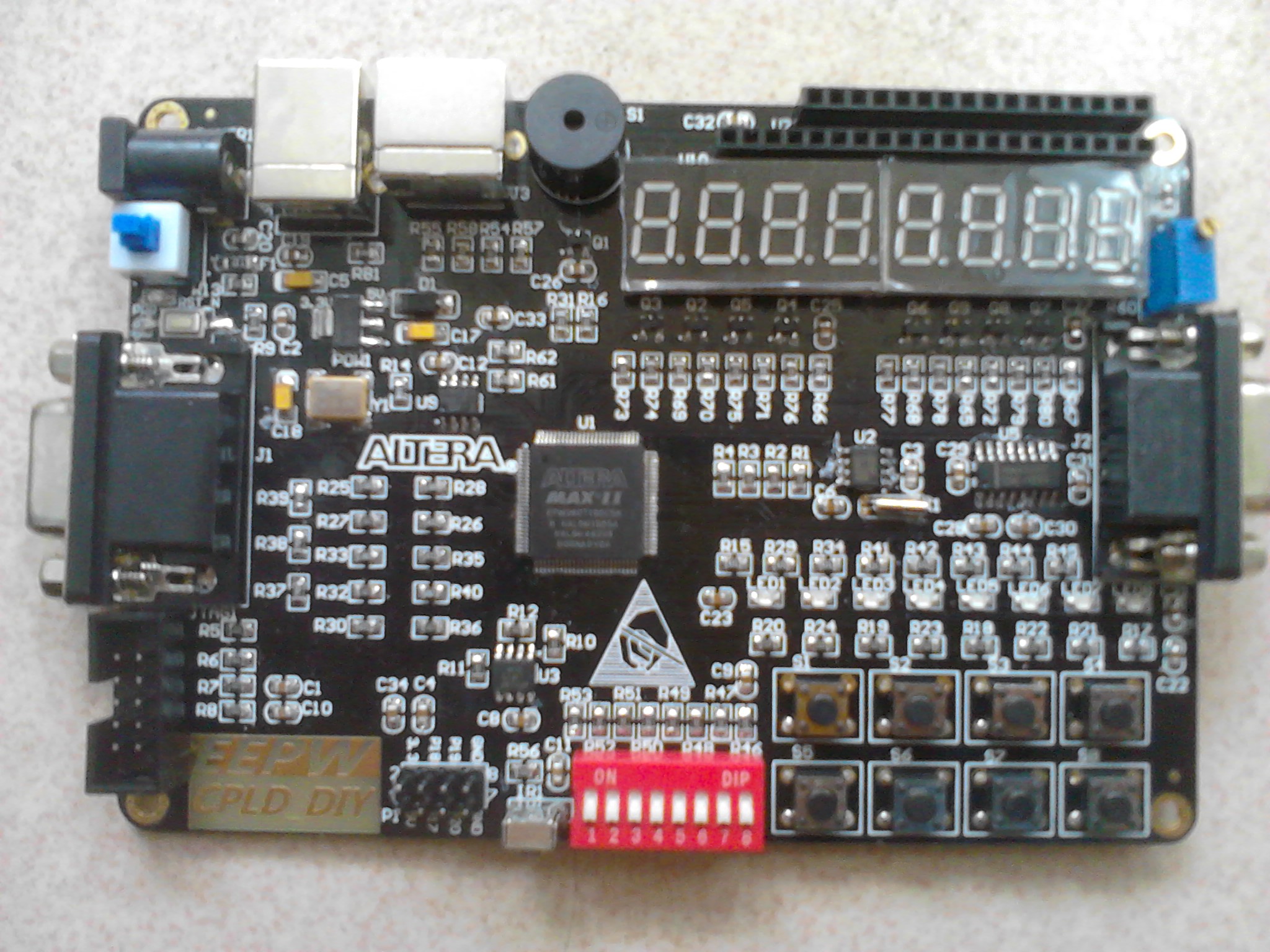

这周事太多了,进程有点慢了,只能晒一下焊好的板子了。明天开始追赶进度。

这周事太多了,进程有点慢了,只能晒一下焊好的板子了。明天开始追赶进度。

我要赚赏金

我要赚赏金