如题,例如:我的运放TLV2171,输出在-0.3V~3V,请问我的供电电压分别为±5V和±15V,对运放的输出有什么影响?

共5条

1/1 1 跳转至页

不同的供电电压分,对运放的小信号输出有什么影响吗?

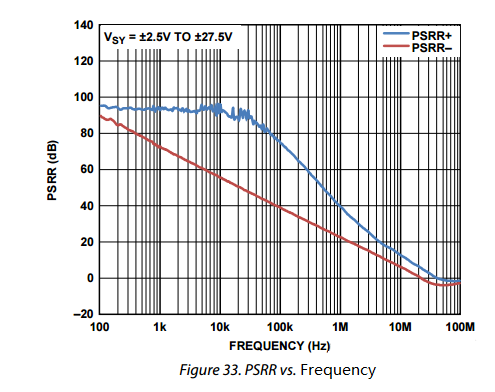

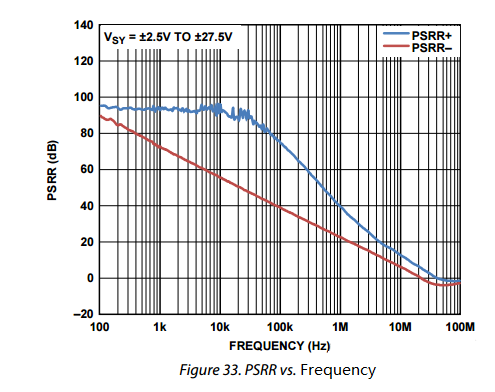

看看刚看到的这个文章。3.运放十坑之快速下降的PSRR

根据计算公式:

即使电源电压在4.5V-5.5V区间内发生变化,电源对运放输出的影响只有10nV。

对于500kHz开关频率的纹波,PSRR+恶化到只有50dB,假设纹波大小为100mV,那么对于后级的影响恶化会达到0.3mV。对于很多小信号采集的应用来说,这个误差是不可接受的。因此,有些应用场景甚至会在运放电源入口做一个低通滤波(请注意电阻功耗和电阻热噪声)。

对于500kHz开关频率的纹波,PSRR+恶化到只有50dB,假设纹波大小为100mV,那么对于后级的影响恶化会达到0.3mV。对于很多小信号采集的应用来说,这个误差是不可接受的。因此,有些应用场景甚至会在运放电源入口做一个低通滤波(请注意电阻功耗和电阻热噪声)。

根据计算公式:

即使电源电压在4.5V-5.5V区间内发生变化,电源对运放输出的影响只有10nV。

对于500kHz开关频率的纹波,PSRR+恶化到只有50dB,假设纹波大小为100mV,那么对于后级的影响恶化会达到0.3mV。对于很多小信号采集的应用来说,这个误差是不可接受的。因此,有些应用场景甚至会在运放电源入口做一个低通滤波(请注意电阻功耗和电阻热噪声)。

对于500kHz开关频率的纹波,PSRR+恶化到只有50dB,假设纹波大小为100mV,那么对于后级的影响恶化会达到0.3mV。对于很多小信号采集的应用来说,这个误差是不可接受的。因此,有些应用场景甚至会在运放电源入口做一个低通滤波(请注意电阻功耗和电阻热噪声)。共5条

1/1 1 跳转至页

回复

| 有奖活动 | |

|---|---|

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

| 打赏了!打赏了!打赏了! | |

我要赚赏金

我要赚赏金