作者:包云岗 来源:知乎

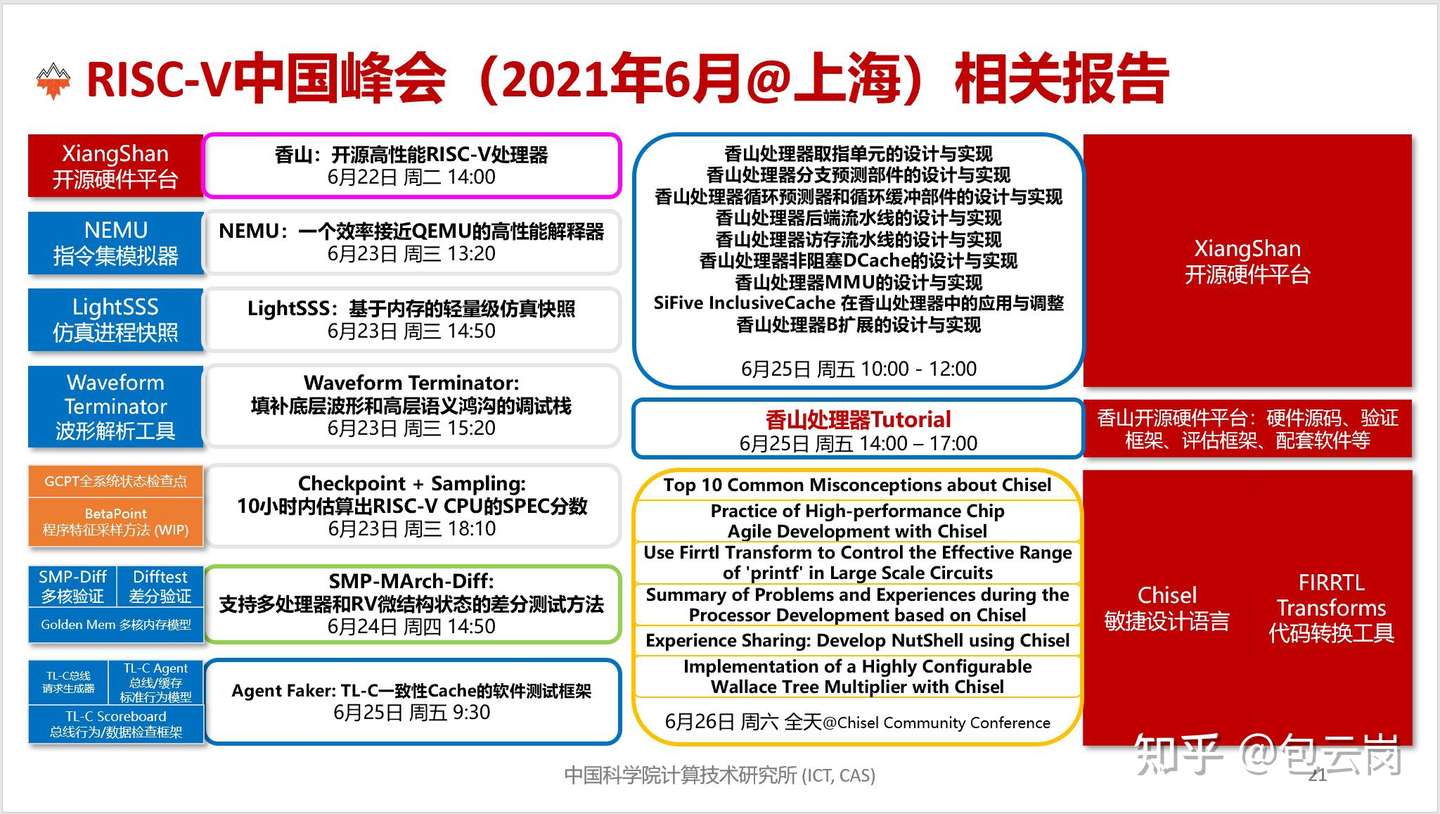

2021 RISC-V中国峰会 香山的报告。

一、为什么要做香山?

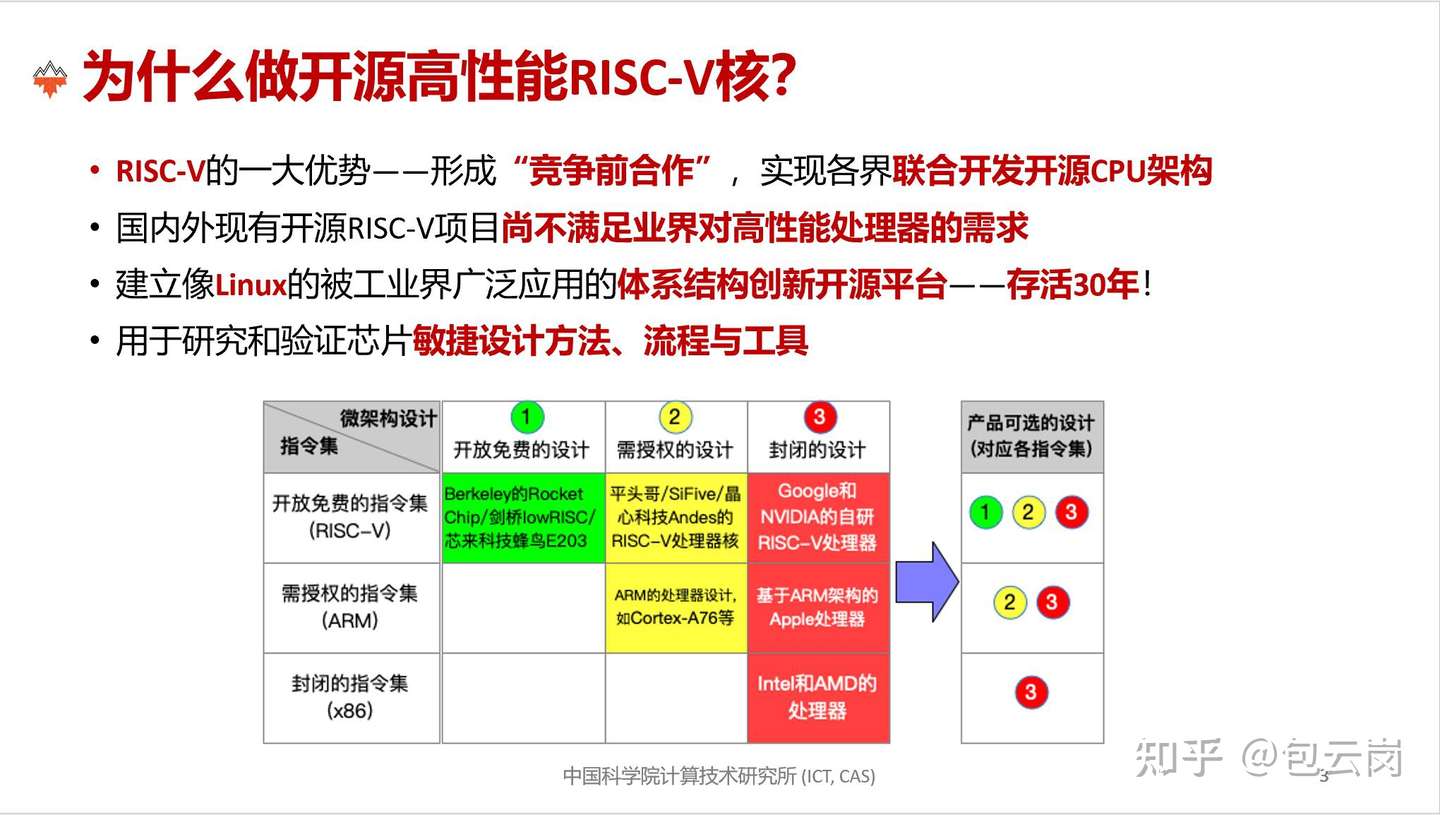

1. 2010年RISC-V诞生,迄今已有11年。如今,在RISC-V国际基金会网站上登记的各类商业或开源的RISC-V处理器核就有上百个(如下链接),为什么还要做一个开源的高性能RISC-V核?

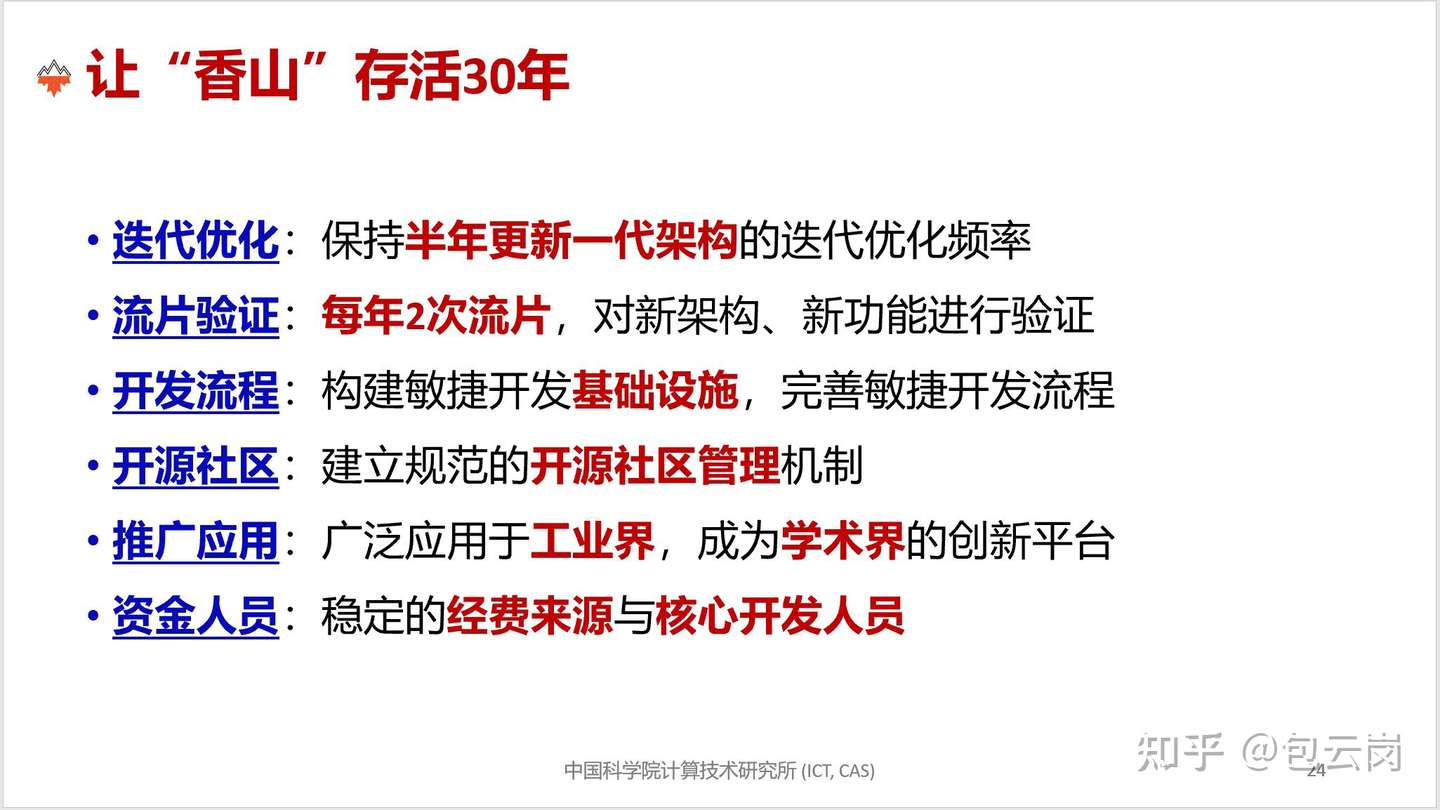

对于这个问题,我们和很多业界企业交流过,也做了很多调研与分析,这都让我们判断认为业界需要一个开源的高性能RISC-V核。另一方面,我们也在思考一个问题——为什么CPU领域还没有一个像Linux那样的开源主线?1991年开源的Linux诞生,到今天正好30年。如今,Linux不仅被工业界广泛应用,也成为学术界开展操作系统研究的创新平台。

RISC-V是开放开源的指令集,允许全世界任何人免费实现一个RISC-V处理器,可以是商用,也可以开源,这是和公司私有的X86/ARM指令集相比最大的区别之一。但是,十年过去了,到现在还未能形成一个像Linux那样的开源主线。Berkeley的BOOM目标是一个高性能开源RISC-V核,但是BOOM代码仓库相对不开放,官方建议其他人实现任何功能都要事先和他们沟通,以确保不要与他们的计划产生冲突。根据GitHub官方的统计页面显示,从2014年1月至今,为BOOM提交过超过100行代码修改的仅有8人。由此可见,一定程度上因为BOOM严格的外部贡献政策,开源社区对BOOM的参与度并不高。

所以,团队的唐丹博士和我一直认为要建立一个像Linux那样的开源RISC-V核主线,既能被工业界广泛应用,又能支持学术界试验创新想法。最关键的是,一定要让它像Linux那样至少存活30年!

于是,“香山”诞生了。

2. 我们做了一年多的准备工作——申请经费,启动“一生一芯”计划培养人才,建立团队,寻找合作伙伴……这期间得到了太多太多人的支持和帮助:计算所孙凝晖院士帮我们多处找经费,国科大全力支持“一生一芯”计划,鹏城实验室支持我们建立起后端物理设计团队,多位计算所老所友毅然决定参与开源主线等等,就不一一列举了。

终于,香山正式启动了——2020年6月11日,香山在GitHub上建立了代码仓库。

短短的的一年时间里,25位同学和老师参与了香山的开发。821次主分支代码合并,3296次代码提交(commit),5万余行代码,400多个文档,记录了香山的成长过程。我们的理念是代码开源、流程开放、文档公开。这期间,有企业直接参与开发,也有企业表达参与意向,都因为认同开源理念,愿意一起来共建开源的香山。这些来自工业界的积极反馈,给与我们极大的鼓舞和信心,让我们更坚定地去践行“科研重工业模式”。

“科研重工业模式”,是 2020年1月我为《中国计算机学会通讯(CCCF)》写了一篇卷首语《伯克利科研模式的启发》中提出的:

回顾伯克利的科研历程,可以发现他们在过去几十年研制了大量的原型系统,不仅推动了技术进步甚至颠覆产业,也培养了一代代杰出人才(其中多位获得图灵奖):1950年代CALDIC系统(Doug Englebart),1960年代Project Genie系统(Butler Lampson与Chuck Thacker),1970年代BSD Unix操作系统与INGRES数据库系统(Michael Stonebraker),1980年代RISC处理器(David Patterson),1990年代RAID存储系统与NOW机群系统……如果用一句话来总结伯克利的科研模式,那就是——热衷于研制真正能改变现状的原型系统,哪怕需要大量工程投入。国重主任孙凝晖院士称之为“科研重工业模式”。

“科研重工业模式”,我们不想纸上谈兵,我们要用行动去实践。

二、香山什么水平?

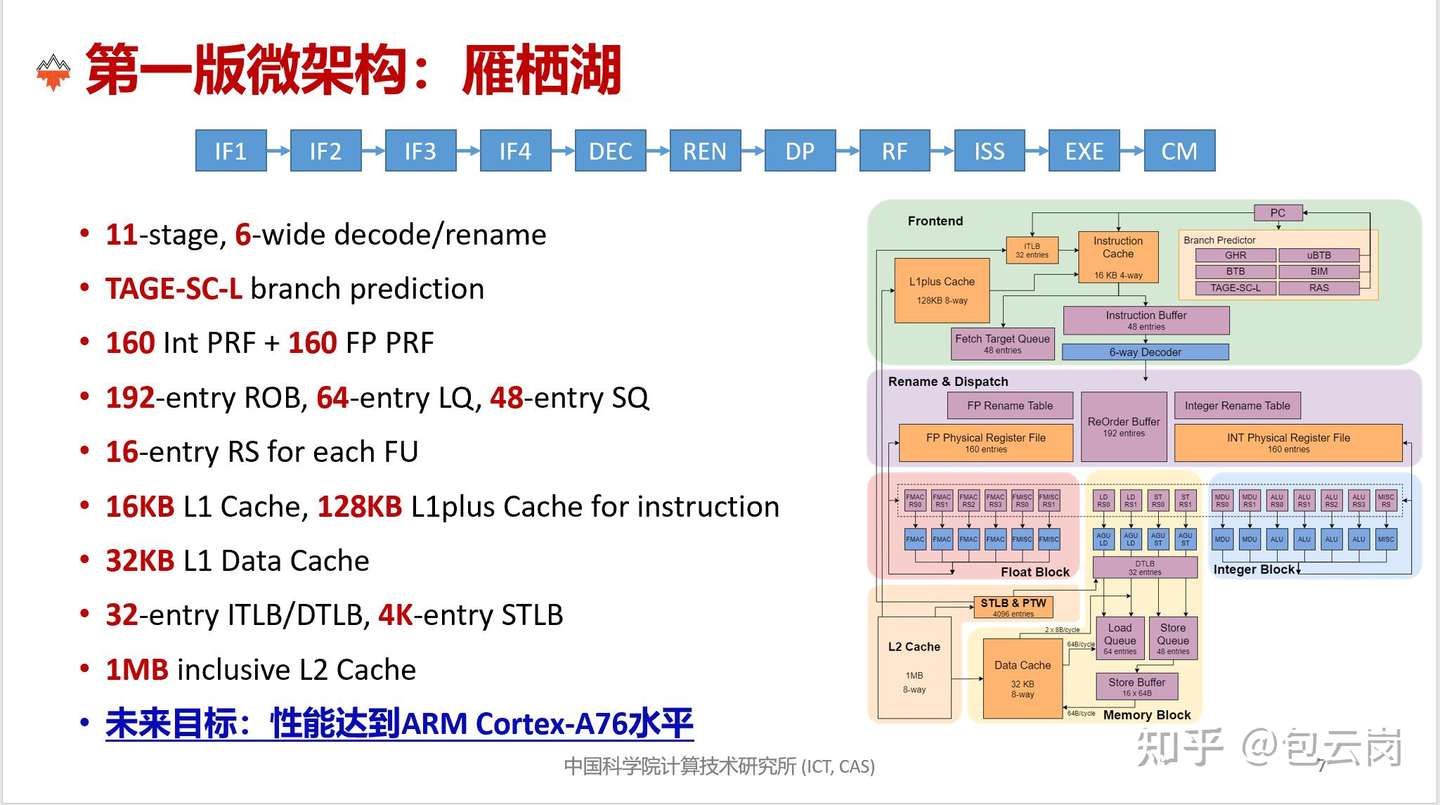

3. 香山是一款开源RISC-V处理器核,它的架构代号以湖命名。第一版架构代号是“雁栖湖”,这是带有浓重国科大情节的同学们起的名字,因为他们研一都在怀柔雁栖湖待了一年。“雁栖湖”RTL代码于2021年4月完成,计划于7月基于28nm工艺流片,目前频率为1.3GHz。

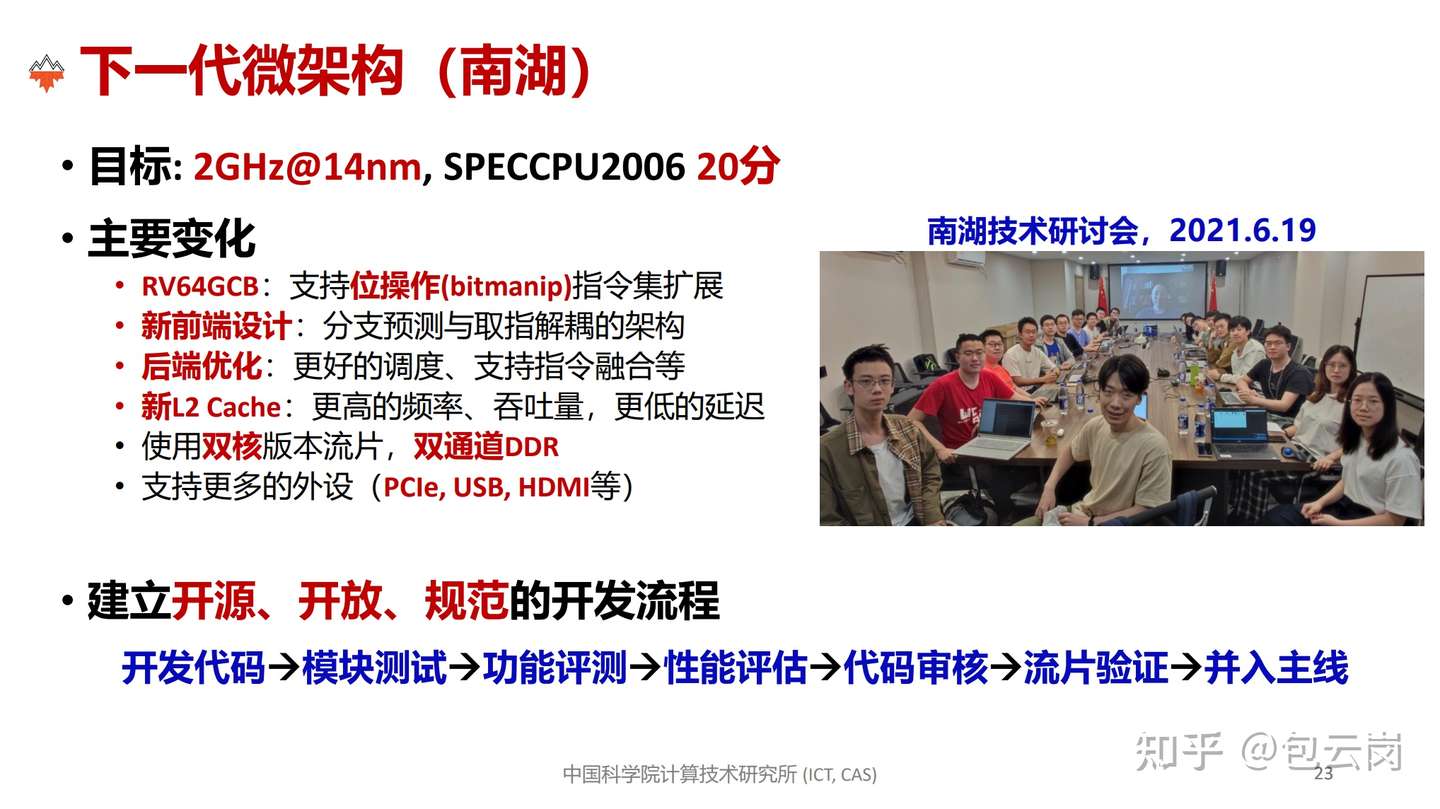

第二版架构代号是“南湖”,这是向建党100周年致敬。“南湖”计划在今年年底流片,将采用14nm工艺,目标频率是2GHz。

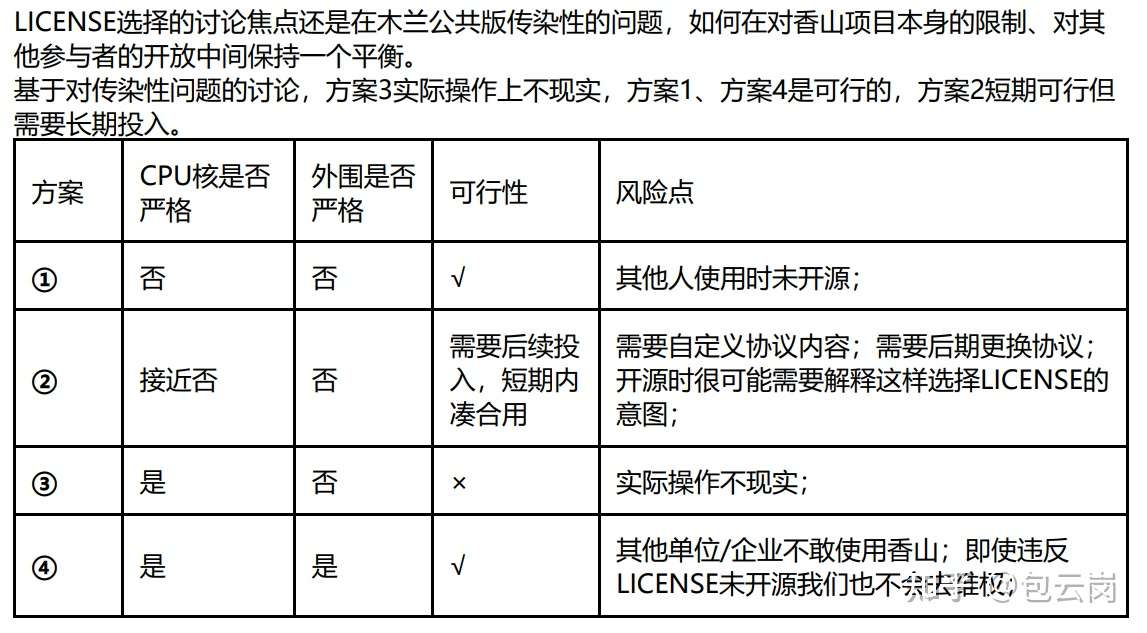

香山选择什么开源许可证?这个问题纠结了我们好一阵子。后来,我们专门向北京大学周明辉教授请教,小伙伴们制定了4种开源许可证方案。在反复对比权衡后,最终选择了如下表格中的方案①——木兰宽松版许可证(MulanPSLv2)。在此,特别感谢北大周明辉老师的专业指导!

开源许可证方案对比(徐易难整理)

4. “雁栖湖”架构是一个11级流水、6****、4个访存部件的乱序处理器核。在****宽度上已经可以和一些ARM高端处理器核相当,但还未进行充分优化,因此实际性能还有不小的差距。我们希望未来通过持续迭代优化(“南湖”-->"X湖"-->"Y湖"-->……),性能达到ARM A76的水平。

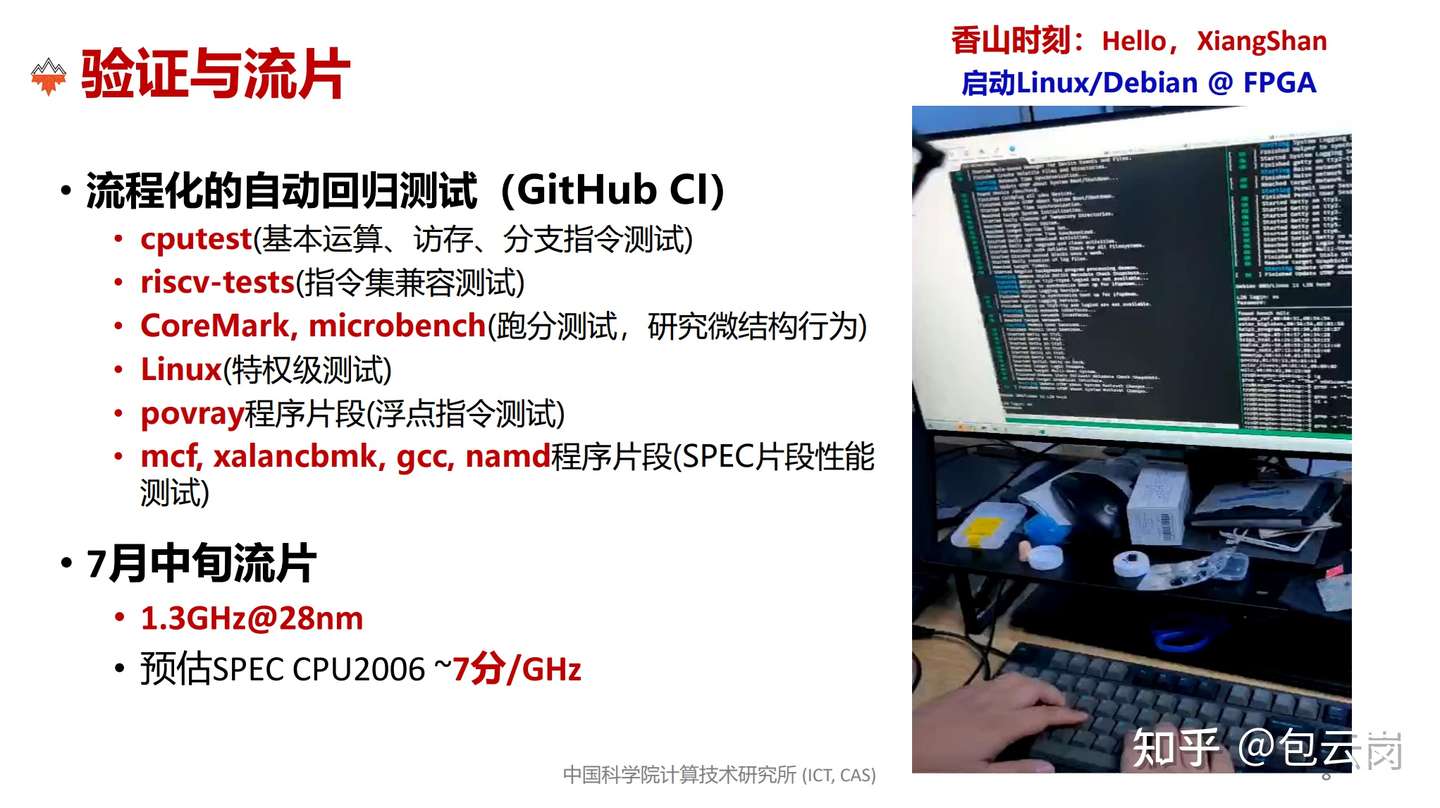

5. 我们基于GitHub CI构建了一套流程化的自动回归测试框架,并在过去大半年不断增加测试负载,从cputest,risc-tests到Linux,到SPECCPU workload。这套自动回归测试框架在保障和验证芯片的正确性。

三、香山怎么做的?

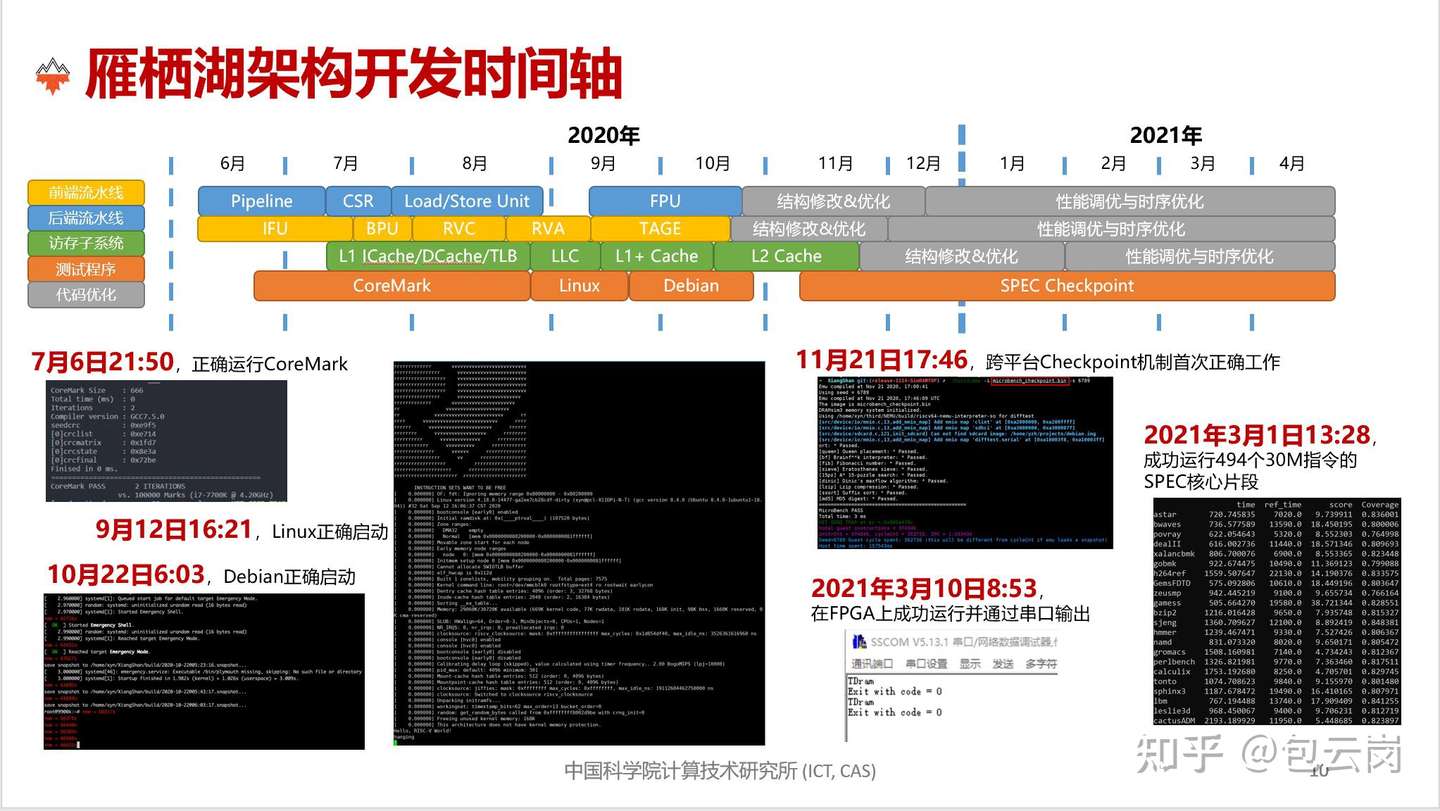

6. 香山开发初期速度非常快:6月11日建立代码仓库,7月6日乱序流水线便已完成,能正确运行CoreMark,不到一个月时间;9月12日,Linux正确启动;10月22日,Debian正确启动。

接下来便是大半年的结构优化、性能调优、时序优化工作,香山架构几乎相当于重构了一遍。一个典型的例子,香山的第一版分支预测器(BPU)参考了BOOM的BPU,但后端评估频率只能达到800MHz(28nm)。于是负责BPU设计的勾凌睿在几位老师的指导下,不断优化BPU结构,最终将频率提升到了1.4GHz。

这期间,小伙伴们纷纷自己动手,开发了各种各样的优化和调试工具,大大地加速了优化和验证环节。这让我真心佩服这批90后——他们真是充满了创造力,从工作到生活,而主要驱动力之一就是“省(tou)时(lan)”。比如宁可自己写个程序自动点外卖,也懒得打开手机看菜单点。

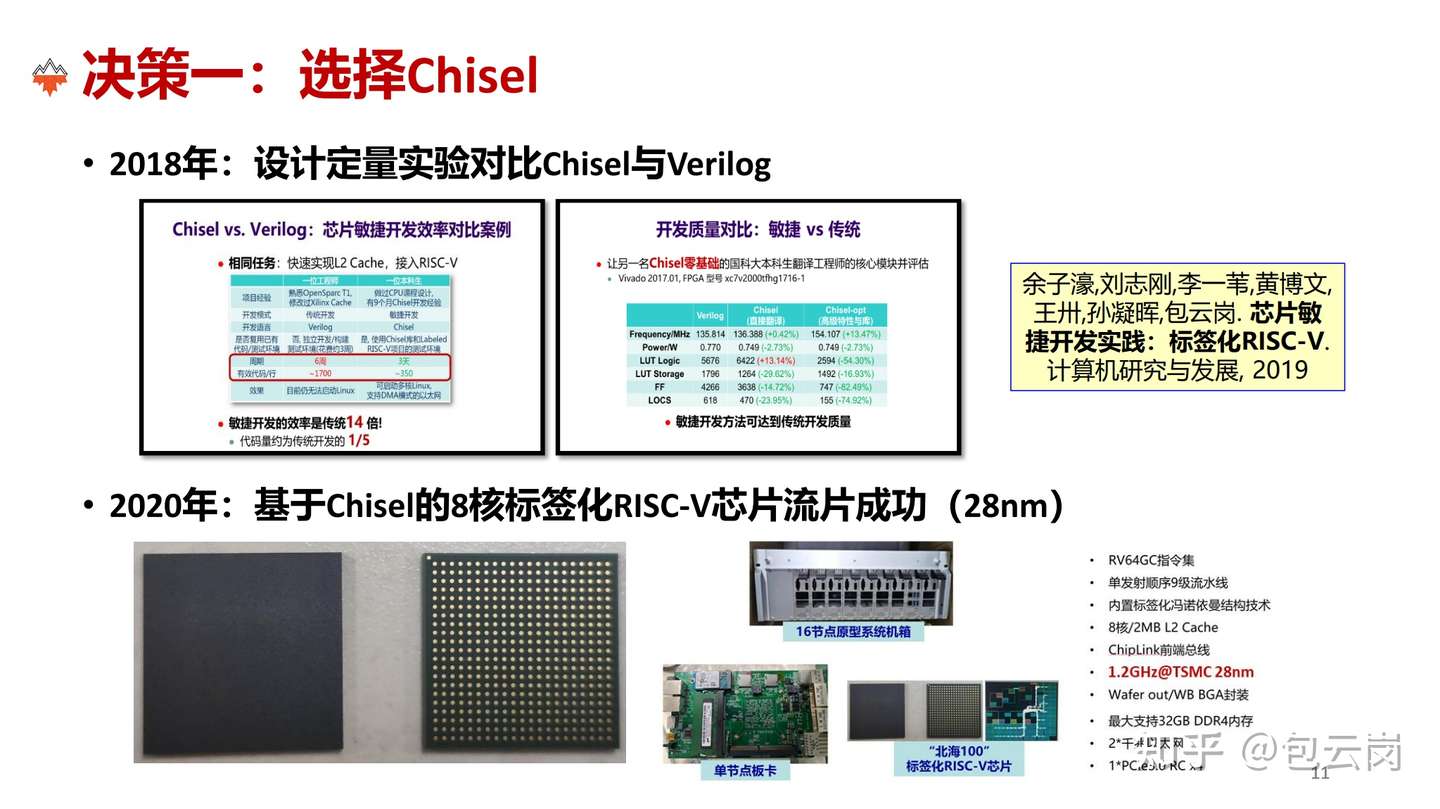

7. 香山的开发至少有两个重要的决策,第一个便是选择敏捷设计语言Chisel。很多人质疑Chisel,排斥Chisel,但是我们在充分评估后,还是决定使用Chisel。

我们团队是在2016年开始使用Chisel,一开始组里也充满质疑。2018年,我们设计了两组定量的对比实验,找了2位同学用Chisel、1位工程师用Verilog分别设计一个L2 Cache模块。通过一系列量化对比,得出了如下三个结论:

1)Chisel开发效率远高于Verilog;

2)实现相同的功能,Chisel代码量仅为Verilog的1/5(因此香山的5万行Chisel代码相当于25万行Verilog代码);

3)Chisel的开发质量不比Verilog差。

后来将实验结果发表在2019年1月的《计算机研究与发展》。最近去华为交流,才知道这些对比结果也推动了华为内部组建了Chisel开发团队,如今华为也是Chisel的支持者。

2020年,我们又基于Chisel完成了一款8核标签化RISC-V处理器的流片,这是基于Rocket处理器核进行了标签化体系结构改造,采用28nm工艺流片。虽然因为时间紧张,并没有进行细致的后端优化,但芯片返回后也还能正常运行在1.2GHz。这是一颗有一定复杂度的8核SoC芯片,但Chisel能应对。所以,我们相信Chisel可用来开发复杂芯片。

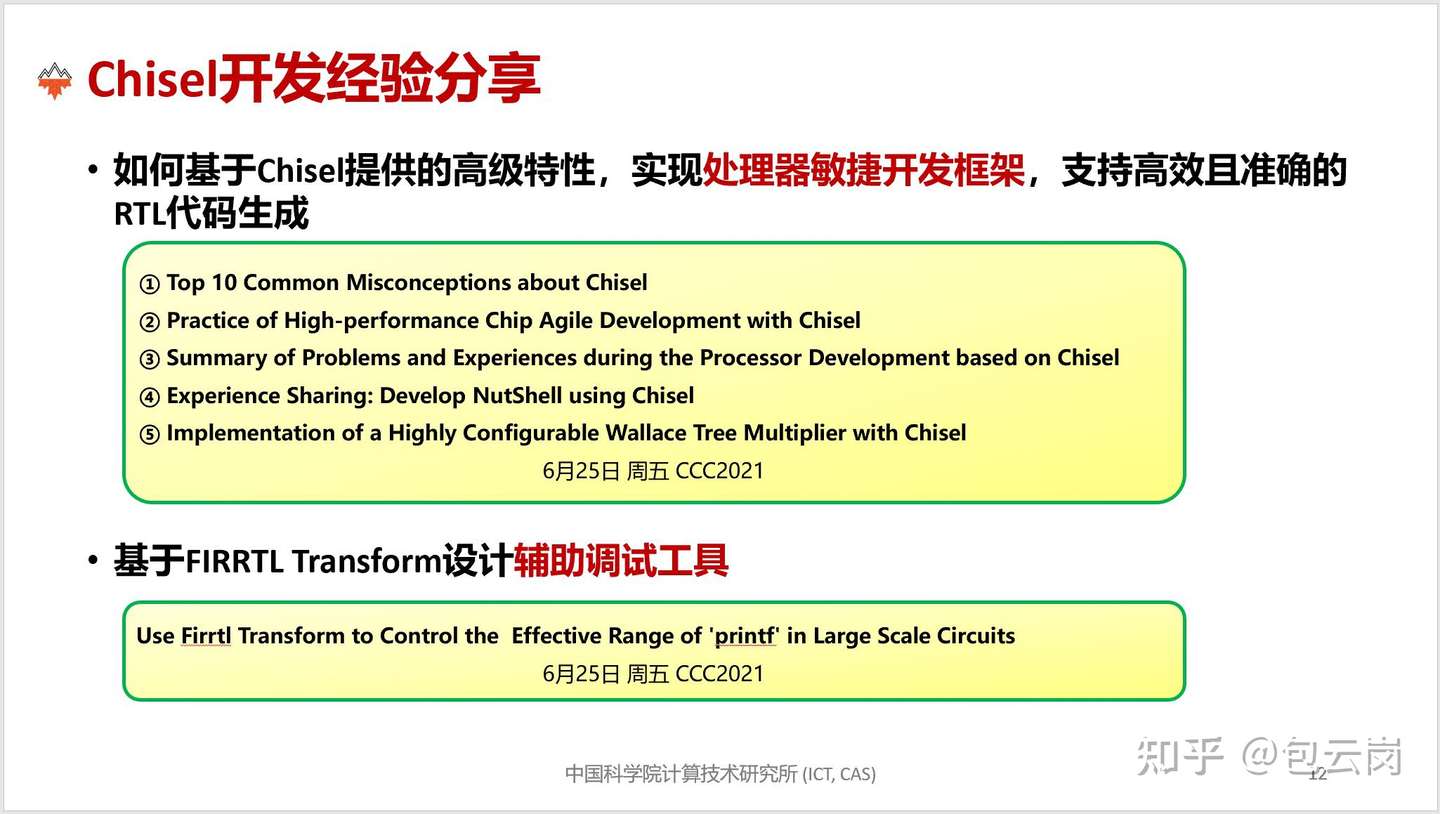

8. 在开发香山的过程中,我们团队积累了丰富Chisel开发经验。小伙伴们(徐易难、王凯帆、蔺嘉炜、余子濠、金越)准备了6个报告,将会在6月25日的CCC Workshop上和大家分享。

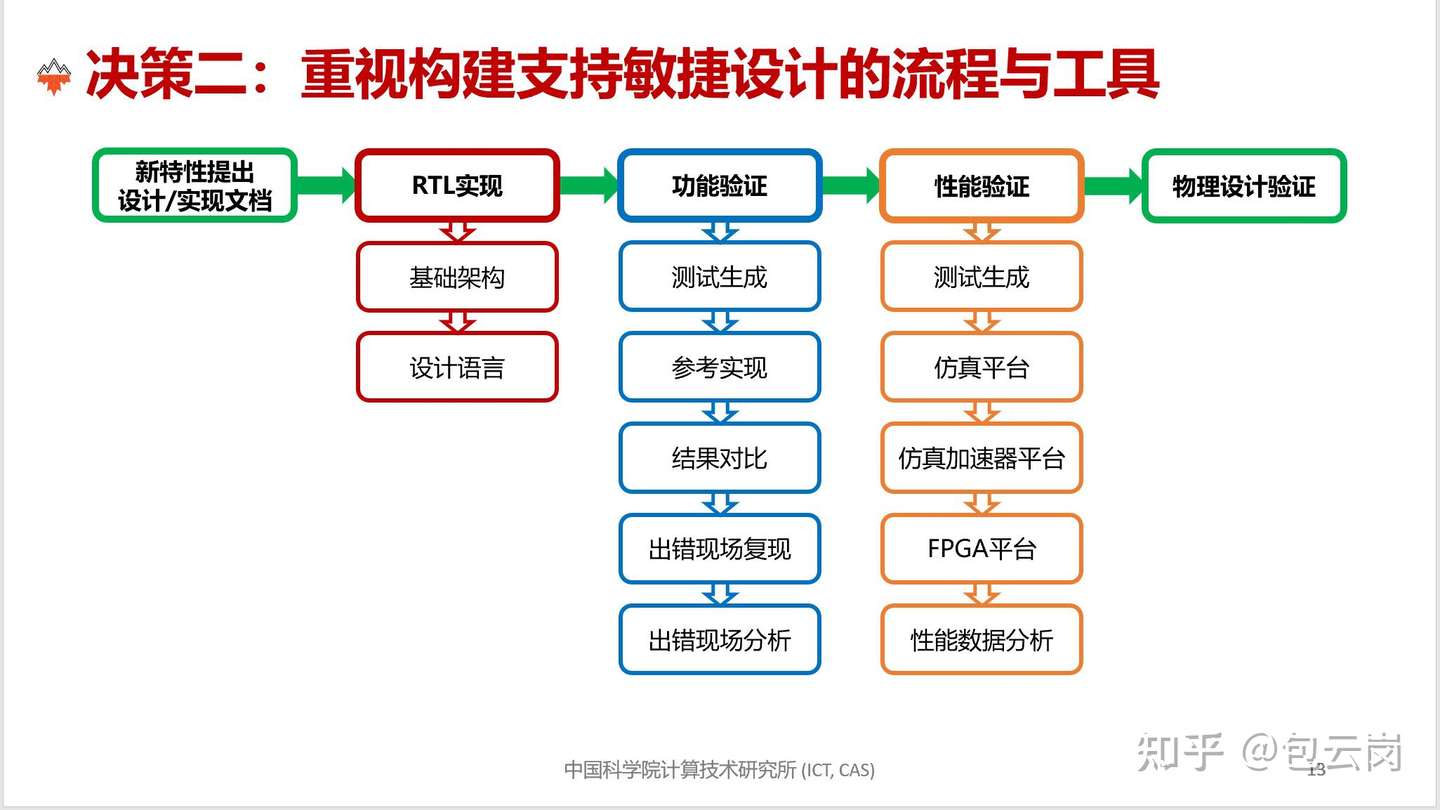

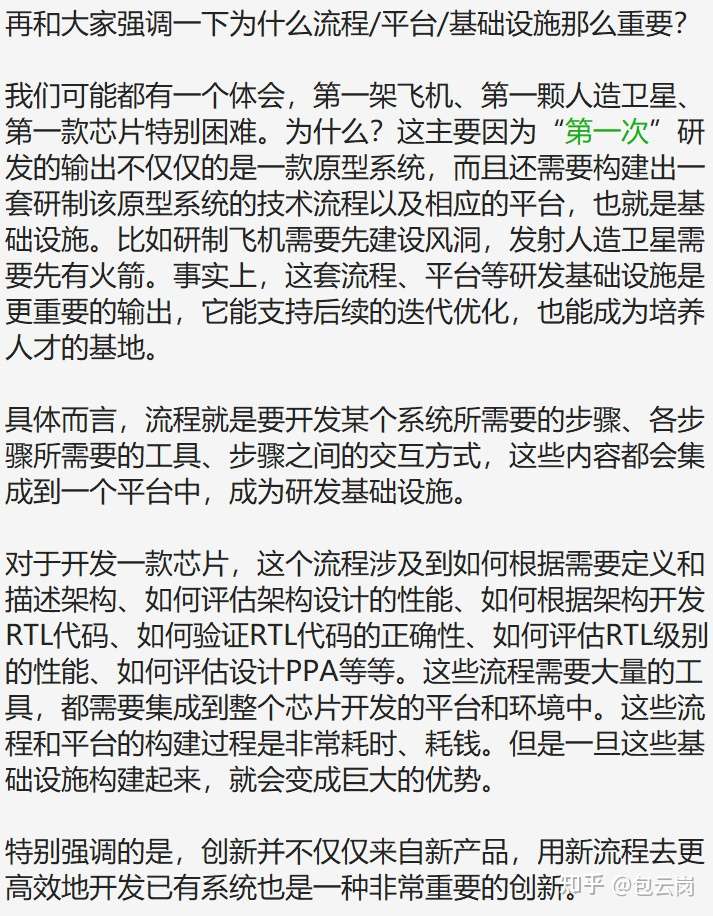

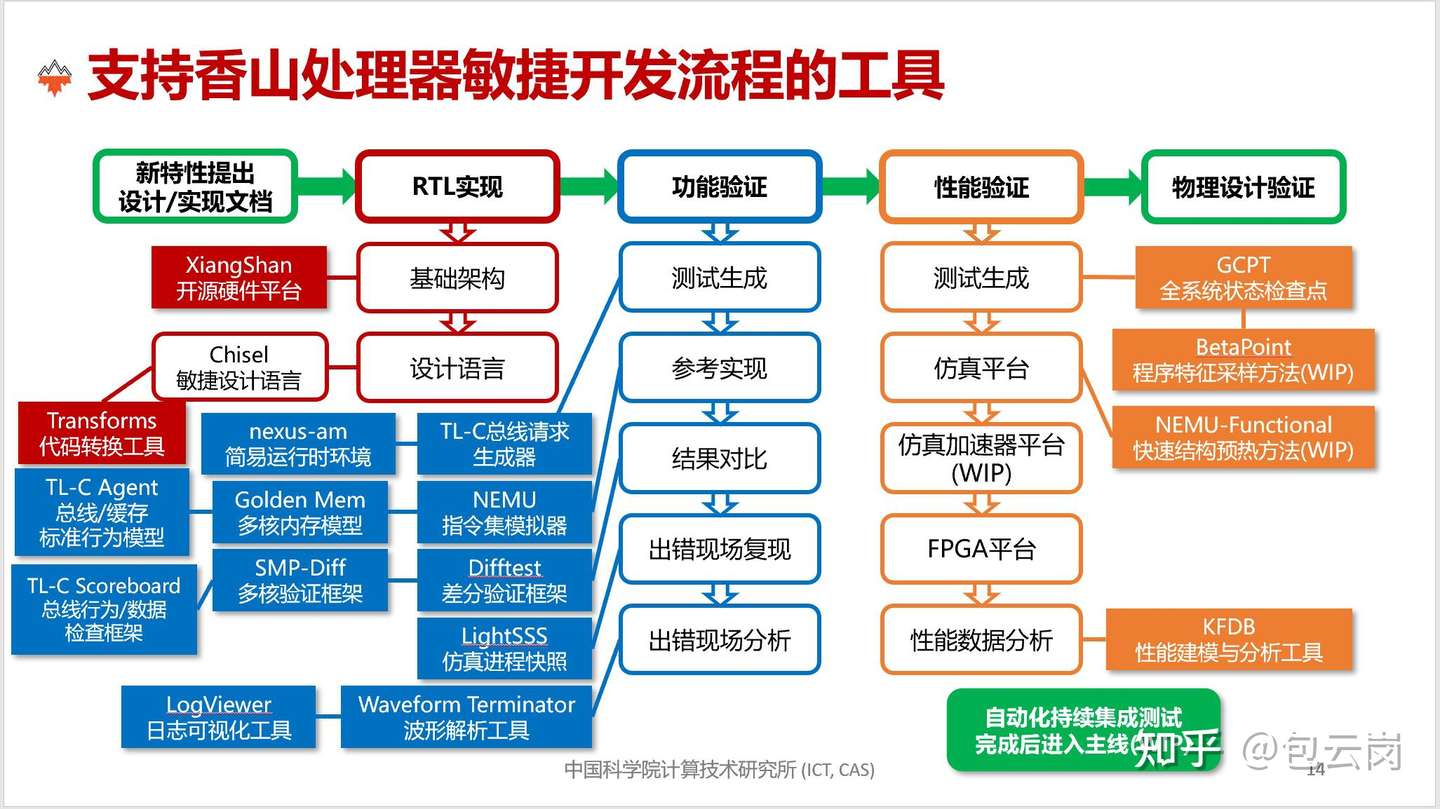

9. 另一个重要决策就是高度重视构建支持敏捷设计的流程与工具。

我们在开发香山的过程中,一直在强调流程、平台、基础设施的重要性。我更多是扮演了啦啦队队长的角色,而小伙伴们则真正将理念落实到了具体行动。

10. 为了更好地支持Chisel开发与调试,为了更快地捕捉、复现和定位bug,为了更准确地评估优化技术的性能收益,小伙伴们开发十余种各具特色的工具。这些工具支撑起了一套处理器芯片敏捷开发的流程。当然,这套流程还比较初级,尚不系统化。我们也期待更多的开源开发者加入,一起完善这套敏捷设计流程。

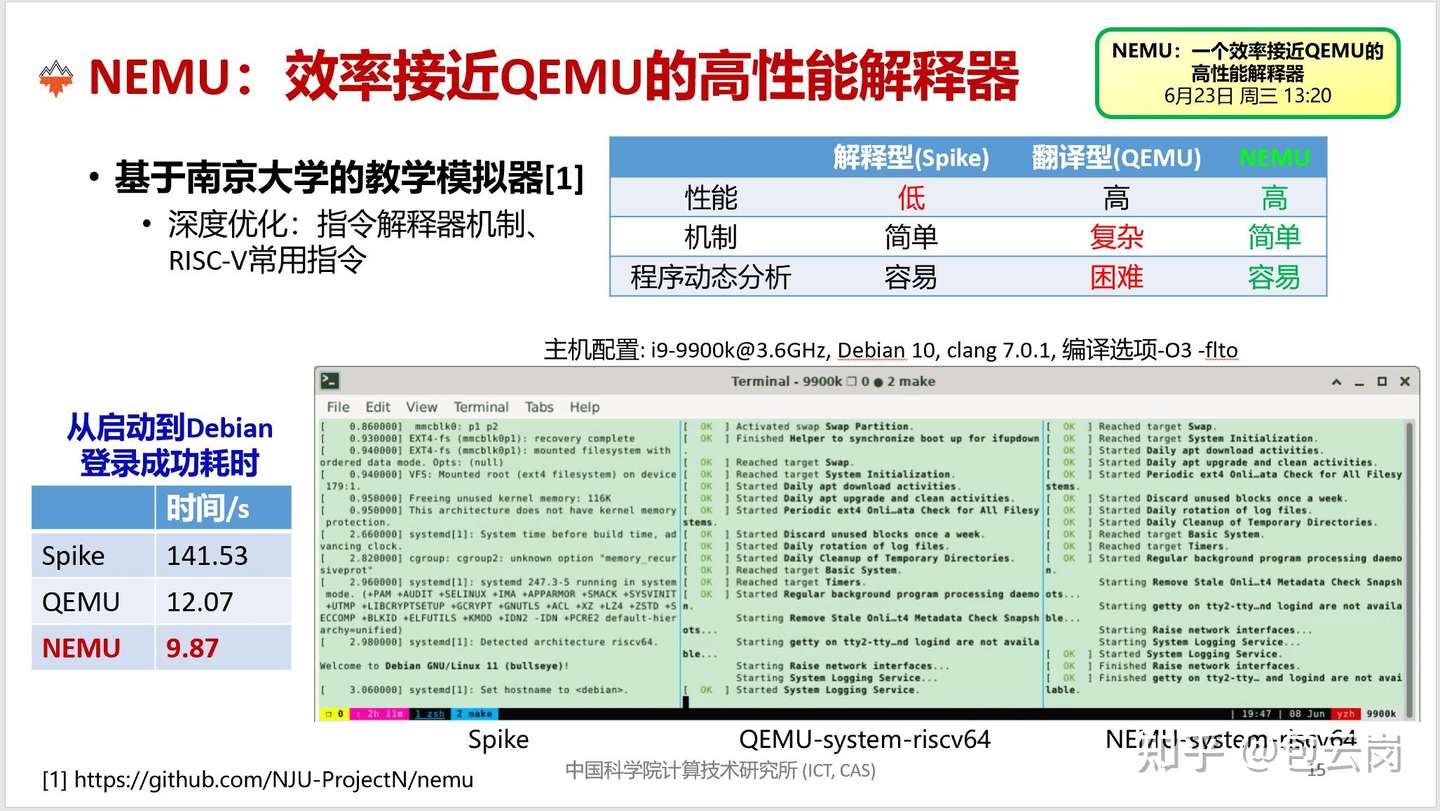

11. 下面举几个工具的例子。NEMU是由余子濠在南大本科时便开始开发的一款教学模拟器。在计算所读博期间,他凭借一人之力一直在持续改进和优化NEMU,使NEMU成为一个效率接近QEMU的高性能解释器——启动Debian甚至比QEMU还要快18.2%(9.87s vs. 12.07s)。

更重要的是NEMU是指令解释器,可以针对每一条指令进行动态分析;相比而言,QEMU的翻译粒度是基本块,无法跟踪每一条指令。事实上,NEMU的这种指令解释器机制,成为了香山开发中正确性验证框架Difftest的基础。

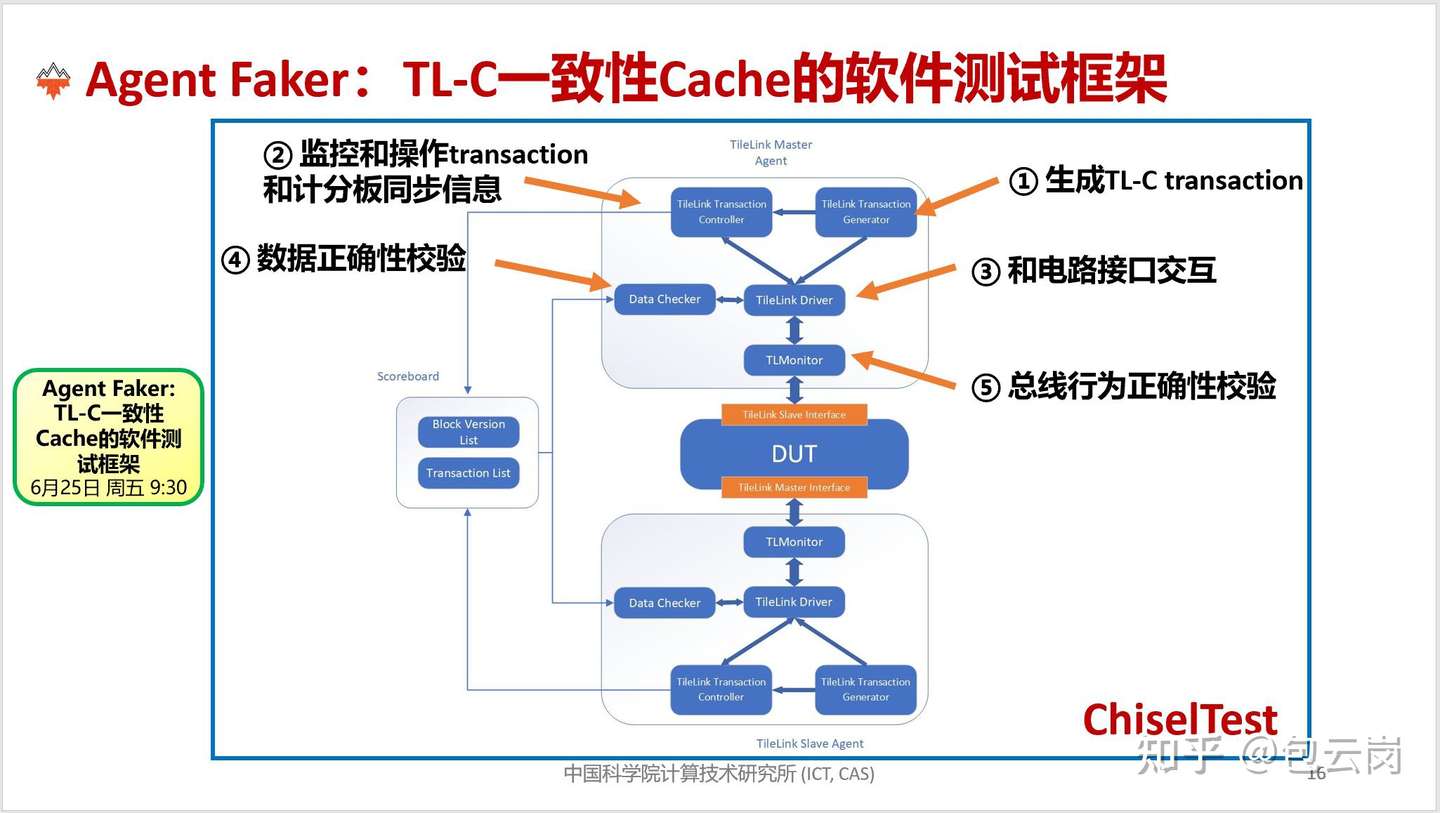

12. Cache是处理器中非常核心的模块,尤其是要支持一致性协议的Cache更为复杂。为此,小伙伴们开发了一套专门验证支持TileLink一致性协议的Cache模块测试框架Agent Faker,发现了好几个Cache模块的bug。

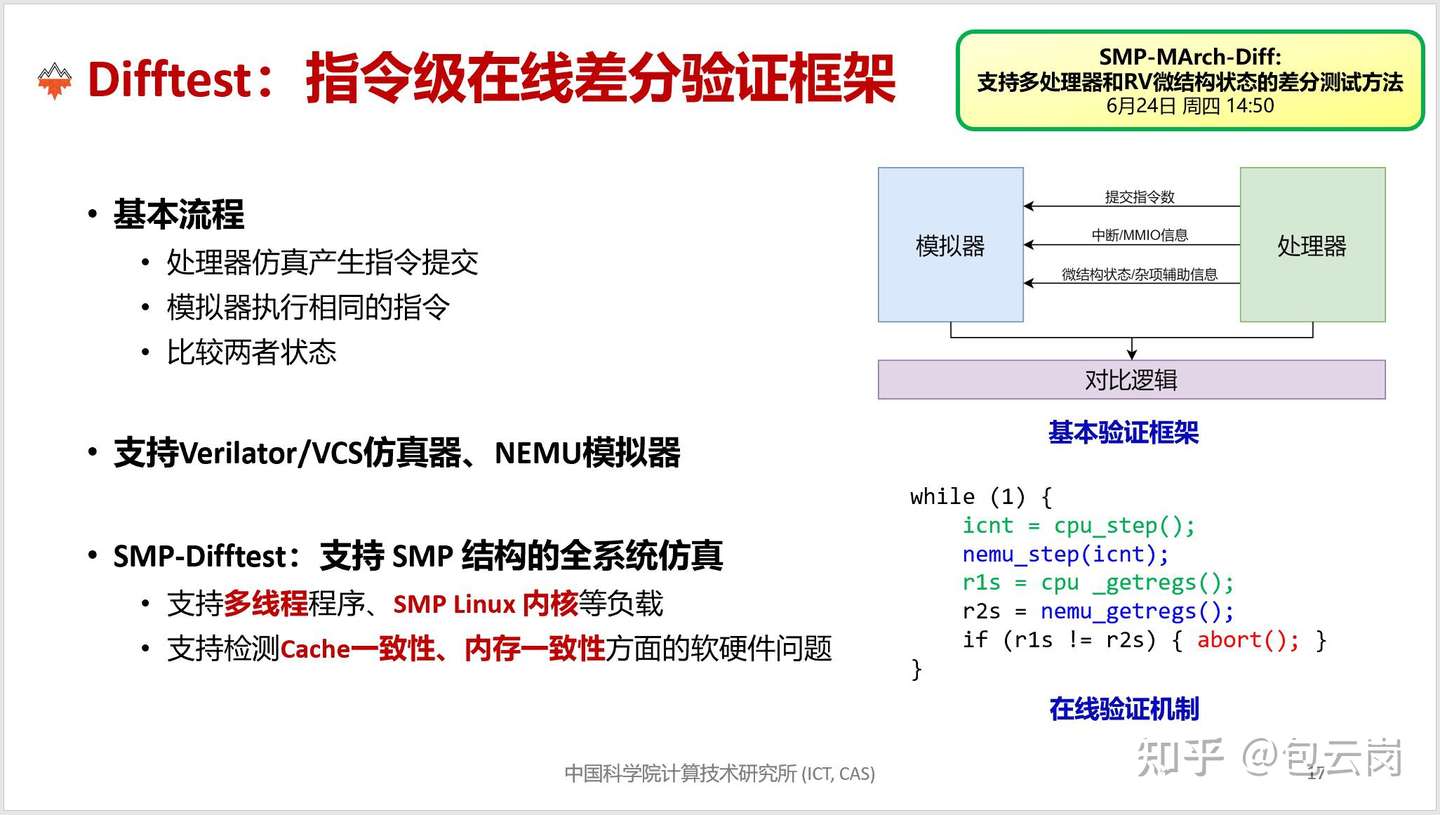

13. Difftest是一个基于NEMU的指令集在线差分验证框架。它的一端是模拟器,提供处理器执行的黄金标准;另一端是运行RTL的仿真器,在仿真过程中会将指令数、中断、MMIO、微结构状态等信息发送给NEMU进行比对,从而判断RTL实现的正确性。

Difftest最早是由余子濠实现,后来王凯帆进行优化,其中一个最重要的改进就是SMP-Difftest,支持多核SMP的全系统仿真,并且支持Cache一致性、内存一致性等需要软硬件协同的问题。

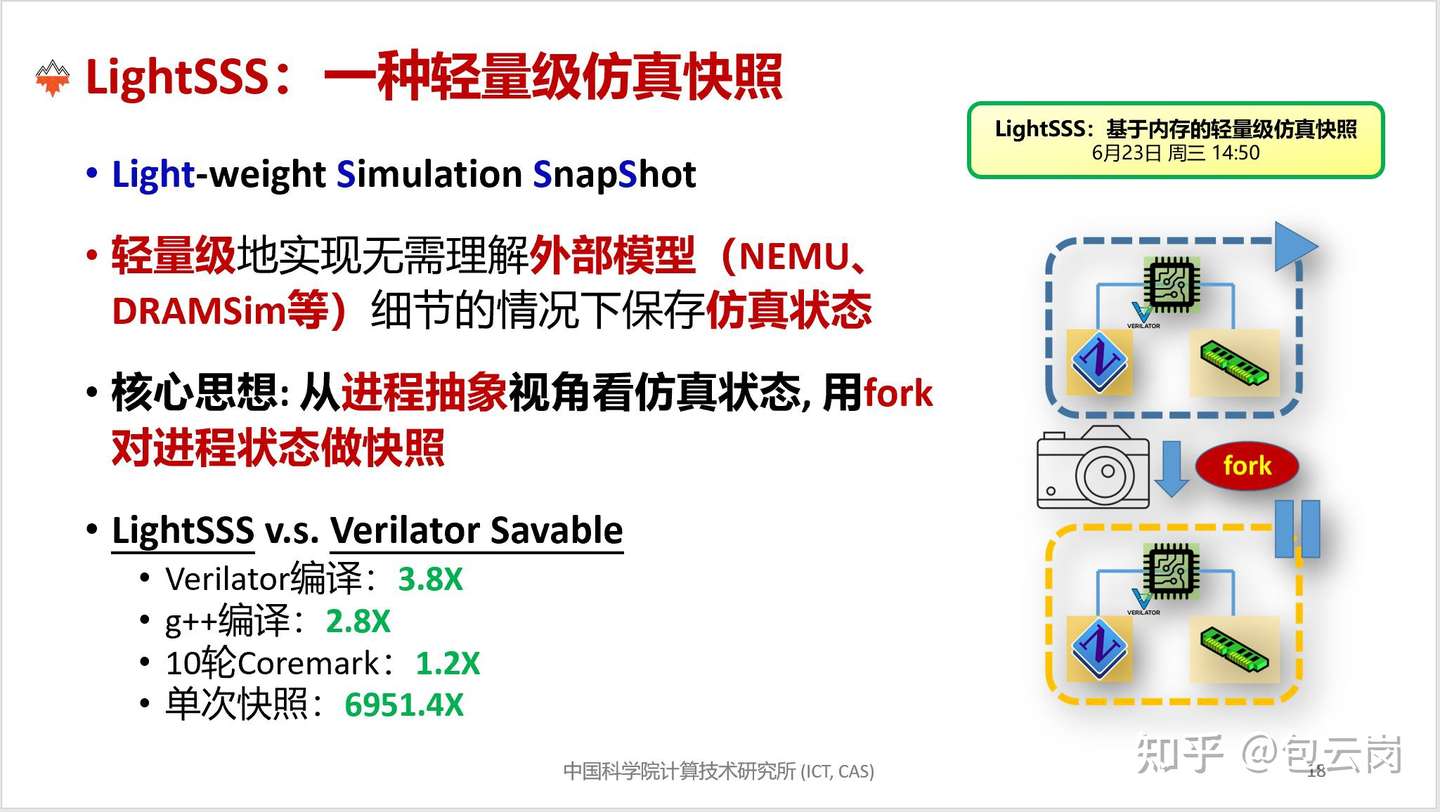

14. 如何快速捕捉、复现、定位bug是调试过程中非常关键的步骤,很多时间都是消耗在这个阶段。小伙伴们提出了一种创新的轻量级仿真快照技术——把整个仿真程序看成是一个进程,利用fork机制创建子进程。然后父进程继续执行,子进程暂停。当父进程出错时,则可以恢复到子进程进行调试。 LightSSS这个机制和Verilator仿真器自带的Savable机制相比,单次快照时间缩短了近7000倍!

15. 很多人质疑Chisel不方便调试。小伙伴们则充分利用了Chisel的可以自定义Firrtl Transform的特点,设计了一套新型的硬件敏捷调试栈,可将基于波形的调试转换为基于事件的调试。我们设计了一套工具,可以直接将高层语义新型从波形中提取出来,并进行可视化。为此,还专门设计了一个Xiang语言。

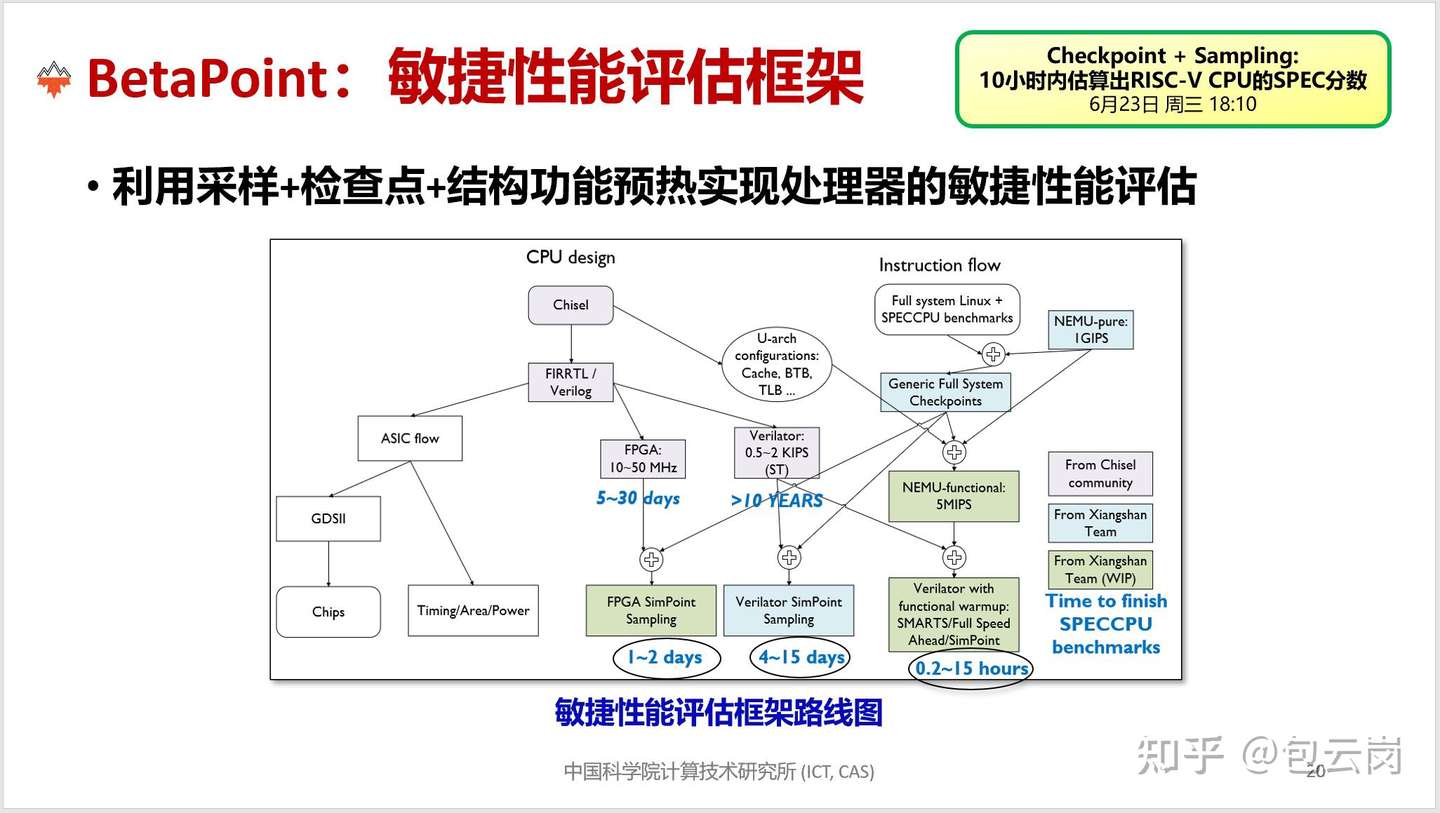

16. 处理器性能优化环节最关键是要快速准确地评估优化技术带来地性能收益。如果评估过程需要几天时间,那将会严重影响迭代优化效率。小伙伴们设计了一个敏捷性能评估框架BetaPoint,它利用了三个机制——Sampling机制、Generic Full System Checkpoint机制和Functional Warmup机制,实现了可以在10个小时内估算出处理器地SPEC分数。

17. 整个香山开发团队将在这次峰会上和大家分享22个技术报告。这些报告都是清一色的90后,很多都是95后:勾凌睿、胡博涵、金越、李昕、刘志刚、蔺嘉炜、王华强、王诲喆、王凯帆、徐易难、余子濠、张传奇、张发旺、张林隽、张紫飞、张梓悦、周耀阳、周意可、邹江瑞;此外还有多位参与香山开发的同学这次并没有投稿。这些小伙伴们在香山的开发过程中做出了不可替代的贡献。

四、香山未来如何发展?

18. 目前香山正在进行下一代架构“南湖”的开发,目标是今年年底流片,基于14nm工艺频率达到2GHz,SPECCPU分值达到10分/GHz。这是一个很有挑战的目标,需要对架构进行大幅度的优化改进。

前几天,小伙伴们专门去了一趟嘉兴南湖,研讨香山未来的发展。除了技术,我们再一次聚焦到流程与平台。此前构建的敏捷设计流程与平台支撑了20多人的开发团队,这远远不够。现在我们需要考虑的是该如何构建一套开源、开放、规范的开放流程,能支撑2000人的开源社区一起开发。

支持成千上万人一起开发开源软件,这已经有成功的经验。但是如何支持数千人一起开发开源处理器,目前还没有可以参考的案例,只能靠我们自己摸索。也期待各界专家给我们更多的指导和建议。

19. 我们有一个愿望——希望“香山”能存活30年;我们有一个约定——30年后再一起聚聚,到时再看看香山会变成什么样。但是,要实现这个愿望,还有很多很多问题和挑战需要去解决。

真诚地期待有更多伙伴加入香山的开发队伍!

20. 香山是在中科院计算所、鹏城实验室的支持下,通过中国开放指令生态(RISC-V)联盟联合业界企业一起开发一款开源高性能RISC-V处理器核,也得到了北京智源人工智能研究院的支持。在此,要特别感谢北京微核芯公司的资深专家给予香山的开发强力的支持,他们非常认同开源理念,也是第一家与香山联合开发的企业。很高兴“南湖”架构的开发有了更多的合作伙伴,感谢对香山的支持。

作者:包云岗

链接:https://www.zhihu.com/question/466393646/answer/1955410750

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

我要赚赏金

我要赚赏金