“重构”对于刚接触FPGA的人来说,可谓十分神秘,对于已经入门的人来说很“简单”,但是你真的了解FPGA的重构吗?

术语“重构”是指FPGA已经配置后的重新编程。FPGA的重构有两种类型:完全的和部分的。完全重构将整个FPGA重新编程,而部分重构只取代设计的一部分,设计的剩下部分仍正常工作。部分重构不被视为完全重构的特殊情况,因为两者基本相同。对FPGA执行部分重构通过使用与完全重构(JTAG、CAP或SelectMAP接口)相同的方法来进行,如上一节所述。比特流的结构对于完全和部分重构来说都是相同的。

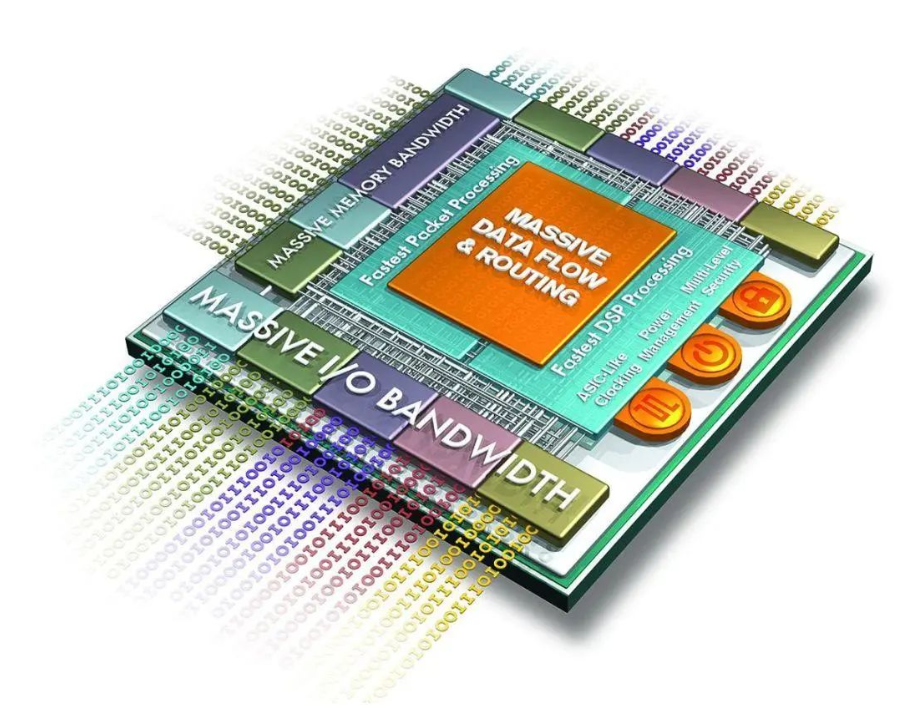

FPGA重构具有以下几个优点。它允许多个设计共享同一个FPGA架构,这反过来又降低了FPGA的面积、成本和系统复杂性。完全和部分重构为许多FPGA的创新应用程序提供了可能,否则,高昂的成本将影响应用程序实现。利用FPGA重构优势的一些应用如DSP音频或视频处理器等,它们根据用户输人,由包括集成深度包检测的通信控制器修改处理算法,以改变基于协议的数据包处理器。

很多工业和学术性的FPGA重构方面的研究不断产生有价值的应用、研究论文和学位论文。

虽然部分重构技术不是一项新功能,也不是主流的研究方向,但是设计和实现流程、工具支持甚至名词术语都在不断发展,用户界面越来越友好。最终目标是向FPGA开发者提供简单和透明的设计流程,无须详细了解配置逻辑和比特流结构。

部分重构是一项复杂过程,在设计实现、工具流程和重构本身的过程中充斥着多重挑战。面临的一个挑战是在FPGA配置的变化过程中,完成平滑切换而无须中断剩余设计功能或损害其完整性。而在完全重构过程中,FPGA架构和10不能保持在复位。另一项挑战是在改变过程中,防止设计的未改动部分进入无效状态。设计者必须正确界定和约束未改动和改动部分之间的接口。这样,FPGA物理实现工具才能进行配置并使用完全相同的布线资源。有三个部分重构流程可用于Xilinx FPGA基于差异的(difference based)、基于分层的(partition based)及使用动态重构端口。

基于差异的部分重构

基于差异的部分重构[2]最适合用于将小型设计转化为LUT方程、IO特征和BRAM中的内容。以下是一个简单的、基于差异的部分重构代码和流程举例,它可以运行在Xilinx开发板上。

//原始模块:当两个按钮都按下时,点亮LED

module top(input btn0,btnl,output led);

assign led=btn0&btnl;

endmodule//top

//部分重构模块:当两个按钮之一按下时,点亮LED

button is pressed

module top_pr(input btn0,btn1,output led);

assign led=btn0 | btn1;

endmodule//top_pr

#约朿文件:对两个设计都相同

NET "btnO" LOC= "A18" ;

NET "btnl" LOC= "H17" ;

NET "led" LOC= "AD21";

#实现LED功能的LUT被锁定到特定逻辑片中

#对于原始设计,LUT函数是btn0 & btn1

#对于部分重构设计,LUT函数是btn0|btn1

INST "led" AREA_GROUP="led";

AREA_GROUP "led" RANGE = SLICE_X65Y168:SLICE_X65Y168;

#bitgen命令用于产生部分重构比特流

#ActiveReconfig和Persist选项在配置变化期间置为全局复位

$bitgen -g ActiveReconfig:Yes -g Persist:Yes -r top_orig.bit

top_pr.ncd top_pr.bit

top_orig.bit:原始设计的比特流

top_pr.ncd:部分重构设计的布局布线后输出

top_pr.bit:得到的部分重构比特流结果

上面例子中基于差异的部分重构流程包括以下步骤:

(1)编译top模块。结果是比特流文件top_orig.bit。

(2)编译top_pr模块。结果是布局布线后文件top_pr.ncd。

(3)使用top.orig.bit比特流和top_pr.ncd,生成包含两个设计之间LED LUT方程差异的比特流。

基于分层的部分重构

与基于差异的重构不同,基于分层的部分重构流程支持重构大型部件FPGA设计。PlanAhead工具它提供了用于配置、实现和使用分层管理部分重构项目的集成环境。设计和实现流程的简要概述如下所示:

•FPGA开发者指定待配置的部分设计。

•在FPGA芯片上包含所需逻辑、嵌入式存储器、10和其他资源的区域。

•开发者定义覆盖该区域的所有可能设计变量。

•PlanAhead工具管理所有诸如编译设计的细节,包括管理多个网表、静态的和可重构的设计部分,执行DRC,并产生合适的比特流。

Xilinx应用提示XAPP883提供了使用部分重构的示例,以允许嵌入式PCI Exress接口模块的快速配置。

动态重构端口

改变Xilinx GTX收发器、混合模式时钟管理器(MMCM)和System Monitor原语设置的另一种方法,是使用动态重构端口(DRP)DRP提供了一个简单的用户逻辑接口,不需要更多地了解配置寄存器和比特流结构。例如,DRP允许输出时钟频率、相位和MMCM的占空比动态变化。

我要赚赏金

我要赚赏金