对于电子工程师而言,晶体和晶振是电路中不可或缺的关键元件,尤其在涉及到时钟信号和同步操作时。虽然两者在功能上有着相似之处,但在实际应用、电路设计以及布局布线等方面却存在着显著的区别。本文将详细对比晶体和晶振的属性、特点及应用场景,并为大家提供一些实用的布局和布线建议。

一、晶体与晶振的区别

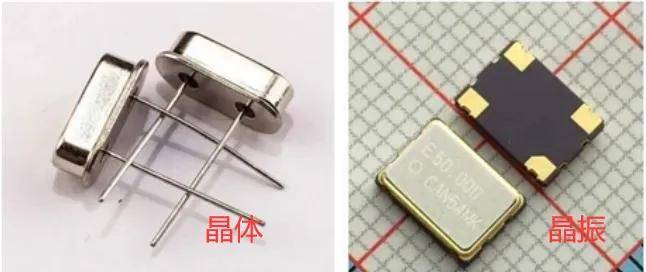

对于许多初入职场的硬件工程师来说,区分晶体(Crystal,简称XTAL)和晶振(Crystal Oscillator,简称XO)一直是个令人头疼的问题。以下是它们之间的主要差异:

01名称差异

晶体,通常简称为XTAL。

晶振,则被称为晶体振荡器,通常简称为XO。

02电源需求

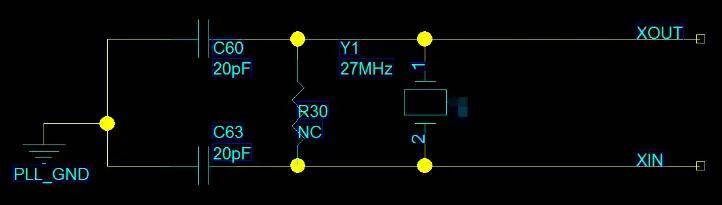

晶体本身无法振荡,需要依赖外部电路来产生时钟信号。使用晶体的芯片内部通常都集成了振荡电路。

晶振只需通电即可振荡并输出时钟信号,因为其内部已经集成了振荡电路。有时,晶体被称作无源晶体,而晶振被称作有源晶体,这种称呼方式凸显了两者在电源需求上的差异。

03输出方式

晶体没有电源引脚,但有输入和输出两个引脚。

晶振有电源引脚,但只有一个输出引脚。

04焊接方向

晶体没有方向性,可以正向或反向焊接,不影响使用。

晶振有方向,焊反则信号无法传至芯片。芯片上的XTAL_IN和XTAL_OUT是为内部振荡电路而标,与外部晶体无关。晶体无方向,正向、反向压电效应相同。晶振在芯片上通常只标XTAL_IN或XTALCLOCK,只需连对应芯片脚即可。

05引脚数量

两个引脚的一定是晶体。晶体只需要一个薄片状的水晶片即可振荡。因此,一个水晶片的两个引脚就是晶体的最少引脚数。小尺寸的晶体可能会带有两个地脚,用于将晶体的外壳接地屏蔽。

晶振至少有三个引脚,包括电源、地和时钟输出。如果再加上一个压控脚,就是四个引脚了。

二、晶体与晶振的应用场景有何不同?

1、晶体在电路中的应用

当考虑晶体在电路中的应用时,其主要作用是提供一个稳定、准确的时钟信号。这种信号对于同步和协调电子设备中的各种操作至关重要。

①、稳定的时钟源:晶体与芯片内部的振荡电路相结合,可以为整个系统提供一个稳定的时钟信号。这是大多数数字电路,特别是微处理器和存储器,所必需的。

②、低成本解决方案:由于晶体本身只需外部连接,不需要复杂的供电或控制线路,这使得它成为一个低成本的时钟解决方案。

③、紧凑电路设计:晶体通常很小,适合在紧凑的电路板设计中使用。

④、焊接无方向性:晶体没有特定的焊接方向,这降低了焊接错误的风险。

2、晶振在电路中的应用

晶振,与晶体相比,是一个更为完整的解决方案,因为它内部已经包含了必要的振荡电路。这使得它在某些应用中更为方便。

(1)简化电路设计:由于晶振内部已经有了振荡电路,所以只需要为其提供电源,它就会输出一个时钟信号。这简化了电路板设计。

(2)高精度和高稳定性:晶振通常能够提供比基本的晶体更高的精度和稳定性,特别是在宽温度范围内。

(3)易于控制:对于需要频率控制的应用,如使用压控振荡器(VCXO)的场景,晶振可以提供一个简单的接口来实现这一点。

(4)适应特定需求:对于需要宽温度范围或对精度要求高的应用,如GPS模块或高端处理器,温补晶振(TCXO)可以确保系统在不同环境下都能正常工作。

三、晶体的布局布线指南

1、晶体布局:

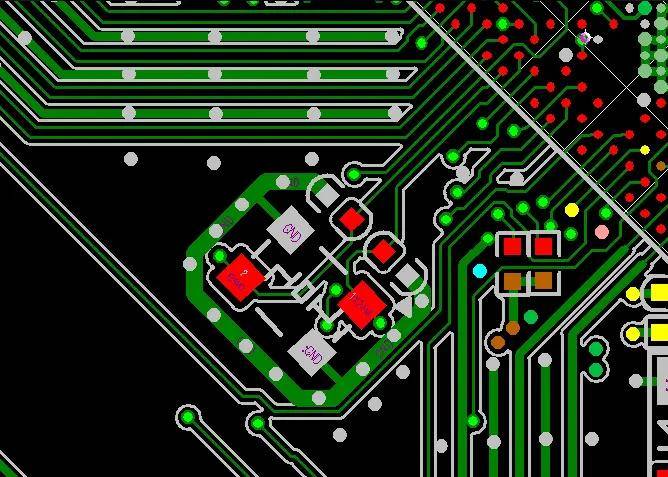

优先考虑紧凑布局,将元件优先放置在TOP层,尽量靠近IC管脚。

为降低寄生电容,当放置两个电容时,应确保分支长度最小化。

2、晶体布线:

优先选择TOP层进行布线。若需过孔,务必在附近设置回流过孔。

晶体信号线应走线成类差分形式。

加粗晶体信号线至8/10mil。

为减小寄生电容,通常将电容的地线扇出线宽加粗至18-22mil。

对时钟信号线实施包地处理,确保其稳定性。

在晶体附近设置屏蔽地过孔,以吸收和减少辐射噪声。

晶体下方禁止其他信号穿越,确保无干扰。

四、晶振的布局布线指南

1、晶振布局:

保持紧凑布局,优先考虑在TOP层进行布局。

将匹配电阻紧邻晶振放置,以减小电阻与晶振之间的信号延迟。

对于晶振电源,采用π型滤波以提高电源质量。在空间允许的情况下,滤波电容应优先放置在TOP层,并按照先大后小的顺序放置,以确保良好的滤波效果。

2、晶振布线:

为避免干扰,晶振本体下方禁止走线。在布线密度较大的情况下,至少确保晶振本体经过两个平面层的屏蔽后方可走线,以维护信号完整性。

晶振输出信号应按照严格的50欧姆阻抗进行走线。在换层处,务必打过回流地过孔,并与其他信号保持至少4W以上的间距,以减小串扰和电磁干扰。

在晶体附近设置屏蔽地过孔,以吸收和降低辐射噪声,提高电路的稳定性。

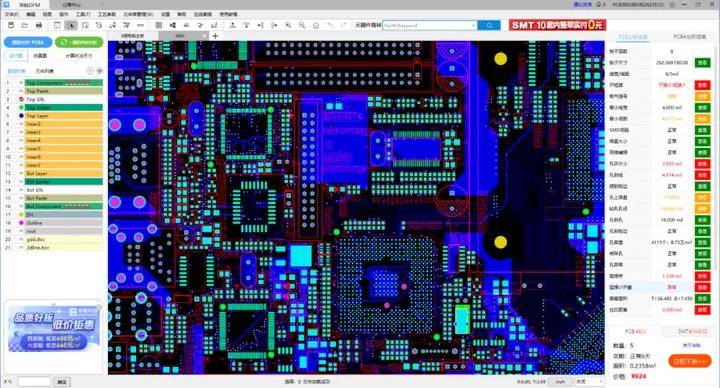

五、晶体晶振的PCB可制造性检查

在PCB布局和布线设计完成后,为确保顺利制造并避免潜在的可制造性问题,进行可制造性检查是至关重要的一步。特别是对于晶体和晶振的PCB设计,应对线宽、线距、孔距和孔径大小进行仔细检查。此外,还要核实孔环是否足够,以确保稳定的电气连接。

我们可以使用华秋DFM软件对晶体和晶振的PCB设计进行详细检查,包括最小线宽、线距,焊盘的大小以及是否漏引脚孔等多项工艺问题,还可以提前预防是否存在可制造性问题等。

结语:

希望通过本文的阐述,读者们能够对晶体和晶振有更清晰的认识,理解它们在电路中的重要作用,以及在设计和应用时需要注意的关键点。对于工程师来说,选择合适的元件并进行合理的布局和布线,是确保电路性能稳定、可靠的关键步骤。希望大家在实践中学以致用,不断积累经验,为电子行业的发展贡献自己的力量。