晶体管消除纹波方案主要是利用晶体管的特性来降低或消除电路中的纹波。

以下是一个基于晶体管的消除纹波方法:

主要依赖于自给偏压的射极跟随器电路,该电路利用了达林顿晶体管的特性。由于达林顿晶体管具有极高的放大倍数,这使得其基极的阻抗得以维持在一个相当高的水平。因此,只需使用较小的电容,就能有效地过滤掉100Hz的纹波。

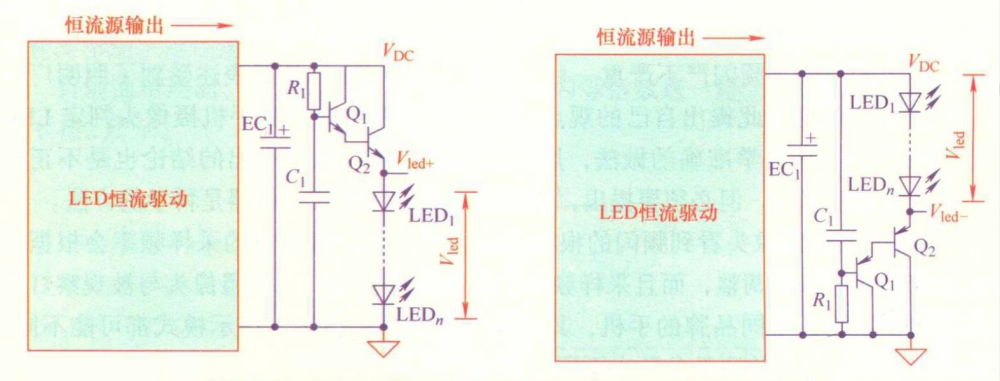

电路的实现有两种方式。一种是使用NPN型晶体管并将其放置在电源的正极(our端),另一种则是使用PNP型晶体管并将其放置在电源的负极(GND端)。通过添加这样的电路,我们可以将LED电流的纹波降低到非常低的水平,甚至接近0%。

显著优点是纹波降低效果显著,但也存在一些缺点。由于额外的晶体管被引入电路中,这会产生一定的功耗,从而降低了LED驱动器的效率。特别是在电流较大的情况下,这种功耗是不能被忽视的。功耗的大小可以通过公式 (Vout/2 + 1.2V) * Iled 来估计。

两个电路是一个自给偏压的射极跟随器,利用达林顿晶体管,由于放大倍数很高,可以使得基极的阻抗维持相当高,所以只需很小的电容即可过滤掉100Hz的纹波。这个电路可以使用NPN型晶体管放在our端来实现,或者使用PNP型晶体管放在GND端实现。加上这样的电路可将LED电流纹波降到非常低的值,甚至接近0%。这种消除LED电流纹波的电路的缺点是会有额外的功耗消耗在Q上因而降低了 LED 驱动器的效率。在Q,上的功耗可以由(Voupp/2 +1.2V)*Le来估计,可以看到,电流很大的话,Q,的功耗不可小视。

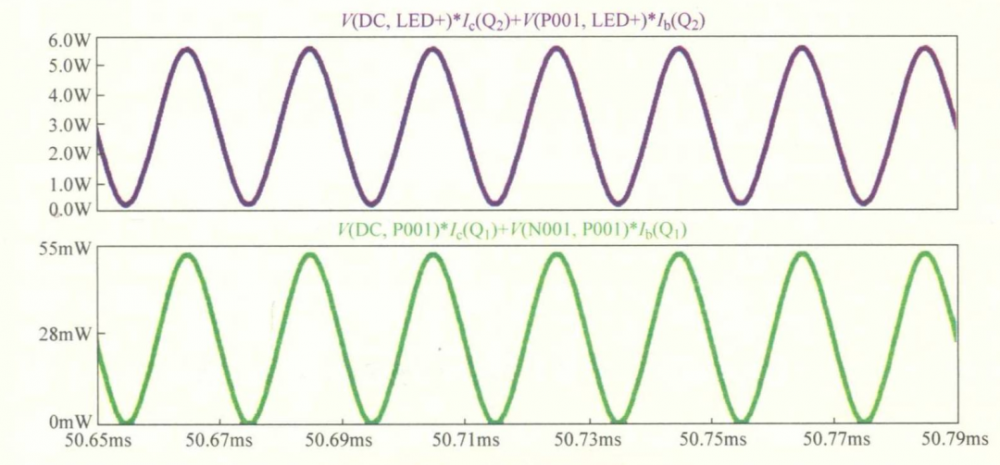

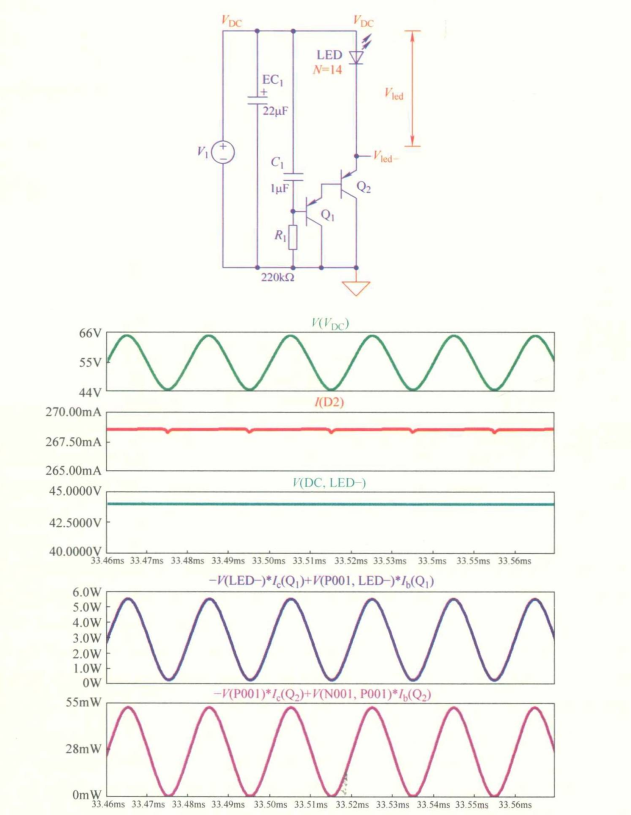

用一个实际的电路来进行测试,电路图如图所示,即为单级 PFC输出,经过Q, 和Q,组成的达林顿结构,再接到LED负载上面(此例为14个LED)。我们先来看仿真结果,如图1-125所示,可以看到,上通过仿真人为叠加100Hz的工频纹波,而在LED上面,基本上看到纹波幅度大为降低,同时LED中的电流纹波水平也接近为0,而实际搭建的测试电路,通过示波器测量出来的结果和仿真结果一致,说明此电路是实际有效的。同时通过仿真我们可以看到Q和Q,的功耗水平如图 1-126 所示,Q,的功率相对来Q,来说很小,这是因为Q, 主要是起驱动作用,而Q,作为线性调整管来吸收掉所有的纹波电流产生的功耗。

实际测试电路波形(左)和仿真电路波形(右)结果比较

Q1,Q2的功耗:

如果采用PNP的晶体管也可以实现类似功能,具体如下:

采用 PNP 型晶体管搭建去纹波电路的仿真电路及波形

不管是哪种形式,由于Q,是作为动态调整管来吸收工频纹波,Q,的高功耗制约了此类电路的应用,使得纹波消除电路这样的解决方案通常仅适用于较低功率的系统中,或是高压小电流输出型电源中。当然对于此类电路,相关公司已申请专利,具体可以阅读参考文献。

总结:

晶体管消除纹波方案具有一系列优点和缺点,以下是对这些优缺点的详细分析:

优点:

纹波抑制效果好:该方案能够有效地降低或消除电路中的纹波,尤其对于100Hz等低频纹波有显著的抑制作用。通过合理设计电路和选用合适的晶体管,可以实现接近0%的纹波降低率,显著提高电路的稳定性和性能。

简单实用:晶体管消除纹波方案相对简单,容易实现。通过使用达林顿晶体管等特定类型的晶体管,可以在不增加太多复杂性的情况下实现有效的纹波抑制。

适用范围广:该方案不仅适用于LED驱动器,还可以应用于其他需要降低纹波的电路。无论是电源电路还是信号处理电路,只要存在纹波问题,都可以考虑采用晶体管消除纹波方案。

缺点:

增加功耗:引入晶体管进行纹波抑制会增加一定的功耗。由于晶体管在工作时会产生热量损失,这会导致LED驱动器的效率降低。特别是在高电流或长时间工作的条件下,功耗问题可能更为突出。

成本增加:为了实现有效的纹波抑制,可能需要使用多个晶体管或其他组件,这会增加电路的成本。此外,为了优化电路性能,可能还需要进行额外的设计和测试工作,进一步增加了成本。

设计复杂性:虽然晶体管消除纹波方案相对简单,但在实际应用中仍需要一定的设计技巧和经验。不正确的电路设计或组件选择可能导致纹波抑制效果不佳或引入其他问题。因此,对于不具备相关经验的工程师来说,可能会增加设计难度。

我要赚赏金

我要赚赏金