在MOS管开关电路中,上拉电阻和下拉电阻的主要区别在于它们的作用方向和应用场景。

以下是详细的区别说明:

一、作用方向

上拉电阻:

将信号线通过一个电阻连接到高电平(VCC),以确保在电路未激活或信号未定义时,信号线保持在高电平状态。

应用场景:常用于需要信号线默认处于高电平状态的场景,或者当输出高电平不足时,利用上拉电阻强制拉高电平。

下拉电阻:

作用方向:将信号线通过一个电阻连接到低电平(如GND),以确保在电路未激活或信号未定义时,信号线保持在低电平状态。

应用场景:常用于需要信号线默认处于低电平状态的场景,或者当输出低电平不够低时,利用下拉电阻将低电平拉低。

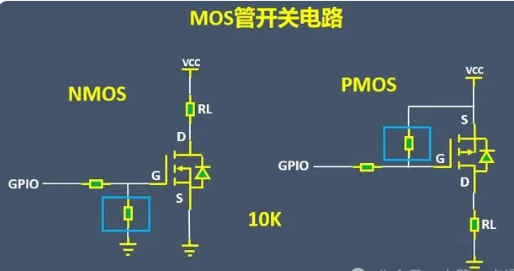

二、在MOS管开关电路中的具体作用

上拉电阻:

在PMOS管中的应用:在PMOS管的栅极加一个上拉电阻,可以确保在上电时给栅极一个确定的电平,防止静电击穿,并提供放电路径。

防止静电击穿:由于栅极结电容的存在,PMOS管容易积累静电电荷,上拉电阻可以固定电平,防止静电击穿。

提供放电路径:在断电时,上拉电阻为GS间的寄生电容提供放电路径,使MOS管能快速关闭。

下拉电阻:

在NMOS管中的应用:在NMOS管的栅极加一个下拉电阻,同样可以确保在上电时给栅极一个确定的电平,防止静电击穿,并提供放电路径。

防止静电击穿:与PMOS管类似,NMOS管也容易受到静电电荷的影响,下拉电阻可以固定电平,防止静电击穿。

提供放电路径:在断电时,下拉电阻为GS间的寄生电容提供放电路径,确保MOS管能快速关闭。

三、看图

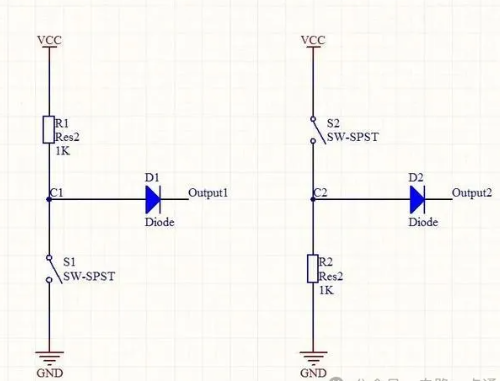

在实际电路中我们会经常遇到器件输出电压幅度不足的情况,如果前级只能输出0V-3V的电平,而后级系统需要一个0V-5V的高电平或者低电平,就可以利用上拉电阻,强制拉高前级的输出电压,但是这种方式只能够将电压拉到3V-5V之间。

上拉电阻与下拉电阻在MOS管开关电路中的作用

确定栅极电平

上拉电阻:在PMOS管栅极加上拉电阻,可以确保在电路未激活或上电瞬间,栅极被稳定地拉至高电平(如VCC),从而避免PMOS管意外导通。

下拉电阻:在NMOS管栅极加下拉电阻,则确保栅极在电路未激活或上电瞬间被稳定地拉至低电平(如GND),防止NMOS管意外导通。

防止静电击穿

MOS管的栅极非常敏感,容易受到静电电荷的影响而发生击穿。通过在上电时给栅极一个确定的电平(无论是高电平还是低电平),上拉电阻和下拉电阻都能有效减少静电电荷的积累,从而降低静电击穿的风险。

提供放电路径

当电路断电或MOS管需要关闭时,栅极与源极(GS)之间的寄生电容需要被放电。上拉电阻和下拉电阻分别为PMOS和NMOS管提供了这样的放电路径,确保MOS管能够迅速且可靠地关闭。

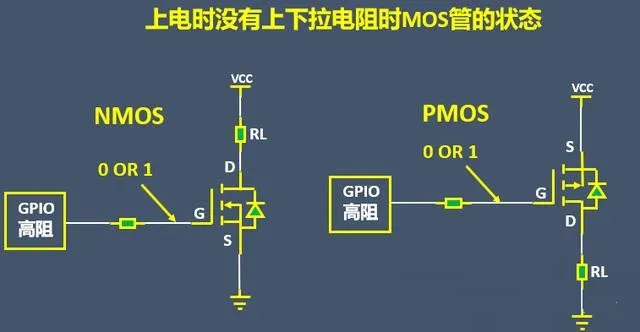

应对上电时的高阻态

MOS管在上电初期可能会呈现高阻态,此时栅极电平不稳定,容易受到外部干扰(如高频噪声)。通过加上拉电阻或下拉电阻,可以确保栅极在上电时即处于确定的电平状态,从而避免MOS管因外部干扰而意外导通或烧毁。

电阻阻值的选择

电阻的阻值通常根据具体电路的需求进行选择。在MOS管开关电路中,上拉电阻和下拉电阻的阻值一般在几千欧姆到几十千欧姆之间,常见的如10KΩ。阻值的选择需要综合考虑电路的功耗、信号完整性以及MOS管的开关速度等因素。

在呈现高阻态时容易积累一些静电电荷,在一定程度时会在GS之间形成高电压,MOS管容易击穿并损坏,也需要电阻来进行固定电平。

三、总结

在MOS管开关电路中,上拉电阻和下拉电阻的主要区别在于它们的作用方向和应用场景。上拉电阻用于将信号线拉至高电平,而下拉电阻用于将信号线拉至低电平。在PMOS管和NMOS管中,它们分别起到确保栅极电平稳定、防止静电击穿和提供放电路径的作用。这些电阻的阻值通常根据具体电路的需求进行选择,一般在10KΩ左右。