上下拉电阻

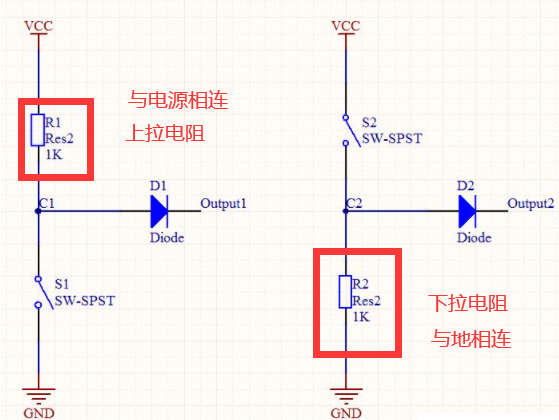

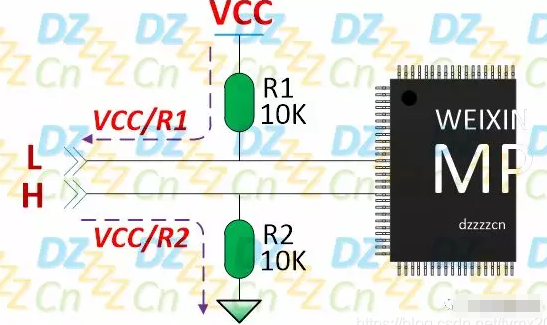

上拉是将不确定的信号通过一个电阻钳制在一个高电平。

下拉是将不确定的信号通过一个电阻与地相连,固定在低电平。

模块端口的上拉或下拉电阻,具有限流、提高驱动能力、防静电等作用,可以有效保护电路。

当信号方向为输入且没有输入信号(高阻态)时,上拉会将该信号的逻辑值置为 1,下拉会将该信号的逻辑值置为 0。

原理:

Verilog 提供了为信号设置上、下拉电阻的逻辑门单元,多用于模块端口信号。

此类门单元没有输入,只有输出。关键字如下:

pullup(设置上拉) pulldown(设置下拉)

例化调用时,只需填写需要设置上下拉电阻的信号即可。

实例的名字也可以不指定。

pullup p1 (IN1); pulldown (OUTX);

在数字电路设计中,上拉门(pull-up)和下拉门(pull-down)是两种常见的配置,用于确保未驱动的输入或输出有一个确定的电平状态。这些配置通常通过使用电阻来实现,确保在没有其他信号驱动的情况下,信号线会被拉到一个已知的高电平(上拉)或低电平(下拉)。

上拉(Pull-Up)

上拉门使用一个电阻将信号线连接到电源(通常是VCC或高电平),从而在没有其他信号驱动该线时,使其保持在高电平。这在许多情况下非常有用,比如在按钮开关电路中,当按钮未被按下时,确保输入信号是高电平。

下拉(Pull-Down)

下拉门使用一个电阻将信号线连接到地(通常是GND或低电平),从而在没有其他信号驱动该线时,使其保持在低电平。这种配置在需要默认低电平输入的情况下非常有用。

实例说明

在你的例子中,pull_gate 是一个代表上拉或下拉门的元件,而 instance_name 是这个元件的实例名,OutputA 是这个门的输出端口。

实例:

pullup u0pullup(core_pwr);

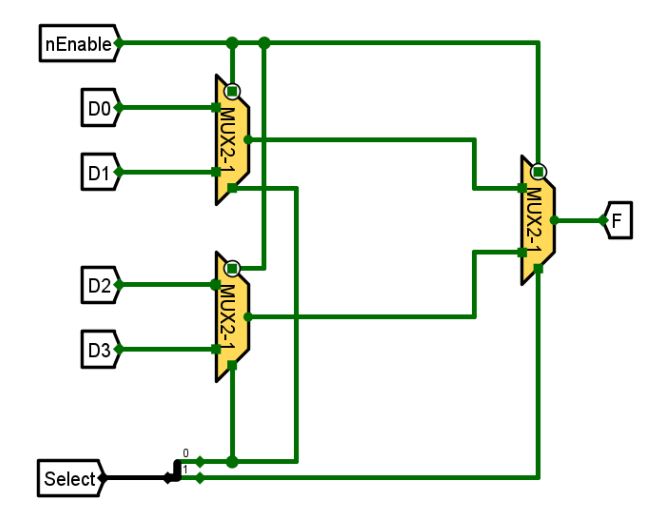

4选1多路选择器

4选1多路选择器(4-to-1 Multiplexer)是一种数字电路,它可以从四个输入信号中选择一个输出,选择哪个输入信号由两个选择信号(SEL1 和 SEL0)决定。这两个选择信号通常编码为二进制数,以表示四个不同的选择状态。

选择信号编码

对于两个选择信号 SEL1 和 SEL0,它们可以组合成四种状态,分别对应四个输入信号的选择:

SEL1 = 0, SEL0 = 0:选择输入 A SEL1 = 0, SEL0 = 1:选择输入 B SEL1 = 1, SEL0 = 0:选择输入 C SEL1 = 1, SEL0 = 1:选择输入 D

4选1多路选择器的表达式

在逻辑表达式中,4选1多路选择器可以表示为:

F=(SEL1⋅SEL0⋅A)+(SEL1⋅SEL0⋅B)+(SEL1⋅SEL0⋅C)+(SEL1⋅SEL0⋅D)

⋅ 表示逻辑与(AND)操作,+ 表示逻辑或(OR)操作,而表示逻辑非(NOT)操作。

举例:

参考图

门级建模与行为级建模的对比

门级建模:

在门级建模中,你需要使用基本的逻辑门(如与门、或门、非门)来实现上述逻辑表达式。这通常涉及到多个逻辑门的级联和连接,使得设计变得相对复杂和繁琐。例如,你需要为每个与操作实现一个与门,为每个或操作实现一个或门,并且可能还需要非门来生成反相信号。

行为级建模:

相比之下,行为级建模通常使用高级描述语言(如Verilog或VHDL)中的条件语句(如if-else或case语句)来直接描述选择器的行为。这种方法更加直观和简洁,因为它直接反映了选择器的工作原理,而不需要关心底层逻辑门的实现细节。例如,在Verilog中,你可以使用如下的行为描述:

module mux4to1 (

input wire A, B, C, D,

input wire SEL1, SEL0,

output reg F

);

always @(*) begin

case ({SEL1, SEL0})

2'b00: F = A;

2'b01: F = B;

2'b10: F = C;

2'b11: F = D;

default: F = 1'b0; // 可选的默认情况,通常不需要,因为SEL1和SEL0已经覆盖了所有情况

endcase

end

endmodule行为级建模如下:

module mux4to1_behavior(

input A, B, C, D ,

input S0, S1,

output F );

assign F = {S1, S0} == 2'b00 ? A :

{S1, S0} == 2'b01 ? B :

{S1, S0} == 2'b10 ? C :

{S1, S0} == 2'b11 ? D : 0 ;

endmodule总结:

上下拉电阻在数字电路设计中扮演着重要角色,它们通过电阻将不确定的信号钳制在高电平(上拉)或低电平(下拉),确保未驱动的输入或输出有确定的电平状态。

Verilog等硬件描述语言提供了设置上下拉电阻的逻辑门单元,这些门单元没有输入,只有输出,简化了电路设计。

4选1多路选择器是一种能从四个输入信号中选择一个输出的数字电路,选择由两个选择信号决定。在逻辑表达式中,这可以通过逻辑门实现,但门级建模相对繁琐。

行为级建模使用条件语句直接描述选择器行为,更加直观简洁。

我要赚赏金

我要赚赏金