QUADSPI介绍

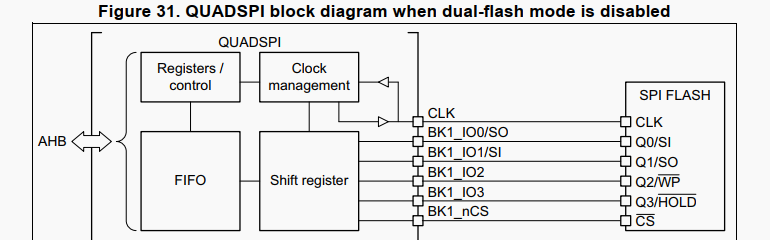

QUADSPI 是一种专用的通信接口,连接单、双或四(条数据线) SPI Flash 存储介质。该接

口可以在以下三种模式下工作:

①间接模式:使用 QUADSPI 寄存器执行全部操作。

②状态轮询模式:周期性读取外部 Flash 状态寄存器,而且标志位置 1 时会产生中断(如擦除或烧写完成,会产生中断)。

③内存映射模式:外部 Flash 映射到微控制器地址空间,从而系统将其视作内部存储器。

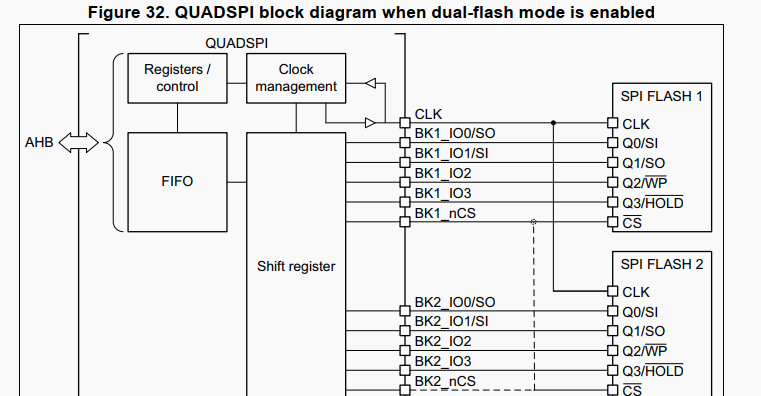

采用双闪存模式时,将并行访问两个 Quad-SPI Flash,可同时发送/接收 8 位数据,吞吐量和容量均可提高二倍。

硬件连接

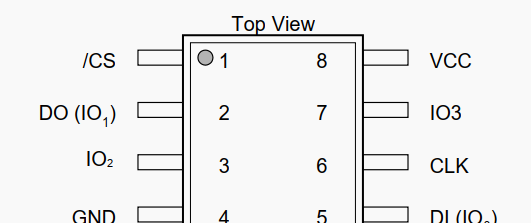

Nor Flash以W25Q64为例:

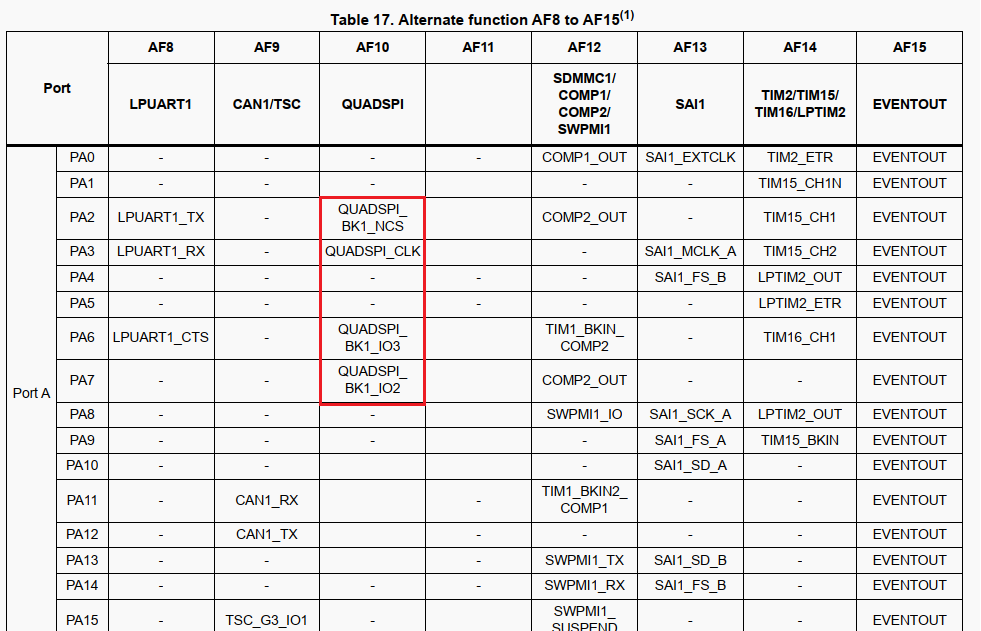

双闪存模式不是所有含有QUADSPI的MCU都支持的,因为使用双闪存模式需要更多的IO口,对于一些IO口较少的MCU型号就没有那么多引脚可以复用为QUADSPI,

具体可以看一下MCU的数据手册,确认一下是不是能连接第二个Flash。另外使用QUADSPI的话片选引脚就不能像标准SPI一样可以随意指定引脚,必须要使用指定的引脚,这个时候片选是由硬件完成的。

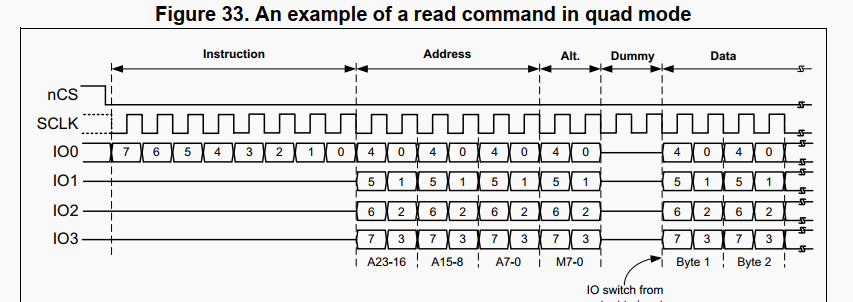

指令阶段

这一阶段,将在 QUADSPI_CCR[7:0] 寄存器的 INSTRUCTION 字段中配置的一条 8 位指令发送到 Flash,指定待执行操作的类型。

尽管大多数 Flash 从 IO0/SO 信号(单线 SPI 模式)只能以一次 1 位的方式接收指令,但指令阶段可选择一次发送 2 位(在双线 SPI 模式中通过 IO0/IO1)或一次发送 4 位

(在四线SPI 模式中通过 IO0/IO1/IO2/IO3)。这可通过 QUADSPI_CCR[9:8] 寄存器中的 IMODE[1:0]

字段进行配置。

若 IMODE = 00,则跳过指令阶段,命令序列从地址阶段(如果存在)开始。

地址阶段

在地址阶段,将1-4 字节发送到Flash,指示操作地址。待发送的地址字节数 在QUADSPI_CCR[13:12] 寄存器的 ADSIZE[1:0] 字段中进行配置。在间接模式和自动轮询模式下,

待发送的地址字节在 QUADSPI_AR 寄存器的 ADDRESS[31:0] 中指定。在内存映射模式下,则通过 AHB(来自于 Cortex® 或 DMA)直接给出地址。

地址阶段可一次发送 1 位(在单线 SPI 模式中通过 SO)、 2 位(在双线 SPI 模式中通过 IO0/IO1)或 4 位(在四线 SPI 模式中通过 IO0/IO1/IO2/IO3)。这可通过QUADSPI_CCR

[11:10] 寄存器中的 ADMODE[1:0] 字段进行配置。

若 ADMODE = 00,则跳过地址阶段,命令序列直接进入下一阶段(如果存在)。

交替字节阶段

在交替字节阶段,将 1-4 字节发送到 Flash,一般用于控制操作模式。待发送的交替字节数在 QUADSPI_CCR[17:16] 寄存器的 ABSIZE[1:0] 字段中进行配置。待发送的字节在QUADSPI_ABR 寄存器中指定。

交替字节阶段可一次发送1位(在单线 SPI 模式中通过 SO)、2位(在双线 SPI 模式中 通 过 IO0/IO1)或4位(在四线 SPI 模 式 中 通 过 IO0/IO1/IO2/IO3)。这可通过QUADSPI_CCR[15:14]

寄存器中的 ABMODE[1:0] 字段进行配置。

若 ABMODE = 00,则跳过交替字节阶段,命令序列直接进入下一阶段(如果存在)。

交替字节阶段存在仅需发送单个半字节而不是一个全字节的情况,比如采用双线模式并且仅使用两个周期发送交替字节时。在这种情况下,固件可采用四线模式 (ABMODE = 11) 并发送一个字节,

方法是 ALTERNATE 的位 7 和 3 置“1”( IO3 保持高电平)且位 6 和 2 置“0”( IO2 线保持低电平)。此时,半字节的高 2 位存放在 ALTERNATE 的位 4:3,低 2位存放在位 1 和 0 中。例如,

如果半字节 2 (0010) 通过IO0/IO1 发送,则 ALTERNATE 应设置为 0x8A (1000_1010)。

空指令周期阶段

在空指令周期阶段,给定的 1-31 个周期内不发送或接收任何数据,目的是当采用更高的时钟频率时,给Flash留出准备数据阶段的时间。这一阶段中给定的周期数在QUADSPI_CCR[22:18] 寄存器

的 DCYC[4:0] 字段中指定。在 SDR 和 DDR 模式下,持续时间被指定为一定个数的全时钟周期。

若 DCYC 为零,则跳过空指令周期阶段,命令序列直接进入数据阶段(如果存在)。

空指令周期阶段的操作模式由 DMODE 确定。

为确保数据信号从输出模式转变为输入模式有足够的“周转”时间,使用双线和四线模式从Flash 接收数据时,至少需要指定一个空指令周期。

数据阶段

在数据阶段,可从 Flash 接收或向其发送任意数量的字节。

在间接模式和自动轮询模式下,待发送/接收的字节数在 QUADSPI_DLR 寄存器中指定。

在间接写入模式下,发送到 Flash 的数据必须写入 QUADSPI_DR 寄存器。在间接读取模式下,通过读取 QUADSPI_DR 寄存器获得从 Flash 接收的数据。

在内存映射模式下,读取的数据通过 AHB 直接发送回 Cortex 或 DMA。

数据阶段可一次发送 / 接收 1 位(在单线 SPI 模式中通过 SO)、 2 位(在双线 SPI 模式中通过 IO0/IO1)或 4 位(在四线 SPI 模式中通过 IO0/IO1/IO2/IO3)。

这可通过QUADSPI_CCR[15:14] 寄存器中的 ABMODE[1:0] 字段进行配置。

若 DMODE = 00,则跳过数据阶段,命令序列在拉高 nCS 时立即完成。这一配置仅可用于仅间接写入模式。

QUADSPI主要信号接口协议模式

主要的信号模式为3种,单线SPI,就是标准SPI;双线SPI,比如数据阶段使用两条信号线;还有一种四线SPI,比如数据阶段使用四条信号线。双线SPI和四线SPI时信号线为双向IO,

也就是说要么类似于标准SPI的MISO,要么类似于标准SPI的MOSI,工作方式为半双工。

单线SPI模式

传统 SPI 模式允许串行发送/接收单独的 1 位。在此模式下,数据通过 SO 信号(其 I/O 与IO0 共享)发送到 Flash。从 Flash 接收到的数据通过 SI(其 I/O 与 IO1 共享)送达。

通过将( QUADSPI_CCR 中的) IMODE/ADMODE/ABMODE/DMODE 字段设置为 01,可对不同的命令阶段分别进行配置,以使用此单个位模式。

在每个已配置为单线模式的阶段中:

①IO0 (SO) 处于输出模式

②IO1 (SI) 处于输入模式(高阻抗)

③IO2 处于输出模式并强制置“0”(以禁止“写保护”功能)

④IO3 处于输出模式并强制置“1”(以禁止“保持”功能)

若 DMODE = 01,这对于空指令阶段也同样如此。

双线SPI模式

在双线模式下,通过 IO0/IO1 信号同时发送/接收两位。

通过将 QUADSPI_CCR 寄存器的 IMODE/ADMODE/ABMODE/DMODE 字段设置为 10,可对不同的命令阶段分别进行配置,以使用双线 SPI 模式。

在每个已配置为双线模式的阶段中:

①IO0/IO1 在数据阶段进行读取操作时处于高阻态(输入),在其他情况下为输出

②IO2 处于输出模式并强制置“0”

③IO3 处于输出模式并强制置“1”

在空指令阶段,若 DMODE = 01,则 IO0/IO1 始终保持高阻态。

四线SPI模式

在四线模式下,通过 IO0/IO1/IO2/IO3 信号同时发送/接收四位。

通过将 QUADSPI_CCR 寄存器的 IMODE/ADMODE/ABMODE/DMODE 字段设置为 11,可对不同的命令阶段分别进行配置,以使用四线 SPI 模式。

在每个已配置为四线模式的阶段中, IO0/IO1/IO2/IO3 在数据阶段进行读取操作时均处于高阻态(输入),在其他情况下为输出。

在空指令阶段中,若 DMODE = 11,则 IO0/IO1/IO2/IO3 均为高阻态。

IO2 和 IO3 仅用于 Quad SPI 模式,如果未配置任何阶段使用四线 SPI 模式,即使 QUADSPI激活,对应 IO2 和 IO3 的引脚也可用于其他功能。

使用QUADSPI操作W25Q64

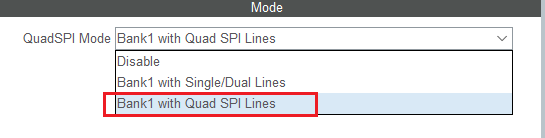

使用STM32CubeMX配置生成QSPI代码,以四线SPI为例。

模式选择:

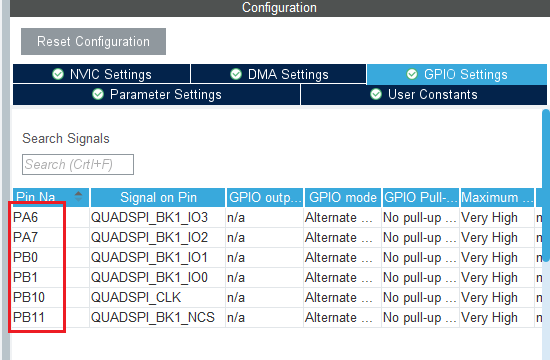

引脚选择:

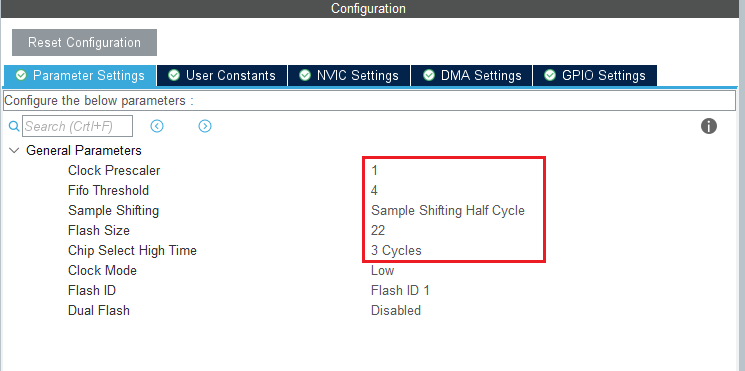

QSPI参数设置:

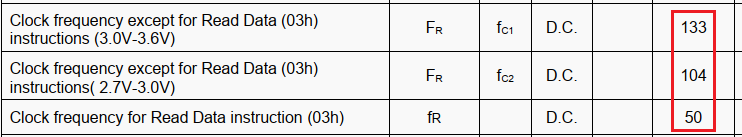

ClockPrescaler:该参数定义基于 AHB 时钟生成 CLK 所用的分频系数(值 + 1),QSPI是挂载在AHB总线上的,AHB时钟频率为80MHz,设置为1时,

QPSI的速率为40MHz(80÷2)。W25Q64除读操作外支持的最大速率是133Mhz,跟电压有关系;读操作最大为50Mhz。这里指的是使用标准SPI的速率,

使用双线SPI和四线SPI时的速率是相对于单线SPI来说的。

FifoThreshold:该参数定义在间接模式下 FIFO 中将导致 FIFO 阈值标志(FTF, QUADSPI_SR[2])置 1 的字节数阈值。

在间接模式下,若达到 FIFO 阈值,或从 Flash 读取完成后, FIFO 中留有数据时,FTF置 1。只要阈值条件不再为“真”,FTF就自动清零。

在自动轮询模式下,每次读取状态寄存器时,FTF即置 1 ;读取数据寄存器时,FTF清零。

SampleShifting:默认情况下, QUADSPI 在 Flash 驱动信号后过半个 CLK 周期才对 Flash 驱动的数据采样。在外部信号延迟时,这有利于推迟数据采样。

来源: 整理文章为传播相关技术,网络版权归原作者所有,如有侵权,请联系删除。