我使用的为EP2C8Q208芯片

其与EP2C5Q208芯片的区别主要为四个IO口,我的少四个。具体如下:

| 管脚号 | 5Q208 | 8Q208 |

| 32 | I/O | VccINT |

| 120 | I/O | VccINT |

| 36 | I/O | GND |

| 119 | I/O | GND |

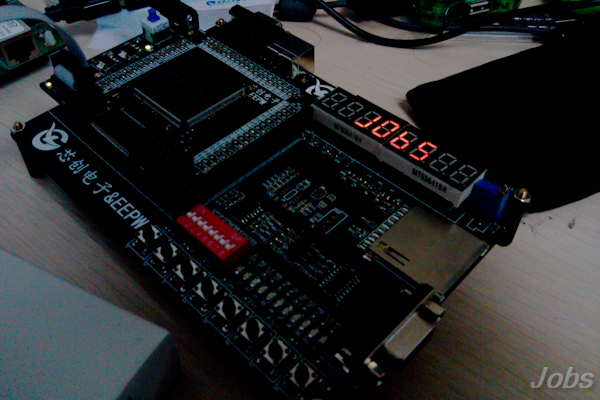

数码段码管在实际生活中应用广泛,主要因为其价格低廉,性能稳定,在低成本的应用项目里被广泛采用。今天这个实验为动态扫描式操作数码管,为以后使用数码管显示提供接口模块。

实验目的:今天这个实验为动态扫描式操作数码管,为以后使用数码管显示提供接口模块。能够完成按位显示任意数字与字母或者图案。

实验内容:此部分内容自己研究了半天,后来发现版主 51FPGA 已经在教程里面进行了说明。在对其代码进行了细致分析后,最终还是采用以版主的代码为基础,在其上进行修改与扩充的方式。代码内容如下:

/****************************************Copyright (c)****************************************************

** jobszheng@vip.sohu.com

**

**--------------File Info---------------------------------------------------------------------------------

** File Name: led_dynamic.v

** Last modified Date: 2013-03-30 10:07

** Last Version:

** Description: 使用动态扫描的方式来显示数码管,参考自51fpga

**

**--------------------------------------------------------------------------------------------------------

** Created By: Jobs Zheng

** Created date: 2013-03-30 10:07

** Version: v1.0

** Descriptions: The original version 初始版本

**

*********************************************************************************************************/

module led_dynamic(sys_clk, sys_rstn, sm_seg, sm_bit);

input sys_clk;

input sys_rstn;

output [7:0] sm_seg;

output [7:0] sm_bit;

reg [7:0] sm_seg;

reg [7:0] sm_bit;

reg [4:0] dataout_buf;

reg [2:0] disp_dat;

reg [15:0] delay_cnt;

always @ (posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt <= 16'd0;

else

begin

if(delay_cnt == 16'd49999)

delay_cnt <= 16'd0;

else

delay_cnt <= delay_cnt + 1'b1;

end

end

always @ (posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

disp_dat <= 4'd0;

else

begin

if(delay_cnt == 16'd49999)

disp_dat <= disp_dat + 1'b1;

else

disp_dat <= disp_dat;

end

end

always @ (disp_dat)

begin

case(disp_dat)

3'b000:

sm_bit = 8'b11111110;

3'b001:

sm_bit = 8'b11111101;

3'b010:

sm_bit = 8'b11111011;

3'b011:

sm_bit = 8'b11110111;

3'b100:

sm_bit = 8'b11101111;

3'b101:

sm_bit = 8'b11011111;

3'b110:

sm_bit = 8'b10111111;

3'b111:

sm_bit = 8'b01111111;

default :

sm_bit = 8'b11111110;

endcase;

end

always @(sm_bit)

begin

case(sm_bit)

8'b11111110:

dataout_buf = 17;

8'b11111101:

dataout_buf = 17;

8'b11111011:

dataout_buf = 16;

8'b11110111:

dataout_buf = 0;

8'b11101111:

dataout_buf = 11;

8'b11011111:

dataout_buf = 5;

8'b10111111:

dataout_buf = 17;

8'b01111111:

dataout_buf = 17;

default :

dataout_buf = 8;

endcase

end

always @(dataout_buf)

begin

case(dataout_buf)

5'h0: sm_seg = 8'hc0;

5'h1: sm_seg = 8'hf9;

5'h2: sm_seg = 8'ha4;

5'h3: sm_seg = 8'hb0;

5'h4: sm_seg = 8'h99;

5'h5: sm_seg = 8'h92;

5'h6: sm_seg = 8'h82;

5'h7: sm_seg = 8'hf8;

5'h8: sm_seg = 8'h80;

5'h9: sm_seg = 8'h90;

5'ha: sm_seg = 8'h88;

5'hb: sm_seg = 8'h83;

5'hc: sm_seg = 8'hc6;

5'hd: sm_seg = 8'ha1;

5'he: sm_seg = 8'h86;

5'hf: sm_seg = 8'h8e;

5'd16: sm_seg = 8'hf1; /* 字母 ‘j’ */

default:

sm_seg = 8'hff;

endcase

end

endmodule

实验结果:上电,使用jtag下载后,得到预期的效果。甚是欣喜。

实验感受:

不知道由于什么原因,开始的时候发现数码管的显示位是倒序,即最右边为位0。于是,通过更改pin的分布来进行更正。可以修改后,发现显示结果成了残缺的显示。查看代码未见异常,遂陷入痛苦的沉思中……

突然,一灵感过来“是不是我将位选与片选的引脚弄混了”,于是再次仔细查看代码与对应关系,发现果然是引脚位选与片选错了,我将位选的顺序反序相连了,因此才有了残码的显示。更改回位选,再将修改了片选位,终于得到了预期的效果“jobs” ——我的logo

秒表这个日常用品在生活还是相当重要的。我们跑步用来较精确计算时间;我们测试物体的移动速度;在高中物理实验中更是大放光彩……

实验目的:利用上回实验时编写的数码管显示模块,来完成进一步的应用。模块代码的移植。

实验内容:在上一个实验中,已经将数码管显示实验完成,并能独立显示某一位数码管内容,可以是数字,可以是字母,也可以是自定义字符。因此,本次实验通过其显示秒表的分钟,秒与百分之一秒。

除去了上一个实验的内容后,本次主要完成两个计数模块的设计,一个是百分之一秒模块的100进制计数模块,另一个是秒计数模块的60进制。两者之间通过进位寄存器来完成进位运算。

源代码附件所示[参见1]:

源代码及sof文件 http://share.eepw.com.cn/share/download/id/87848

实验结果:实验结果符合预期要求;

实验感受:本来以为刷新频率设置为10毫秒就够了,可是8位数码管全下来就是0.1秒的刷新频率了。显然要低于我们平时使用的85Hz的显示器,因此也就出现了闪烁现象。后来,设置成1000hz的刷新频率后,各项显示正常。目测很完美……嘿嘿