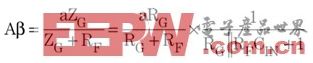

让我们再来认真看一下上一小节中提到的公式:

下面我们一项一项的来看看他们吧。

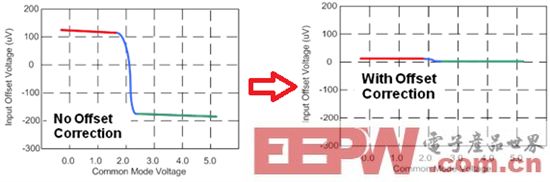

(1) Vos, 输入失调电压,大家都熟,不多废话。它更坏的一点是它不是一个老实待着的值,它会随着温度变化漂移呢。

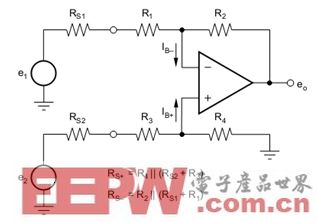

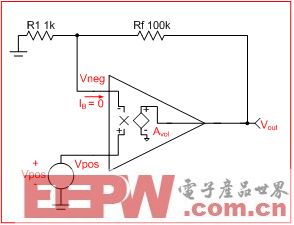

(2) Ib+, 同向端输入偏置电流,它流过同向端等效阻抗,形成一个误差电压。

(3) Ib-, 反向端输入偏置电流,它流过反向端等效阻抗,形成一个误差电压。

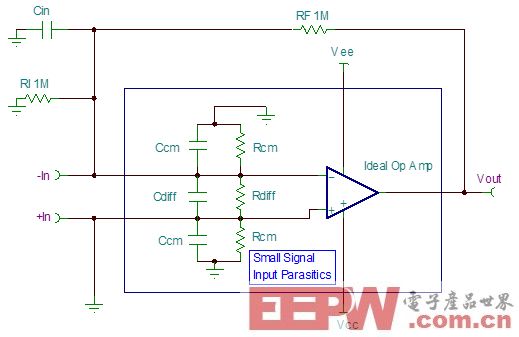

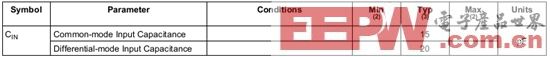

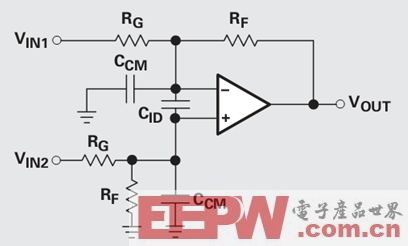

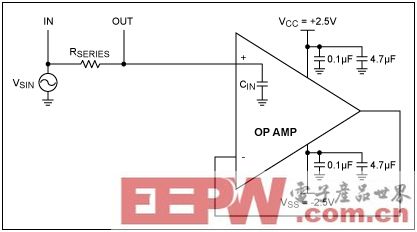

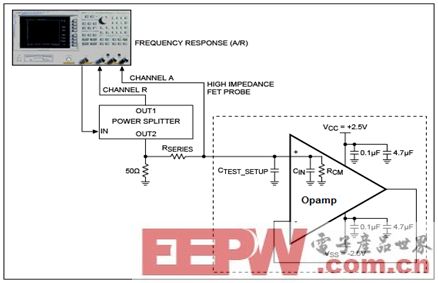

有人可能注意了,输入端阻抗怎么计算呢。下面的图一看就明白了。简而言之吧,输入电阻(信号源电阻加输入端电阻)与反馈电阻的并联。千万别忘了信号源电阻哦,因为我们时常选用高阻抗的传感器做信号源。

(4) en, 等效输入噪声。这个值,我的理解可不只是datasheet中给定的en如1.1nV√Hz。它是集成了电压噪声,电流噪声和电阻噪声三都的贡献的。是所有噪声等效到输入端的值。具体请参照Art Kay的文章和本系列博文的part4。

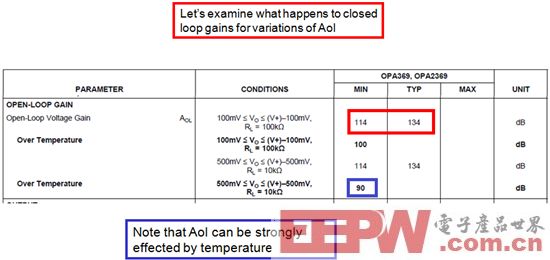

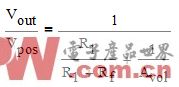

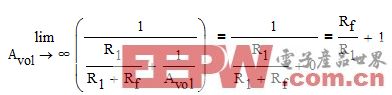

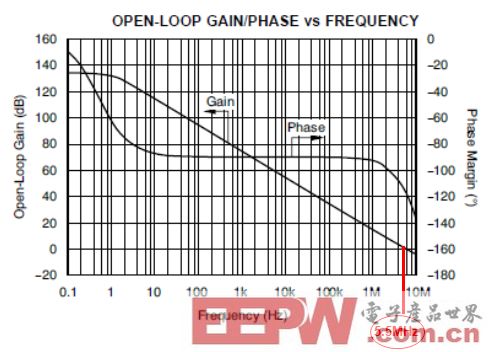

(5) eo/A, 这个表达式,可能很多人从来没有关注过,有这一项的原因是,运放的开环增益A不为0。这也就是因为输入贴值的不同,而引起的等效输入误差的不同了,举个例 子吧,如果输出值是5V。开环增益是100dB,不低了吧。它的折算到输入端的误差就有50uV啊。不是小数目了。

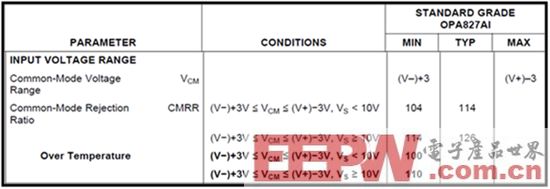

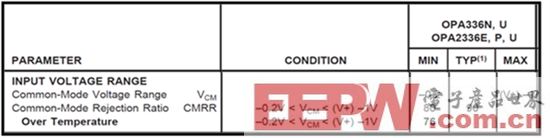

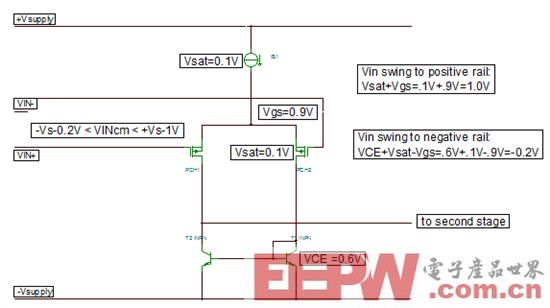

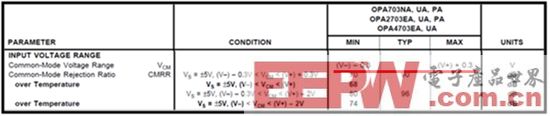

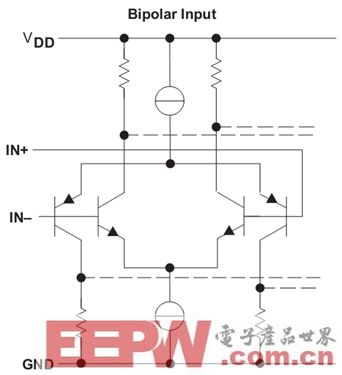

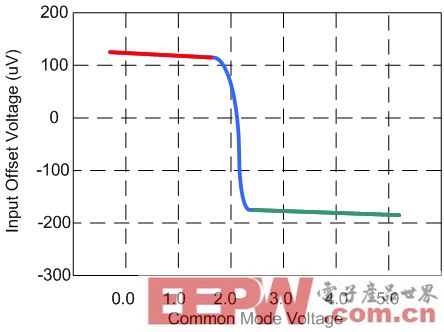

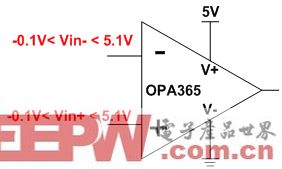

(6) eicm/CMRR, 这个不用多说,输入端的同模电压除以共模抑制比。又有一点不好的地方,运放的CMRR可是随共模信号频率的增加而下降的。好多运放的CMRR在共模信号到10KHz以上时,就比直流下降了几十个dB呢

(7) ΔVs/PSRR,电源电压的变引入的误差。同样的,交流PSRR在随频率的增高,而下降。

看了这些,可能还会以为,这点小误差是毛毛雨了,至多到mV级,甚至在uV级,不要忘了,它还要乘上一个增益Gain呢。假如输入误差是100uV。增益为100倍,则输出的误差信号,就是10mV。

Input_error x Gain = Output Error

如果还觉得没什么,那再讲一个经验值吧,一个满量程为5V的16位ADC的一个LSB约为75uV。只要75uV的误差就会引起ADC的一位的变化。假如放大电路的输出误差信号是1mV的话,这个信号给ADC,直接引起的误差就是13个LSB以上。

这个Output error,真是鱼龙混杂。有直流成份,这个可通过ADC采样后校正去除掉。有噪声信号,还有交流的成份。最不期望的,它还会随温度漂移呢。

我们在设计电路中,可以通过上面的分析,找出引起直流误差的主要因素,然后努力减小之。

我要赚赏金

我要赚赏金