我的LED灯——作业1

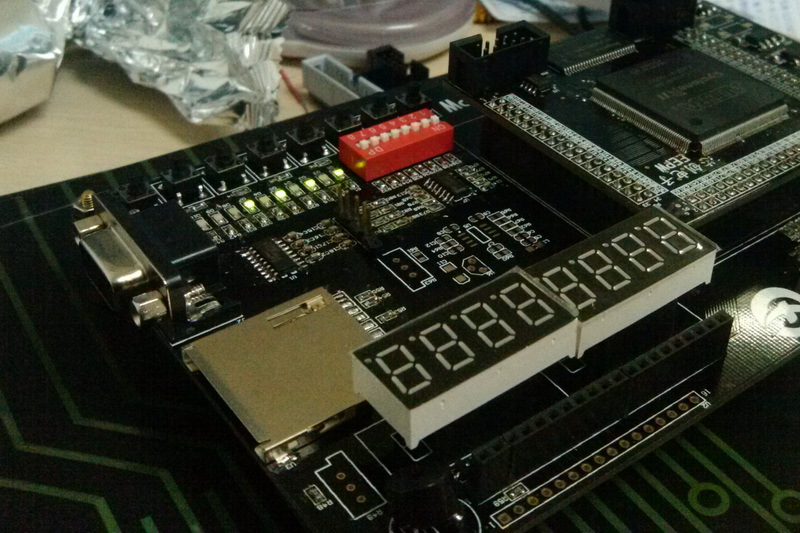

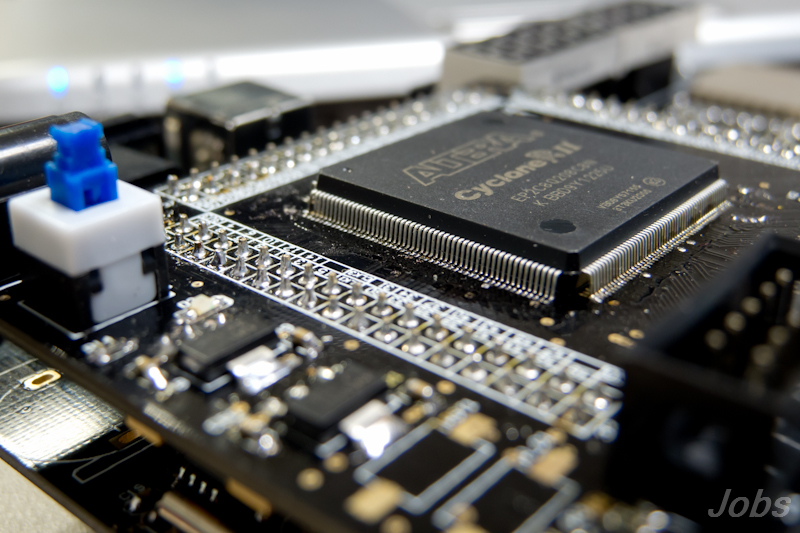

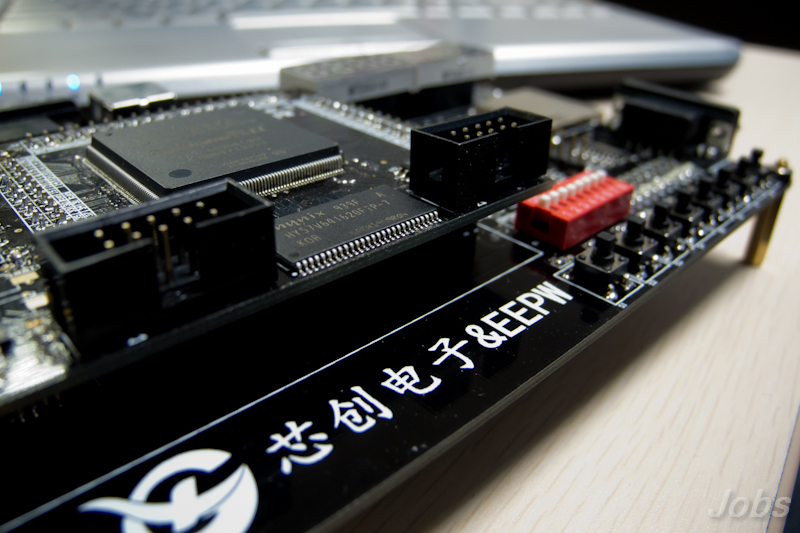

实验目的: 熟悉QuartusII软件及FPGA初学 熟悉verilog语言 实验内容: 将LED灯间隔点亮,此为常亮。 源代码如下:

module led_show(led);

output [7:0] led; assign led = 8'b10101010; endmodule 将LED灯以每隔0.5秒闪烁,源代码如下:module led_flicker(sys_clk, sys_rstn, led);

input sys_clk; input sys_rstn; output [7:0] led; /* LED输出信号 */ reg [7:0] led; reg [24: 0] delay_cnt; always @(posedge sys_clk or negedge sys_rstn) begin if(!sys_rstn) delay_cnt <= 25'd0; else begin if(delay_cnt == 25'd24999999) delay_cnt <= 25'd0; else delay_cnt <= delay_cnt + 1'b1; end endalways @ (posedge sys_clk or negedge sys_rstn)

begin if(!sys_rstn) led <= 8'b11111111; else begin if(delay_cnt == 25'd24999999) led <= ~led; else led <= led; end end endmodule 实验结果: 完成LED灯交替常量显示 根据教程所示,将LED灯以1Hz交替显示。(视频省略)

作业:

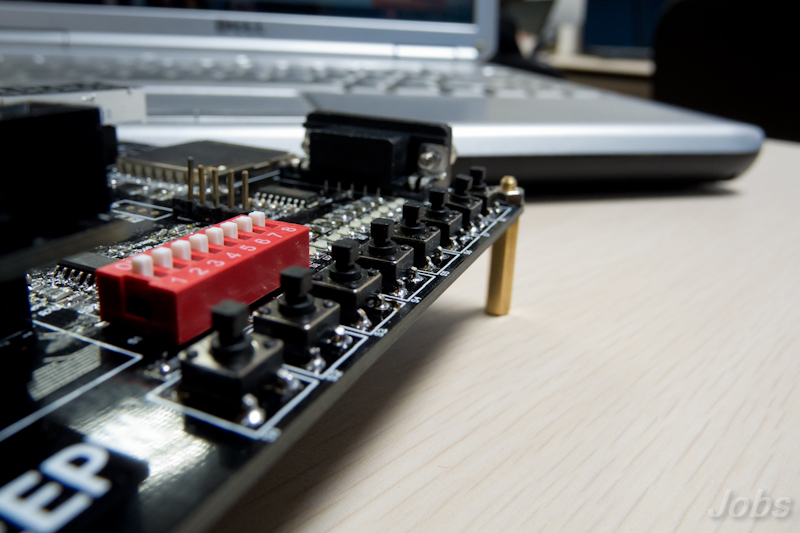

LED灯以0.5Hz的频率闪烁,此时只须要更改1Hz的时钟计数周期即可,源代码如下:

根据教程所示,将LED灯以1Hz交替显示。(视频省略)

作业:

LED灯以0.5Hz的频率闪烁,此时只须要更改1Hz的时钟计数周期即可,源代码如下:

module led_flicker(sys_clk, sys_rstn, led);

input sys_clk; input sys_rstn; output [7:0] led; /* LED输出信号 */ reg [7:0] led; reg [25: 0] delay_cnt; always @(posedge sys_clk or negedge sys_rstn) begin if(!sys_rstn) delay_cnt <= 26'd0; else begin if(delay_cnt == 26'd4999999) delay_cnt <= 26'd0; else delay_cnt <= delay_cnt + 1'b1; end endalways @ (posedge sys_clk or negedge sys_rstn)

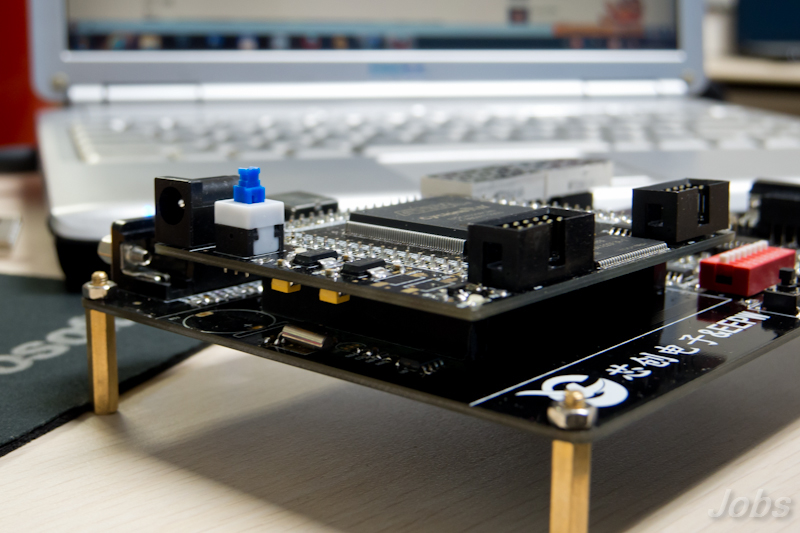

begin if(!sys_rstn) led <= 8'b11111111; else begin if(delay_cnt == 26'd4999999) led <= ~led; else led <= led; end end endmodule 完成编译,并成功在fpga开发板上显示。Cheer~~

我要赚赏金

我要赚赏金