13、PLL简单的配置实验

PLL(锁相环),给PLL一个时钟输入,经过PLL内部处理后,在输出端口就可以得到一定范围的时钟频率。

下面用图文对PLL的配置简单的说明下。

步骤:

1、先建一个PLL的工程,这个大家都会,不用做介绍;

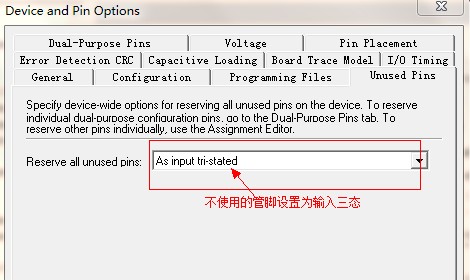

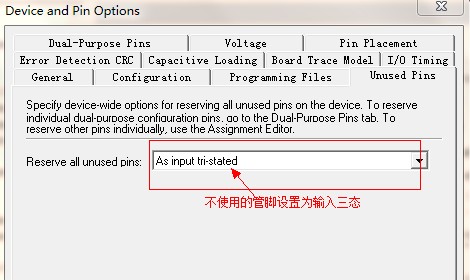

2、建完工程后,将不用的管脚设置为输入三态;

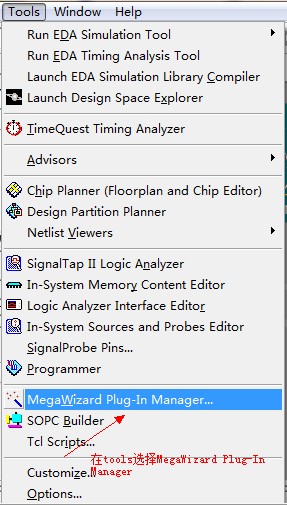

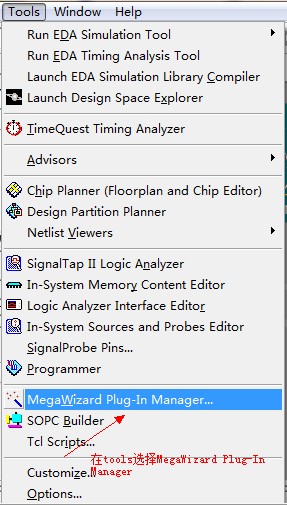

3、在Quartus的菜单栏选择tools--->MegaWizard Wizard Plug - In Manager

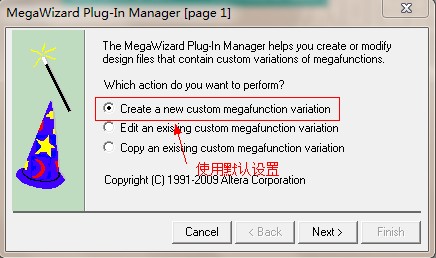

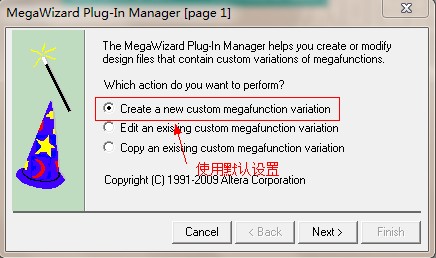

4、选择默认选项,如下图

5、如下图进行操作

(1)在I/O下,选择ALTPLL;

(2)选择Verilog HDL为配置PLL内核的使用语言;

(3)输入例化PLL的文件名;

6、选择器件的速度等级及外接晶振的大小

7、配置时钟c0的相关参数

8、配置时钟c1的参数

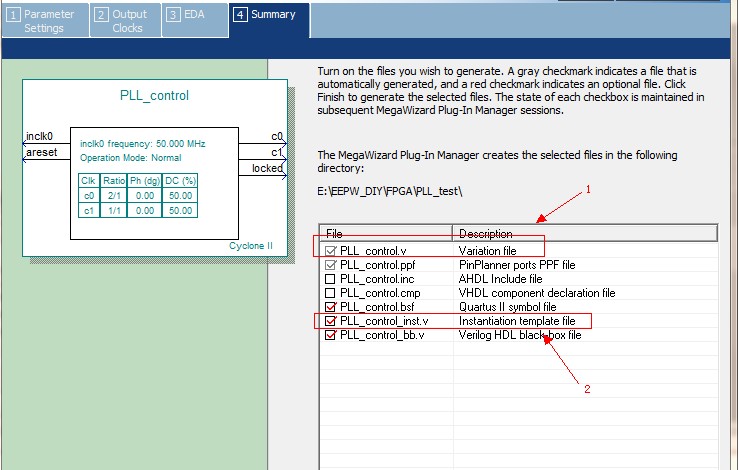

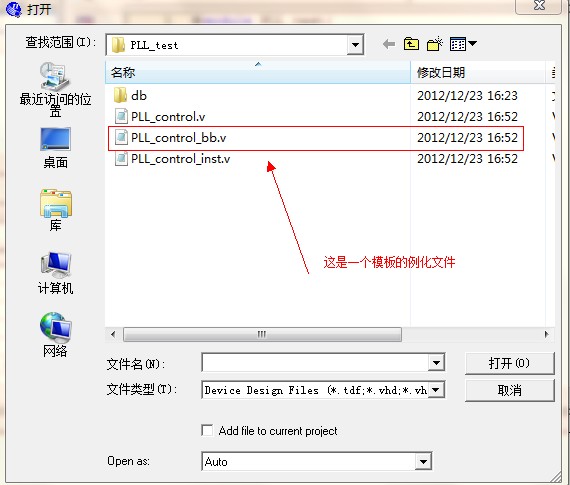

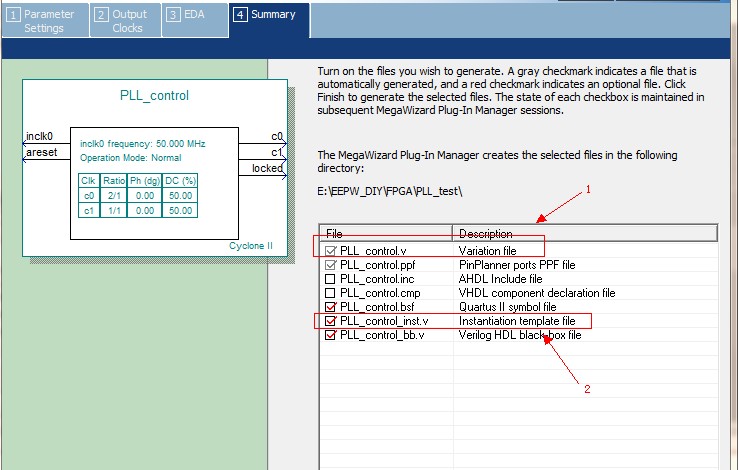

9、PLL核最终输出文件

(1)PLL_control.v PLL内部的控制IP核

(2)PLL_control_inst.v 是PLL的例化文件,可以直接复制来使用。

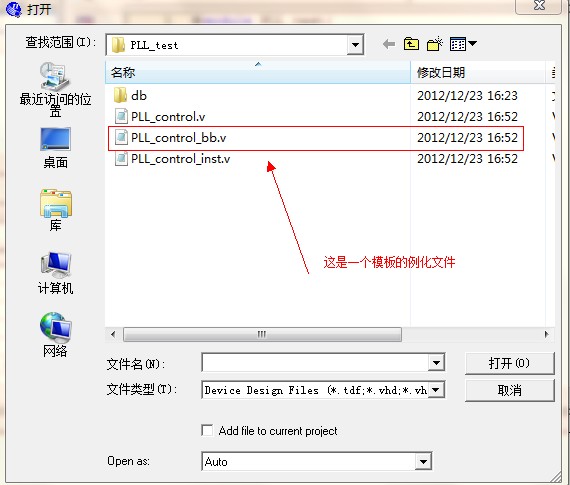

10、打开红框下面的 PLL_control_inst.v文件 复制里面PLL的例化模板

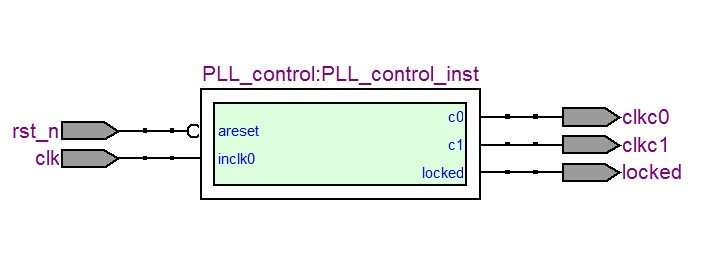

11、将PLL例化文件粘贴到PLL_test文件中,修改信号接口,与自己的定义的接口对应。

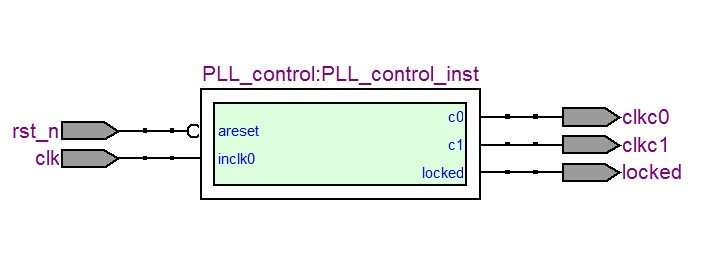

12、编译,打开RTL视图

PLL(锁相环),给PLL一个时钟输入,经过PLL内部处理后,在输出端口就可以得到一定范围的时钟频率。

下面用图文对PLL的配置简单的说明下。

步骤:

1、先建一个PLL的工程,这个大家都会,不用做介绍;

2、建完工程后,将不用的管脚设置为输入三态;

3、在Quartus的菜单栏选择tools--->MegaWizard Wizard Plug - In Manager

4、选择默认选项,如下图

5、如下图进行操作

(1)在I/O下,选择ALTPLL;

(2)选择Verilog HDL为配置PLL内核的使用语言;

(3)输入例化PLL的文件名;

6、选择器件的速度等级及外接晶振的大小

7、配置时钟c0的相关参数

8、配置时钟c1的参数

9、PLL核最终输出文件

(1)PLL_control.v PLL内部的控制IP核

(2)PLL_control_inst.v 是PLL的例化文件,可以直接复制来使用。

10、打开红框下面的 PLL_control_inst.v文件 复制里面PLL的例化模板

11、将PLL例化文件粘贴到PLL_test文件中,修改信号接口,与自己的定义的接口对应。

12、编译,打开RTL视图

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |