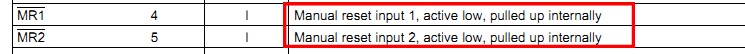

外部上拉是可以提高驱动能力,那内部上拉呢?看dsp、电源很多引脚都有该功能;

此外,DSP中还提及,因为有内部上拉,故GPIO口可选择进行输入、输出、高阻态三种情况的能力。是因为OD或OC门加内部上拉形成的?

共9条

1/1 1 跳转至页

7楼

有内部上拉是可以简化设计,一般来说有内上拉的除非特别说明,都可以悬空处理。主要上下拉就是为了防止输入口因为电平不确定而带来的错误配置。所以一旦有了内部若上下拉。就避免了这个问题

共9条

1/1 1 跳转至页

回复

| 有奖活动 | |

|---|---|

| 请大声喊出:我要开发板! | |

| 【有奖活动】EEPW网站征稿正在进行时,欢迎踊跃投稿啦 | |

| 【有奖活动】智能可穿戴设备AR/VR如何引领科技新潮流! | |

| 奖!发布技术笔记,技术评测贴换取您心仪的礼品 | |

| 【有奖活动】震撼来袭!这场直播将直击工程师的心灵! | |

| 打赏帖 | |

|---|---|

| 如何实现基于NXPiMX.RT1021的BH1730采集被打赏50分 | |

| 【换取手持数字示波器】AHT10温度检测分享被打赏40分 | |

| 【换取手持数字示波器】ACM32F070开发板点亮LCD屏和触控按键,串口,ADC被打赏40分 | |

| 【换取手持数字示波器】ACM32F070LCD屏和触控按键功驱动蜂鸣器分享被打赏40分 | |

| 【换取手持数字示波器】国民技术PWM功能知识分享被打赏40分 | |

| 【换取手持数字示波器】放大器运放知识分享被打赏40分 | |

| 【分享评测,赢取加热台】+开关电源AC输入知识分享被打赏30分 | |

| 【换取手持数字示波器】N32G430点亮数码管与串口打印、ADC被打赏40分 | |

| 老胖子聊电路--分析一个反馈电路被打赏50分 | |

| 【换取手持数字示波器】+点亮WS2812RGB灯被打赏50分 | |