2012年10月20日

收到开发板(商品四),之前也一直在做一些准备,看了下子关于VHDL的书籍,并且安装了QuartusII。。。

2012年10月22日

下载了论坛中的几个测试程序,并且学会了如何将程序烧到开发板中,实现了相应的功能。并且对这个好玩的东西产生了很大的兴趣。。。

2012年10月24日

从一些资料中,学习到了软件的大致使用:即从编写程序,到编译,时序仿真,功能仿真,引脚锁定等;

深入的去理解了下,VHDL的元件例化,以及设计中的层次的思想,在自己最后的项目(出租车计价器)会应用到的。

2012年10月25日

昨日,有个遗留的问题,即引脚锁定,自己寻摸着应该是与开发的电路想对应的(高手也是如是指点的),于是对应着原理图,仔细的了解了下子。。。

同时,也开始着手编写的第一个程序,LED流水灯。。。

2012年10月29日

完成了LED流水灯 闪烁灯的实现。。。(代码见3,4,5层)

2012年10月31日

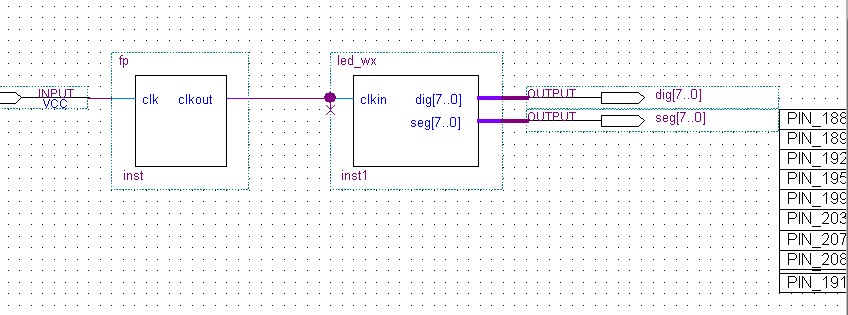

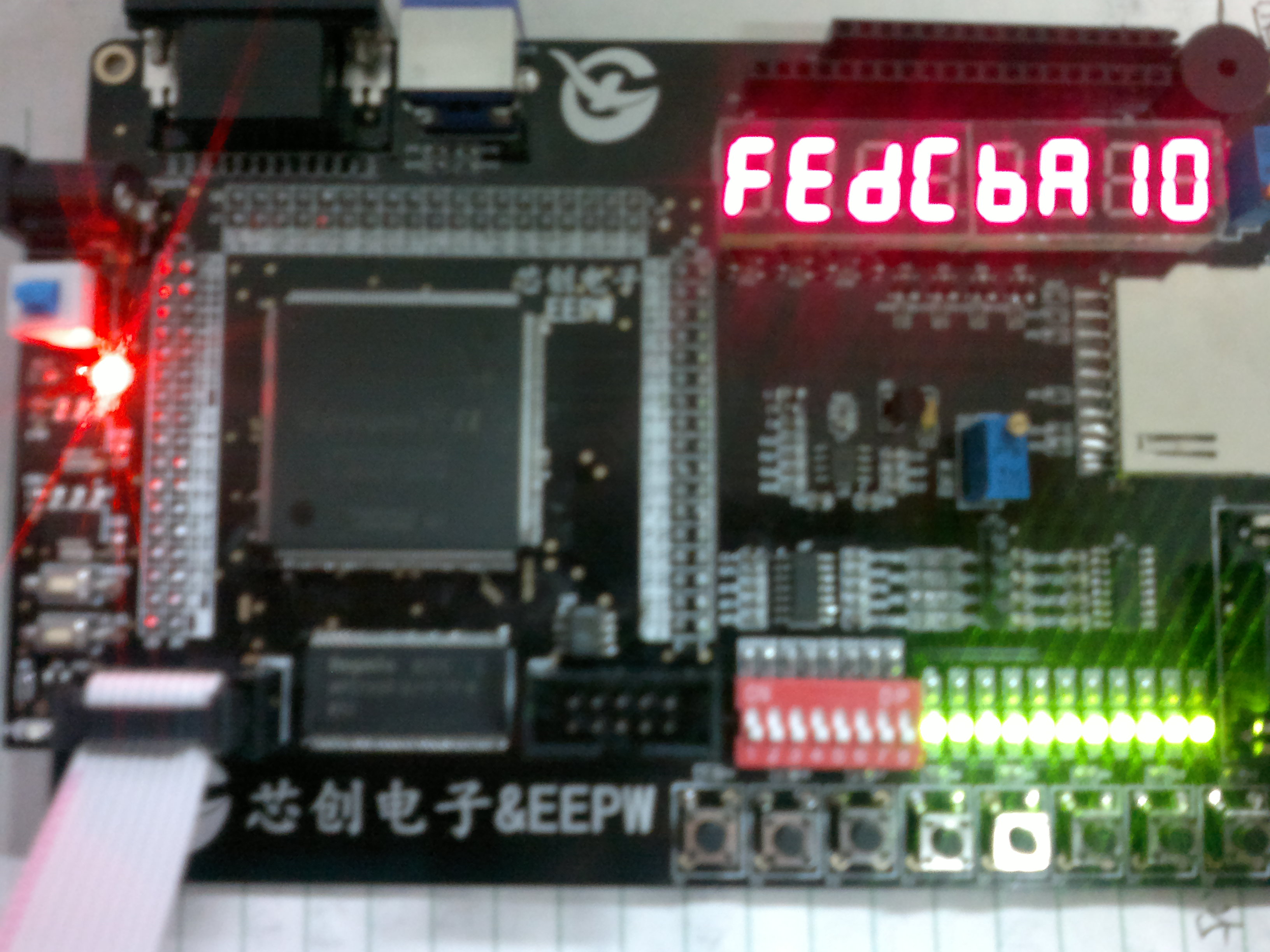

完成了LED数码管的动态显示。。。(代码见8层,系统图见9层,效果图见10层)

2012年11月1日

完成了拨码开关控制LED数码管的静态显示(效果见11楼,代码12楼)

2012年11月3日

完成了硬件电子琴的简单功能(分别按住按键s1-s7会发出低音部分的1-7;按住s8的同时分别按住s1-s7则会发出中音1-7的声音)

2012年11月7日

完成硬件乐曲自动演奏 (代码及分析见14,15楼)

2012年12月13日

完成lcd的显示 视频过段时间上传

我要赚赏金

我要赚赏金