| 日期 | 进程 | 楼层 | 备注 |

| 10.31 | 板子搞到手焊接ing~~~ | 2 | 上大图 |

| 11.02 | 上一个动态扫描程序 | 4 | 程序+图 |

| 11.03 | 来个vhdl版本的lcd1602 | 7 | 程序+图 |

| 日期 | 进程 | 楼层 | 备注 |

| 10.31 | 板子搞到手焊接ing~~~ | 2 | 上大图 |

| 11.02 | 上一个动态扫描程序 | 4 | 程序+图 |

| 11.03 | 来个vhdl版本的lcd1602 | 7 | 程序+图 |

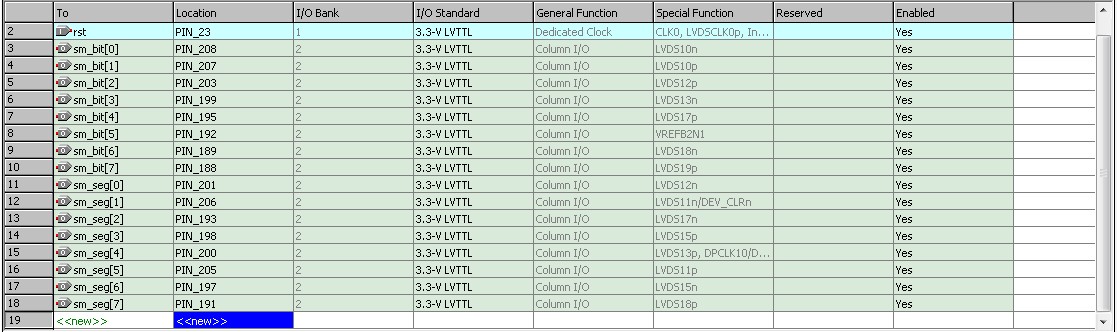

数码管动态显示

module scan_led(clk,rst,sm_seg,sm_bit);

input clk,rst;

output[7:0] sm_seg;

output[7:0] sm_bit;

reg[7:0] sm_seg;

reg[7:0] sm_bit;

reg[15:0] cnt_scan;

reg[4:0] dataout_buf;

always@(posedge clk or negedge rst)

begin

if(!rst) begin

cnt_scan<=0;

end

else begin

cnt_scan<=cnt_scan+1'b1;

end

end

always @(cnt_scan)

begin

case(cnt_scan[15:13])

3'b000 :

sm_bit = 8'b1111_1110;

3'b001 :

sm_bit = 8'b1111_1101;

3'b010 :

sm_bit = 8'b1111_1011;

3'b011 :

sm_bit = 8'b1111_0111;

3'b100 :

sm_bit = 8'b1110_1111;

3'b101 :

sm_bit = 8'b1101_1111;

3'b110 :

sm_bit = 8'b1011_1111;

3'b111 :

sm_bit = 8'b0111_1111;

default :

sm_bit = 8'b1111_1110;

endcase

end

always@(sm_bit)

begin

case(sm_bit)

8'b1111_1110:

dataout_buf=0;

8'b1111_1101:

dataout_buf=1;

8'b1111_1011:

dataout_buf=2;

8'b1111_0111:

dataout_buf=3;

8'b1110_1111:

dataout_buf=4;

8'b1101_1111:

dataout_buf=5;

8'b1011_1111:

dataout_buf=6;

8'b0111_1111:

dataout_buf=7;

default:

dataout_buf=8;

endcase

end

always@(dataout_buf)

begin

case(dataout_buf)

4'h0 : sm_seg = 8'b00000011; // "0"

4'h1 : sm_seg = 8'b10011111; // "1"

4'h2 : sm_seg = 8'b00100101; // "2"

4'h3 : sm_seg = 8'b00001101; // "3"

4'h4 : sm_seg = 8'b10011001; // "4"

4'h5 : sm_seg = 8'b01001001; // "5"

4'h6 : sm_seg = 8'b01000001; // "6"

4'h7 : sm_seg = 8'b00011111; // "7"

/* 4'h8 : sm_seg = 8'h80; // "8"

4'h9 : sm_seg = 8'h90; // "9"

4'ha : sm_seg = 8'h88; // "a"

4'hb : sm_seg = 8'h83; // "b"

4'hc : sm_seg = 8'hc6; // "c"

4'hd : sm_seg = 8'ha1; // "d"

4'he : sm_seg = 8'h86; // "e"

4'hf : sm_seg = 8'h8e; // "f"*/

endcase

end

endmodule

上图

来个vhdl lcd1602的 注释乱码咯 见谅啊~~

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity lcd is

port(clk:in std_logic;

lcd_rs,lcd_rw,lcd_e:out std_logic;

dataout:out std_logic_vector(7 downto 0));

end lcd;

architecture behave of lcd is

signal p:std_logic_vector(15 downto 0);

signal m:std_logic_vector(7 downto 0);

signal t,n:std_logic:='0';

begin

process(clk,n)

begin

if(n='0')then

if(clk'event and clk='1')then ---¸ßµçƽ´¥·¢·½Ê½

p<=p+1;

if(p>"0111111111111111")then -- 5000000000m/3760

t<='1';

else

t<='0';

end if;

end if;

end if;

end process;

lcd_e<=t; --//ÿ¸öÂö³å¿ª¹ØʹÄÜ

process(t,m)

begin

if(t'event and t='1')then

m<=m+1;

if(m>39)then

n<='1';

end if;

if(m<6 or m=23)then --//µ±m<5ʱΪ³õʼ»¯m=6£¬m=23ʱΪÉ趨ÐÐ Æ䶼ΪдָÁî

lcd_rs<='0';

lcd_rw<='0';

else --//ÆäÓà¾ùΪдÊý¾Ý

lcd_rs<='1';

lcd_rw<='0';

end if;

end if;

case m is

when"00000001"=>dataout<=X"38"; --//lcd1602 ³õʼ»¯º¯ÊýÖ¸Áî 0x38 0x0c 0x06 0x80 0x01

when"00000010"=>dataout<=X"0C";

when"00000011"=>dataout<=X"06";

when"00000100"=>dataout<=X"80";

when"00000101"=>dataout<=X"01";

when"00000110"=>dataout<=X"40"; ------www.eepw.com --

when"00000111"=>dataout<=X"77";

when"00001000"=>dataout<=X"77";

when"00001001"=>dataout<=X"77";

when"00001010"=>dataout<=X"2E";

when"00001011"=>dataout<=X"65";

when"00001100"=>dataout<=X"65";

when"00001101"=>dataout<=X"70";

when"00001110"=>dataout<=X"77";

when"00001111"=>dataout<=X"2E";

when"00010000"=>dataout<=X"63";

when"00010001"=>dataout<=X"6F";

when"00010010"=>dataout<=X"6D";

when"00010100"=>dataout<=X"20";

when"00010101"=>dataout<=X"20";

when"00010110"=>dataout<=X"20";

when"00010111"=>dataout<=X"20";

when"00011000"=>dataout<=X"C0"; --//»»ÐÐ aihai0002275

when"00011001"=>dataout<=X"20";

when"00011010"=>dataout<=X"20";

when"00011011"=>dataout<=X"20";

when"00011100"=>dataout<=X"20";

when"00011101"=>dataout<=X"61";

when"00011110"=>dataout<=X"69";

when"00011111"=>dataout<=X"68";

when"00100000"=>dataout<=X"61";

when"00100001"=>dataout<=X"69";

when"00100010"=>dataout<=X"30";

when"00100011"=>dataout<=X"30";

when"00100100"=>dataout<=X"30";

when"00100101"=>dataout<=X"32";

when"00100110"=>dataout<=X"32";

when"00100111"=>dataout<=X"37";

when"00101000"=>dataout<=X"35";

when others=>dataout<=X"20"; --//¿Õ¸ñ

end case;

end process;

end behave;

上大图

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 在FireBeetle2ESP32-C5上实现温湿度检测和显示被打赏¥20元 | |

| 在FireBeetle2ESP32-C5上实现光照强度检测及显示被打赏¥21元 | |

| 以FireBeetle2ESP32-C5实现数据识读播报被打赏¥19元 | |

| 【STM32F103ZET6】14:实测STM32F1的串口输出任务的挂起与恢复功能被打赏¥27元 | |

| Chaos-nano在压力容器监控系统中的项目应用被打赏¥23元 | |

| 基于FireBeetle2ESP32-C5的WS2812B彩色灯带控制被打赏¥21元 | |

| SWM221CBT7显示开发板驱动TFT显示屏被打赏¥19元 | |

| SWM221CBT7显示开发板驱动OLED屏显示被打赏¥19元 | |

| SWM221CBT7显示开发板及其使用被打赏¥20元 | |

| 揭秘Chaos-nano:ArduinoProMini轻量级操作系统开发框架深度解析与实战应用被打赏¥19元 | |