电路描述

图1所示电路接受单端输入并使用宽带宽(3 GHz) M/A-COM ECT1-1-13M 1:1变压器将其转换为差分信号。ADL5565 6.0 GHz差分放大器采用6 dB增益工作时具有200 Ω的差分输入阻抗,采用12 dB增益工作时为100 Ω,采用15.5 dB增益工作时为67 Ω。

ADL5565是 AD6657A的理想驱动器,通过低通滤波器可在ADC中实现全差分架构,提供良好的高频共模抑制,同时将二阶失真产物降至最低。 ADL5565根据输入连接提供6 dB、12 dB和15.5 dB的增益。此电路中,使用6 dB增益补偿滤波器网络和变压器(约2.1 dB)的插入损耗,从而提供4.0 dB的总信号增益。增益还有助于将放大器的噪声影响降至最低。

AD6657A是一款四通道中频接收机,其中将每个ADC输出从内部连接到数字噪声整形再量化器(NSR)模块。集成NSR电路能够提高奈奎斯特带宽内较小频段的信噪比(SNR)性能。

可以对NSR模块进行编程,以提供采样速率22%、33%或36%的带宽。对于本电路笔记内采用的数据,采样速率为184.32 MSPS,且以下NSR设置适用:

NSR带宽 = 36%

调谐字(TW) = 12

左频带边缘 = 11.06 MHz(输入 = 173.26 MHz)

中心频率 = 44.24 MHz(输入 = 140.08 MHz)

右频带边缘 = 77.41 MHz(输入 = 106.91 MHz)

NSR模块的详细工作原理请参见 AD6657A数据手册。

抗混叠滤波器是采用标准滤波器设计程序(本例中是Agilent ADS)设计的四阶巴特沃兹低通滤波器。选择巴特沃兹滤波器是因为它具有平坦响应。四阶滤波器产生1.03的交流噪声带宽比。其他滤波器设计程序可从Nuhertz Technologies ( http://www.nuhertz.com/filter)或Quite Universal Circuit Simulator (Qucs) Simulation (http://www.qucs.sourceforge.net)获得。

为了实现最佳性能,ADL5565应载入至少200 Ω的净差分负载。20 Ω串联电阻将滤波器电容与放大器输出隔离开,当加入下游阻抗时可产生249 Ω的净负载阻抗。

15 Ω电阻与ADC输入串联,将内部开关瞬变与滤波器和放大器隔离开。110 Ω电阻与ADC并联,用于降低ADC的输入阻抗,使性能更具可预测性。

AD6657A的差分输入阻抗与2.2 pF并联,约为2.4 kΩ。对于该类型的开关电容输入ADC,实部与虚部与输入频率成函数关系;详细分析请参见应用笔记AN-742。

四阶巴特沃兹滤波器采用50 Ω的源阻抗、209 Ω的负载阻抗和190 MHz的3 dB带宽设计而成。滤波器的最终电路值如图1所示。从滤波器程序生成的值如图2所示。为滤波器无源元件选择的值是最接近程序生成值的标准值。ADC的内部2.2 pF电容用作滤波器设计的最终分流电容。

从本设计可以看出,最佳性能的获得有时可以是迭代过程。滤波器程序设计值非常接近最终值,但由于存在一些板寄生电容,滤波器最终值略有不同。图3显示了滤波器的最终设计值。

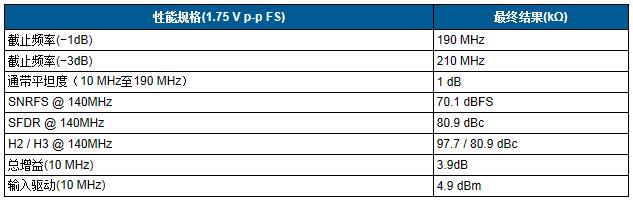

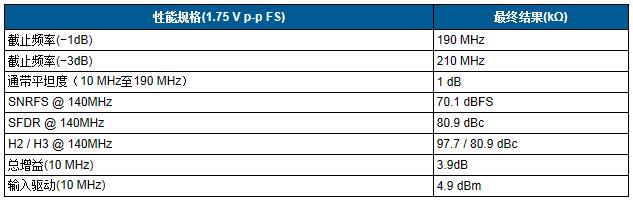

表1总结了系统的测量性能,其中3 dB带宽为210 MHz。网络的总插入损耗约为2 dB。图4所示为最终滤波器电路的带宽响应,图5所示为SNR和SFDR性能。

表1. 电路的测定性能

我要赚赏金

我要赚赏金