运算放大器的静态技术指标

1.输入失调电压VIO(input offset voltage) :输入电压为零时,将输出电压除以电压增益,即为折算到输入端的失调电压。VIO是表征运放内部电路对称性的指标。

2.输入失调电流IIO(input offset current):在零输入时,差分输入级的差分对管基极电流之差,用于表征差分级输入电流不对称的程度。

3.输入偏置电流IB(input bias current):运放两个输入端偏置电流的平均值,用于衡量差分放大对管输入电流的大小。

4.输入失调电压温漂:在规定工作温度范围内,输入失调电压随温度的变化量与温度变化量之比值。

5.输入失调电流温漂:在规定工作温度范围内,输入失调电流随温度的变化量与温度变化量之比值。

6.最大差模输入电压 (maximum differential mode input voltage):运放两输入端能承受的最大差模输入电压,超过此电压时,差分管将出现反向击穿现象。

7.最大共模输入电压(maximum common mode input voltage):在保证运放正常工作条件下,共模输入电压的允许范围。共模电压超过此值时,输入差分对管出现饱和,放大器失去共模抑制能力。

运算放大器的动态技术指标

1.开环差模电压放大倍数(open loop voltage gain) :运放在无外加反馈条件下,输出电压与输入电压的变化量之比。

2.差模输入电阻(input resistance) :输入差模信号时,运放的输入电阻。

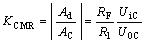

3.共模抑制比(common mode rejection ratio) :与差分放大电路中的定义相同,是差模电压增益 与共模电压增益 之比,常用分贝数来表示。 KCMR=20lg(Avd / Avc ) (dB)

4.-3dB带宽(—3dB band width) :运算放大器的差模电压放大倍数 在高频段下降3dB所定义的带宽 。

5.单位增益带宽(BW?G)(unit gain band width): 下降到1时所对应的频率,定义为单位增益带宽 。

6.转换速率(压摆率)(slew rate):反映运放对于快速变化的输入信号的响应能力。

7.等效输入噪声电压Vn(equivalent input noise voltage):输入端短路时,输出端的噪声电压折算到输入端的数值。这一数值往往与一定的频带相对应。

集成运算放大器指标测试

集成运算放大器是一种线性集成电路,和其它半导体器件一样,它是用一些性能指标来衡量其质量的优劣。为了正确使用集成运放,就必须了解它的主要参数指标。集成运放组件的各项指标通常是由专用仪器进行测试的,这里介绍的是一种简易测试方法。

本实验采用的集成运放型号为μA741(或F007),引脚排列如图7-1所示,它是八脚双列直插式组件,②脚和③脚为反相和同相输入端,⑥脚为输出端,⑦脚和④脚为正、负电源端,①脚和⑤脚为失调调零端,①⑤脚之间可接入一只几十KΩ的电位器并将滑动触头接到负电源端。 ⑧脚为空脚。

1、 μA741主要指标测试

图7-1 μA741管脚图 图7-2 U0S、I0S测试电路

1)输入失调电压U0S

理想运放组件,当输入信号为零时,其输出也为零。但是即使是最优质的集成组件,由于运放内部差动输入级参数的不完全对称,输出电压往往不为零。这种零输入时输出不为零的现象称为集成运放的失调。

输入失调电压U0S 是指输入信号为零时,输出端出现的电压折算到同相输入端的数值。

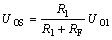

失调电压测试电路如图7-2所示。闭合开关K1及K2,使电阻RB短接,测量此时的输出电压U01 即为输出失调电压,则输入失调电压

实际测出的U01可能为正,也可能为负,一般在1~5mV,对于高质量的运放U0S在1mV以下。

测试中应注意:a、将运放调零端开路。

b、要求电阻R1和R2,R3和RF的参数严格对称。

2)输入失调电流I0S

输入失调电流I0S 是指当输入信号为零时,运放的两个输入端的基极偏置电流之差,

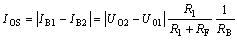

输入失调电流的大小反映了运放内部差动输入级两个晶体管β的失配度,由于IB1 ,IB2 本身的数值已很小(微安级),因此它们的差值通常不是直接测量的,测试电路如图7-2所示,测试分两步进行

a、 闭合开关K1及K2,在低输入电阻下,测出输出电压U01 , 如前所述,这是由输入失调电压U0S 所引起的输出电压。

b、断开K1及K2,两个输入电阻RB接入,由于RB 阻值较大,流经它们的输入电流的差异,将变成输入电压的差异,因此,也会影响输出电压的大小,可见测出两个电阻RB接入时的输出电压U02 ,若从中扣除输入失调电压U0S 的影响,则输入失调电流I0S 为

一般,I0S 约为几十~几百nA(10-9A),高质量运放IOS低于1nA。

测试中应注意: a、将运放调零端开路。

b、两输入端电阻RB必须精确配对。

3)开环差模放大倍数Aud

集成运放在没有外部反馈时的直流差模放大倍数称为开环差模电压放大倍数,用Aud 表示。它定义为开环输出电压U0与两个差分输入端之间所加信号电压Uid 之比。

按定义Aud 应是信号频率为零时的直流放大倍数,但为了测试方便,通常采用低频(几十赫芝以下)正弦交流信号进行测量。由于集成运放的开环电压放大倍数很高,难以直接进行测量,故一般采用闭环测量方法。 Aud的测试方法很多,现采用交、直流同时闭环的测试方法,如图7-3所示。

图7-3 Aud测试电路

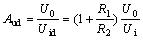

被测运放一方面通过RF、R1、R2完成直流闭环,以抑制输出电压漂移,另一方面通过RF和RS实现交流闭环,外加信号uS经R1、R2分压,使uid 足够小,以保证运放工作在线性区,同相输入端电阻R3应与反相输入端电阻R2相匹配,以减小输入偏置电流的影响,电容C 为隔直电容。被测运放的开环电压放大倍数为

通常低增益运放Aud约为60~70db,中增益运放约为80db,高增益在100db以上,可达120~140db。

测试中应注意:a、测试前电路应首先消振及调零。

b、被测运放要工作在线性区。

c、输入信号频率应较低,一般用50~100HZ ,输出信号幅度应较小,且无明显失真。

4)共模抑制比CMRR

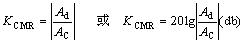

集成运放的差模电压放大倍数Ad与共模电压放大倍数AC之比称为共模抑制比

共模抑制比在应用中是一个很重要的参数,理想运放对输入的共模信号其输出为零,但在实际的集成运放中,其输出不可能没有共模信号的成分,输出端共模信号愈小,说明电路对称性愈好,也就是说运放对共模干扰信号的抑制能力愈强,即CMRR愈大。CMRR的测试电路如图7-4所示。

集成运放工作在闭环状态下的差模电压放大倍数为

当接入共模输入信号Uic时,测得U0C,则共模电压放大倍数为

得共模抑制比

图7-4 CMRR测试电路

测试中应注意:a、消振与调零

b、R1与R2、R3与RF之间阻值严格对称

c、输入信号Uic 幅度必须小于集成运放的最大共模输入电压范围 Uicm

5) 共模输入电压范围Uicm

集成运放所能承受的最大共模电压称为共模输入电压范围,超出这个范围,运放的CMRR会大大下降,输出波形产生失真,有些运放还会出现“自锁”现象以及永久性的损坏。

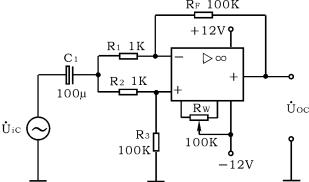

Uicm的测试电路如图7-5所示。

被测运放接成电压跟随器形式,输出端接示波器,观察最大不失真输出波形,从而确定Uicm值。

6) 输出电压最大动态范围UOPP

集成运放的动态范围与电源电压、外接负载及信号源频率有关。测试电路如图7-6所示。

改变uS幅度,观察u0削顶失真开始时刻,从而确定u0的不失真范围,这就是运放在某一定电源电压下可能输出的电压峰峰值UOPP。

图7-5 Uicm测试电路 图7-6 UOPP测试电路

2、集成运放在使用时应考虑的一些问题

1) 输入信号选用交、直流量均可, 但在选取信号的频率和幅度时,应考虑运放的频响特性和输出幅度的限制。

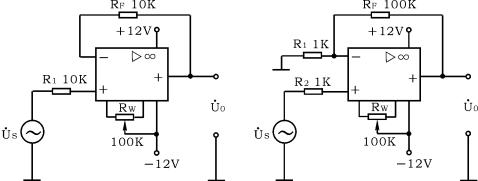

2) 调零。为提高运算精度,在运算前, 应首先对直流输出电位进行调零,即保证输入为零时,输出也为零。当运放有外接调零端子时,可按组件要求接入调零电位器RW,调零时,将输入端接地,调零端接入电位器RW,用直流电压表测量输出电压U0,细心调节RW,使U0为零(即失调电压为零)。如运放没有调零端子,若要调零,可按图7-7所示电路进行调零。

一个运放如不能调零,大致有如下原因:① 组件正常,接线有错误。② 组件正常,但负反馈不够强(RF/R1 太大),为此可将RF短路,观察是否能调零。③ 组件正常,但由于它所允许的共模输入电压太低,可能出现自锁现象,因而不能调零。为此可将电源断开后,再重新接通,如能恢复正常,则属于这种情况。④组件正常,但电路有自激现象,应进行消振。⑤组件内部损坏,应更换好的集成块。

(a) (b)

图7-7 调零电路

3) 消振。一个集成运放自激时,表现为即使输入信号为零, 亦会有输出,使各种运算功能无法实现,严重时还会损坏器件。在实验中,可用示波器监视输出波形。为消除运放的自激,常采用如下措施

①若运放有相位补偿端子,可利用外接RC补偿电路,产品手册中有补偿电路及元件参数提供。②电路布线、元、器件布局应尽量减少分布电容。③在正、负电源进线与地之间接上几十μF的电解电容和0.01~0.1μF 的陶瓷电容相并联以减小电源引线的影响。

什么是 PSRR

PSRR,就是 Power Supply Rejection Ratio 的缩写,中文含意为“电源抑制比”。也就是说, PSRR 表示把输入与电源视为两个独立的信号源时,所得到的两个电压增益的比值。基本计算公式为:

PSRR 的单位为分贝(dB),采用对数比值,此处V1是输入电压的改变,而V2是输出电压的改变。

从上面的式子可以看出,影响输出信号的因素除了电路本身之外,还受到了供电电源的影响。PSRR 是一个用来描述输出信号受电源影响的量,PSRR 越大,输出信号受到电源的影响越小。 这个等式的计算结果一般是零。如果看到有电源供应商标明PSRR是正值,不要惊讶,这只是因为他们使用的是V2与V1而不是V1与V2的比值。只要取PSRR的绝对值,就能避免一切迷惑了。设计者们都希望PSRR的绝对值越高越好,因为PSRR绝对值越高就意味着输出上的噪音/波纹越低。比如,80 dB 的PSRR绝对值(输出纹波比输入波纹小1万倍)就比20dB的绝对值(输出波纹比输入波纹小10倍)要好。

还可得出,输出电压 Vout 是 Vin 与电源电压 VCC 的函数。如果输入信号 Vin 变化了 SVin,输出信号的变化量 SVout 是由输入到输出的电压增益 Av 乘以输入电压的变化量 SVin。如果把电源电压变化 SVCC 看作一个很小信号,由于电源电压变化导致的输出电压的变化量 SVout 则为电源电压到输出的电压增益 Avo 乘以电源电压变化量 SVCC。

不稳定的供电电压势必会影响输出信号的波形,影响的幅度取决于 PSRR。所以需要侧重于运放等的去耦设计和电源的设计(通常较多用 LDO 线性电源给运放供电)。PSRR 是在单位闭环增益情况下得到的,因此在负反馈应用中引起的输出变化需乘以闭环增益。

一般地,PSRR 有 3个具体参数:+PSRR,-PSRR,+/-PSRR。表示从某个电源端或两个电源端分别或同时异向低频变化,在运放差分输入端引入的传输或影响量值。如上所分析的:SVps=1V 的电源变化,在 PRSS=80dB 运放输入端,导致 SVdi=100uV 的变化(PSRR=20logSVps/SVdi)。于是运放输出电压产生的变化:SVo=SVdi(1+Rf/Ri);Rf--反馈电阻,Ri--输入电阻。

扩展阅读:运放设计原理

我要赚赏金

我要赚赏金