上一讲当中,我们简单提到了STM32的时钟源。我们知道STM32的系统时钟的选择是可以通过对其内部的时钟管理寄存器的操作来进行选择。那么这些寄存器操作的是芯片内部的哪些电路,以及芯片内各部分外设具体的时钟频率又是如何确定的呢?带着这个问题,我们一起详细了解一下STM32的时钟树。

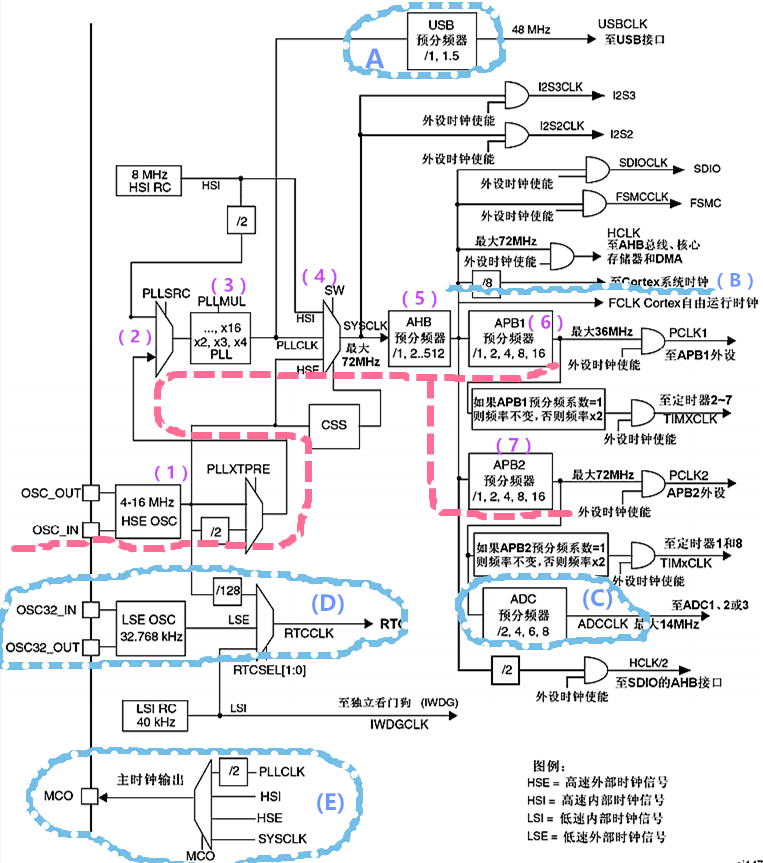

时钟树是了解STM32时钟的灵魂,STM32一切和时钟相关的操作,都要经过它进行调度。那么这个时钟树究竟是何方神圣呢?我们可以看到下图。

上图中就是STM32的时钟树了。这个图是从《STM32F10x微控制器参考手册》中截出来的,我在上面用不同颜色的笔进行了简单的标定,以便于后面的讲解。建议大家在看下文的时候,可以结合着《STM32F10x微控制器参考手册》 RCC 章节一起阅读(STM32F10x微控制器参考手册.pdf)。下面我们一起跟着图来分析一下这棵“时钟树”。

首先我们可以看到,在图中用粉色的虚线笔标定的区域,我把它叫做STM32时钟树的时钟主线。也就是说,STM32几乎所有的外围设备的时钟都由这个部分产生。

图中(1)部分是HSE 高速外部时钟信号,该信号可以在芯片外部外接有源晶振或者无源晶振提供,频率从 4-16MHZ不等。当使用有源晶振时,时钟从 OSC_IN 引脚进入, OSC_OUT 引脚悬空,当选用无源晶振时,时钟从 OSC_IN 和 OSC_OUT 进入,并且要配谐振电容。

HSE 最常使用的就是 8M 的无源晶振,因此在这里,我的开发板上也使用的是8MHz的无源晶振作为外部时钟信号的来源。当确定 PLL 时钟来源的时候, HSE 可以不分频或者 2 分频(也就是图中的/2),这个由时钟配置寄存器 CFGR 的位 17: PLLXTPRE 来设置,我们设置为 HSE不分频。 多说一句,这里的PLLXTPRE 我们可以将它理解为一个可以通过写程序来控制的“单刀双掷”开关。

从(1)中经过选择出来的时钟信号,紧接着被传递到(2)部分中。

(2)部分的名称是PLL时钟源,PLL时钟来源可以有两个,一个来自 HSE(也就是刚才从(1)部分电路中传递过来的时钟信号),另外一个是 HSI/2(也就是高速内部RC振荡器经过2分频后传递过来的信号)。具体用哪一路信号,则由时钟配置寄存器 CFGR 的位 16: PLLSRC 设置。 HSI 是内部高速的时钟信号,频率为 8M,根据温度和环境的情况频率会有漂移,在某些应用环境下可能会存在较大的误差,一般不作为 PLL 的时钟来源。这里我们选 HSE 作为PLL 的时钟来源。

(2)中的信号出来,就被送往(3)去,(3)是用来产生PLL时钟PLLCLK的电路,我们可以看到(2)中的信号在(3)中通过锁相环PLL倍频后,输出一路名为PLLCLK的时钟信号。具体要通过设置 PLL 的倍频因子,可以对 PLL 的时钟来源进行倍频,倍频因子可以是:[2,3,4,5,6,7,8,9,10,11,12,13,14,15,16],具体设置成多少,可以由时钟配置寄存器 CFGR 的位21-18位: PLLMUL[3:0]设置。我们这里设置为 9 倍频,因为上一步我们设置 PLL 的时钟来源为 HSE=8M,所以经过 PLL 倍频之后的 PLL 时钟: PLLCLK = 8M *9 = 72M。

72M是ST官方推荐的稳定运行时钟,如果你想超频的话,增大倍频因子即可,最高为 128M。在这里,我们设置 PLL 时钟: PLLCLK = 8M *9 = 72M。

在(3)中获取了PLLCLK信号后,紧接着这路信号又被传送到(4)中来。(4)是系统时钟选择电路。从图中我们可以看出,系统时钟来源可以是: HSI、 PLLCLK、 HSE,具体的时钟配置寄存器 CFGR 的位 1-0:SW[1:0]设置。我们这里设置系统时钟:SYSCLK = PLLCLK = 72M。 当然,SYSCLK信号也可选自HSI和HSE,但是这两路信号没有倍频,只有8MHz大小,速度较慢。

从(4)中出来的信号,兵分两路,一路向上走,走到了图上方的(A)处,通过USB预分频器分频,送至USB接口,用作USB设备的时钟信号;另一路继续往下走,到了(5)中。(5)是AHB总线时钟HCLK,也就是所有外围设备的时钟信号的总集了。

系统时钟 SYSCLK 经过(5)中的 AHB 预分频器分频之后得到时钟叫 APB 总线时钟,即 HCLK,分频因子可以是:[1, 2, 4, 8, 16, 64, 128, 256, 512],具体的由时钟配置寄存器 CFGR的位 7-4 :HPRE[3:0]设置。片上大部分外设的时钟都是经过 HCLK 分频得到,至于 AHB总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置,我们这里只需粗线条的设置好 APB 的时钟即可。 我们这里设置为 1 分频,即 HCLK=SYSCLK=72M。

到这里,从(5)中出来的HCLK信号就会被送往各外设中去了。这里我选择了两条较为主要的线路进行说明,一条通往(6)APB1总线时钟HCLK1,另一条通往(7) APB2总线时钟HCLK2。

我们先来看一下(6)APB1总线时钟HCLK1。

APB1 总线时钟 PCLK1 由 HCLK 经过低速 APB 预分频器得到,分频因子可以是:[1,2,4,8,16],具体的由时钟配置寄存器 CFGR 的位 10-8: PRRE1[2:0]决定。

HCLK1 属于低速的总线时钟,最高为 36M,片上低速的外设就挂载到这条总线上,比如USART2/3/4/5、SPI2/3、I2C1/2 等。至于 APB1 总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置,我们这里只需粗略的设置好 APB1 的时钟即可。我们这里设置为 2 分频,即 PCLK1 = HCLK/2 = 36M。

再来看一下(7) APB2总线时钟HCLK2。

APB2 总线时钟 PCLK2 由 HCLK 经过高速 APB2 预分频器得到,分频因子可以

是:[1,2,4,8,16],具体由时钟配置寄存器 CFGR 的位 13-11: PPRE2[2:0]决定。 HCLK2属于高速的总线时钟,片上高速的外设就挂载到这条总线上,比如全部的 GPIO、 USART1、SPI1 等。至于 APB2 总线上的外设的时钟设置为多少,得等到我们使用该外设的时候才设置,我们这里也只需粗略的设置好 APB2 的时钟即可。我们这里设置为 1 分频,即 PCLK2= HCLK = 72M。

接下来,我们通过设置系统时钟的库函数,来看一下刚才分析的这7个步骤。

上面的 7 个步骤对应的设置系统时钟库函数如下, 该函数截取自固件库文件system_stm32f10x.c。在这里我已把互联型相关的代码删掉,把英文注释翻译成了中文,并把代码标上了序号,总共七个步骤。该函数是直接操作寄存器的,有关寄存器部分请参考数据手册的 RCC 的寄存器描述部分。

代码贴出来如下:

static void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

// ① 使能 HSE,并等待 HSE 稳定

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

// 等待 HSE 启动稳定,并做超时处理

do {

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while ((HSEStatus == 0)

&&(StartUpCounter !=HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET) {

HSEStatus = (uint32_t)0x01;

} else {

HSEStatus = (uint32_t)0x00;

}

// HSE 启动成功,则继续往下处理

if (HSEStatus == (uint32_t)0x01) {

//-----------------------------------------------------------

// 使能 FLASH 预存取缓冲区 */

FLASH->ACR |= FLASH_ACR_PRFTBE;

// SYSCLK 周期与闪存访问时间的比例设置,这里统一设置成 2

// 设置成 2 的时候, SYSCLK 低于 48M 也可以工作,如果设置 成 0 或者 1 的时候,

// 如果配置的 SYSCLK 超出了范围的话,则会进入硬件错误,程序就死了

// 0: 0 < SYSCLK <= 24M // 1: 24< SYSCLK <= 48M // 2: 48< SYSCLK <= 72M */ FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

//------------------------------------------------------------

// ② 设置 AHB、 APB2、 APB1 预分频因子

// HCLK = SYSCLK

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

//PCLK2 = HCLK

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

//PCLK1 = HCLK/2

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

//③ 设置 PLL 时钟来源,设置 PLL 倍频因子, PLLCLK = HSE * 9 = 72 MHz

RCC->CFGR &= (uint32_t)((uint32_t)

~(RCC_CFGR_PLLSRC

| RCC_CFGR_PLLXTPRE

| RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE

| RCC_CFGR_PLLMULL9);

// ④ 使能 PLL

RCC->CR |= RCC_CR_PLLON;

// ⑤ 等待 PLL 稳定

while ((RCC->CR & RCC_CR_PLLRDY) == 0) {

}

// ⑥ 选择 PLL 作为系统时钟来源

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

// ⑦ 读取时钟切换状态位,确保 PLLCLK 被选为系统时钟

while ((RCC->CFGR&(uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){

}

} else {// 如果 HSE 启动失败,用户可以在这里添加错误代码出来

}

}

到此,主线部分的时钟信号产生过程就已经全部讲解完了。图中我还用蓝色笔标定了(A)~(E)部分电路。

下面对这5部分电路的时钟也进行简要的说明。

(A)USB 时钟

USB 时钟是由 PLLCLK 经过 USB 预分频器得到,分频因子可以是: [1,1.5], 具体的由时钟配置寄存器 CFGR 的位 22: USBPRE 配置。 USB 的时钟最高是 48M,根据分频因子反推过来算 , PLLCLK 只能是 48M 或者是 72M。一般我们设置 PLLCLK=72M,USBCLK=48M。 USB 对时钟要求比较高,所以 PLLCLK 只能是由 HSE倍频得到,不能使用 HSI 倍频。

(B)Cortex 系统时钟

Cortex 系统时钟由 HCLK 8 分频得到,等于 9M, Cortex 系统时钟用来驱动内核的系统定时器 SysTick, SysTick 一般用于操作系统的时钟节拍,也可以用做普通的定时。

(C)ADC 时钟

ADC 时钟由 PCLK2 经过 ADC 预分频器得到,分频因子可以是[2,4,6,8],具体的由时钟配置寄存器 CFGR 的位 15-14: ADCPRE[1:0]决定。 很奇怪的是怎么没有 1 分频。 ADC时钟最高只能是 14M,如果采样周期设置成最短的 1.5 个周期的话, ADC 的转换时间可以达到最短的 1us。如果真要达到最短的转换时间 1us 的话,那 ADC 的时钟就得是 14M,反推 PCLK2 的时钟只能是: 28M、 56M、 84M、 112M,鉴于 PCLK2 最高是 72M,所以只能取 28M 和 56M。

(D)RTC 时钟、独立看门狗时钟

RTC 时钟可由 HSE/128 分频得到,也可由低速外部时钟信号 LSE 提供,频率为

32.768KHZ,也可由低速内部时钟信号 HSI 提供,具体选用哪个时钟由备份域控制寄存器BDCR 的位 9-8: RTCSEL[1:0]配置。 独立看门狗的时钟由 LSI 提供,且只能是由 LSI 提供,LSI 是低速的内部时钟信号,频率为 30~60KHZ 直接不等,一般取 40KHZ。

(E) MCO 时钟输出

MCO 是 microcontroller clock output 的缩写,是微控制器时钟输出引脚,在 STM32 F1系列中 由 PA8 复用所得,主要作用是可以对外提供时钟,相当于一个有源晶振。 MCO 的时钟来源可以是: PLLCLK/2、 HSI、 HSE、 SYSCLK,具体选哪个由时钟配置寄存器CFGR 的位 26-24: MCO[2:0]决定。 除了对外提供时钟这个作用之外, 我们还可以通过示波器监控 MCO 引脚的时钟输出来验证我们的系统时钟配置是否正确。

至此,我们就在本节中把STM32的时钟树的主要组成部分跟大家一起分析完了,时钟树是STM32非常重要的一个环节,是使用外设,定时器,看门狗以及延时函数的基础。因此希望大家能够认真学习和了解。

尽情期待下一节:大Z带你重玩STM32系列(九)------通过按键学习STM32的GPIO口的输入

我要赚赏金

我要赚赏金