一 元器件布局的10条规则:

遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局.

布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.

元器件的排列要便于调试和维修,亦即小元件周围不能放置大元件、需调试的元、器件周围要有足够的空间。

相同结构电路部分,尽可能采用“对称式”标准布局;

按照均匀分布、重心平衡、版面美观的标准优化布局;

同类型插装元器件在X或Y方向上应朝一个方向放置。同一种类型的有极性 分立元件也要力争在X或Y方向上保持一致,便于生产和检验。

发热元件要一般应均匀分布,以利于单板和整机的散热,除温度检测元件以外的温度敏感器件应远离发热量大的元器件。

布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分。

去偶电容的布局要尽量靠近IC的电源管脚,并使之与电源和地之间形成的回路最短。

元件布局时,应适当考虑使用同一种电源的器件尽量放在一起, 以便于将来的电源分隔。

二、布线

(1)布线优先次序

键信号线优先:摸拟小信号、高速信号、时钟信号和同步信号等关键信号优先布线

密度优先原则:从单板上连接关系最复杂的器件着手布线。从单板上连线 最密集的区域开始布线

注意点:

尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。必要时应采取手工优先布线、屏蔽和加大安全间距等方法。保证信号质量。

电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。

有阻抗控制要求的网络应尽量按线长线宽要求布线。

(2)四种具体走线方式

1 、时钟的布线:

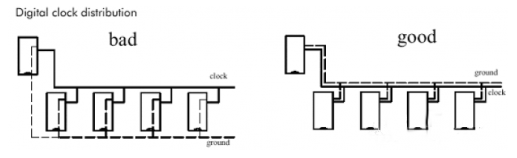

时钟线是对EMC 影响最大的因素之一。在时钟线上应少打过孔,尽量避免和其它信号线并行走线,且应远离一般信号线,避免对信号线的干扰。同时应避开板上的电源部分,以防止电源和时钟互相干扰。

如果板上有专门的时钟发生芯片,其下方不可走线,应在其下方铺铜,必要时还可以对其专门割地。对于很多芯片都有参考的晶体振荡器,这些晶振下方也不应走线,要铺铜隔离。

2、直角走线:

直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实不光是直角走线,顿角,锐角走线都可能会造成阻抗变化的情况。

直角走线的对信号的影响就是主要体现在三个方面:

拐角可以等效为传输线上的容性负载,减缓上升时间;

阻抗不连续会造成信号的反射;

直角尖端产生的EMI。

3、差分走线:

差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计.定义:通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。而承载差分信号的那一对走线就称为差分走线。

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:

抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differenTIal signaling)就是指这种小振幅差分信号技术。

对于PCB工程师来说,最关注的还是如何确保在实际走线中能完全发挥差分走线的这些优势。也许只要是接触过Layout的人都会了解差分走线的一般要求,那就是“等长、等距”。

等长是为了保证两个差分信号时刻保持相反极性,减少共模分量;等距则主要是为了保证两者差分阻抗一致,减少反射。“尽量靠近原则”有时候也是差分走线的要求之一。

4、蛇形线:

蛇形线是Layout中经常使用的一类走线方式。其主要目的就是为了调节延时,满足系统时序设计要求。设计者首先要有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用。但实际设计中,为了保证信号有足够的保持时间,或者减小同组信号之间的时间偏移,往往不得不故意进行绕线。

注意点:

成对出现的差分信号线,一般平行走线,尽量少打过孔,必须打孔时,应两线一同打孔,以做到阻抗匹配。

相同属性的一组总线,应尽量并排走线,做到尽量等长。从贴片焊盘引出的过孔尽量离焊盘远些。

我要赚赏金

我要赚赏金