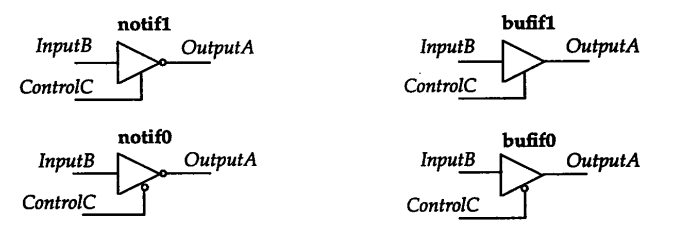

三态门(包括bufif0、bufif1、notif0及notif1)的详细阐述,并附有实例说明及真值表。

三态门概述

三态门是一种特殊的逻辑门,它包含一个输出端口、一个数据输入端口以及一个控制输入端口。其独特之处在于,根据控制输入的状态,输出端口可以被设置为高阻态(即值为z,表示高阻抗或不确定状态)。这种特性使得三态门在数字电路设计中具有广泛的应用,特别是在需要总线共享或数据隔离的场合。

Verilog 中还提供了 4 个带有控制端的 buffer 门单元,称为三态门。只有当控制信号有效时,数据才能正常传递,否则输出为高阻抗状态 Z。

三态门类型及功能

bufif0:当控制输入为1时,输出为高阻态;否则,数据输入被直接传输到输出端。

bufif1:当控制输入为0时,输出为高阻态;否则,数据输入被直接传输到输出端。

notif0:当控制输入为1时,输出为高阻态;否则,数据输入的逻辑非(即取反后的值)被传输到输出端。

notif1:当控制输入为0时,输出为高阻态(原文此处可能有误,因为通常notif1在控制输入为0时不会单纯输出z,而是应该在非控制输入为1时输出数据的非,但控制为0时行为需具体电路定义,这里按描述为z进行说明,但实际应用中可能有所不同);否则,数据输入的逻辑非被传输到输出端(但考虑到上述可能的误解,此处的描述需结合具体电路实现来理解)。

//tri bufif1 buf1 (OUTX, IN1, CTRL1) ; bufif0 buf2 (OUTY, IN1, CTRL2) ; notif1 buf3 (OUTZ, IN1, CTRL3) ; //no instantiation name notif0 (OUTX1, IN1, CTRL4) ;

实例说明

bufif1实例:

bufif1 u7bufif1(dbus, mem_data, strobe);

在此实例中,u7bufif1是bufif1类型的一个三态门实例。当strobe为0时,输出dbus被驱动至高阻态;当strobe为1时,mem_data的值被传输到dbus。

notif0实例:

notif0 u3notif0(paddr, abus, probe);

在此实例中,u3notif0是notif0类型的一个三态门实例。当probe为1时,输出paddr被驱动至高阻态;当probe为0时,abus的逻辑非被传输到paddr。

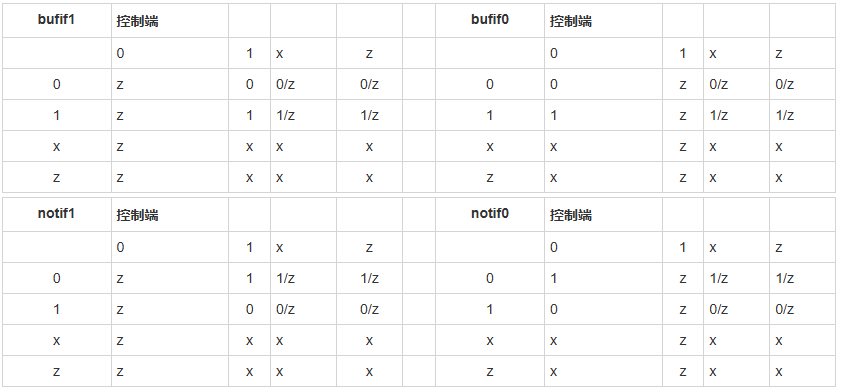

真值表

以下是根据您所提供的信息整理的三态门的真值表:

三态门的真值表如下。

表中有些为可选项,1/z 表明,根据输入端和控制端的信号强度,输出端既可能为 1,也可能为 z。

总结:

三态门是数字电路设计中一种重要的逻辑门,它包含一个输出端口、一个数据输入端口以及一个控制输入端口。

根据控制输入的状态,输出端口可以被设置为高阻态(z),这种特性使得三态门在总线共享或数据隔离等场合具有广泛应用。

Verilog中提供了四种三态门:bufif0、bufif1、notif0和notif1。其中,bufif0和bufif1用于数据缓冲,当控制输入满足特定条件时,数据输入被传输到输出端;notif0和notif1则对数据进行取反操作后再传输。

实例说明中,我们展示了bufif1和notif0的具体应用。在bufif1实例中,当控制输入strobe为0时,输出dbus被驱动至高阻态;在notif0实例中,当控制输入probe为1时,输出paddr被驱动至高阻态。

真值表详细列出了四种三态门在不同控制输入和数据输入组合下的输出状态。输出可能既可能为确定值(1或0),也可能为高阻态(z),这取决于输入端和控制端的信号强度以及具体电路的实现。

我要赚赏金

我要赚赏金