电子科技•作者:王勇;梁伟中

内河水运是国家综合运输体系和水资源综合利用的重要组成部分,是实现经济社会可持续发展的重要战略资源。航标是内河航道的基础助航设施,传统的航标管理模式落后,标准化程度低,实时性、安全性能差,已无法满足当前日益繁忙的航道运输所提出的高质量安全航行的需求。

Nios II是Altera公司推出的基于RISC技术的软核CPU,作为一种用户可随意配置和构建的32位总线嵌入式系统微处理器软核,它的硬件设计方面用户是可自定制的,具有灵活性和可裁减性等优点。

结合内河航道航标管理的实际情况,介绍了一种新的基于Nios II软核的航标监控系统的设计方案。根据系统的运行结果显示,设计实现了系统预期功能,为监控中心能实时地监测航标的工作参数与状态,管理信息,及时发现故障,从而提高航标的可靠性,增强航道航行的安全性,提高管理效率。

1、系统终端硬件电路的实现

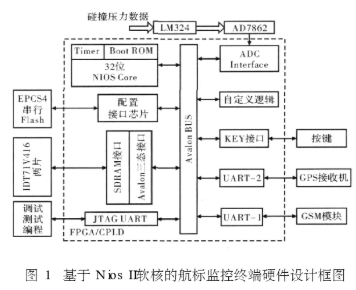

航标监控系统终端硬件设计主要包括GSM短消息发送模块、GPS数据采集模块、碰撞压力处理电路等组成的外围设备,还有以32位Nios II CORE为主体的核心逻辑两个主要部分组成,系统终端硬件框图如图1所示。

1.1 外围设备

外围设备是指某些具体控制电路或模块接口,它们都是非逻辑的,而且无法在FPGA/CPLD中用可编程逻辑来实现。

1.1.1 碰撞压力处理电路

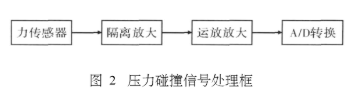

对航标是否受到碰撞须作实时监控,避免航标受碰撞损坏,而导致未能给航行体作正确指示,根据系统设计要求,碰撞压力信号测量的电路设计如图2所示。

力传感器采样数据送两级运放LM324进行调节放大后,送入双12位A/D转换器的VA1和VA2。AD7862以250 kHz的采样率同时进行4个通道信号采样,输入给片内采样一保持放大器的信号经差分并在ADC输入期间内保持,将模拟信号转换成系统需要的数字信号。

1.1.2 GSM、GPS模块

控制中心GSM Modem选用Siemens公司的无线通信引擎TC35终端,它由引擎模块、天线及其外围电路组成。监控终端TC35i模块的用户口采用40脚的ZIP插座,其中包含了模拟音频、RS232接口、SIM卡接口和电源,外围电路主要是SIM卡电路和启动控制电路。

GPS数据采集模块采用美国泰雷兹导航定位公司(Thales Navigation)的一款高性能、低功耗的小型GPS接收机B12 OEM,通过独特的软件算法和最新的GPS技术,泰勒兹公司把B12优化成快速处理、导航、车辆跟踪、移动数据、远程信息处理的手持产品。它支持差分远程操作,可提高系统差分定位精度。

1.2 片内逻辑的设计

将概念结构转化为与实际系统相应的数据模型的过程称为逻辑结构设计。FPGA的片内逻辑设计,包括系统模块和用户自定制逻辑区域。系统模块是指由SOPC builder自动生成的设计,SOPC builder会根据用户选择的IP生成相应的HDL描述文件。用户自定制逻辑区域内可以包含用户自定义的Avalon外设,以及与系统模块无关的其他用户自定制逻辑。

利用FPGA中的可编程逻辑资源和现有IP软核,如Nios II核、片内Boot ROM、用于FIFO的片内双口RAM、定时器TImer、JTAG UART等来构成该嵌入式系统处理器的接口功能模块。

1.2.1 串行通信接口UART

UART是基于RS232通信协议的串行通信接口,用于在Altera的FPGA中实现简单的RS232异步发送和接收逻辑。因为GSM、GPS模块两者的数据通信接口都为标准RS232串行接口,因此,可方便地与NiosⅡ系统的串口相连。

图1所示的监控终端硬件设计框图中,UART-1连接GSM短消息发送模块TC35i,利用AT命令控制TC35i收发信息和拨号,控制中通过RS232串口与GSM TC35 Modem通信。GSM模块接入GSM网络,按照规定的通信协议,以****方式完成航标的工作参数与状态信息的传输。

UART-2连接GPS OEM板,通过GPS定位模块的接收天线接收导航信号,经接收机解调处理,获取航标灯的位置信息,包括航标灯的代码、位置的经纬度、测定时间等信息,再将经纬度坐标通过无线通讯系统传送给监控中心。

1.2.2 自定制AD7862接口VHDL设计

Nios II是一个可灵活定制的CPU,它的外设是可选的IP软核或自定制逻辑。通过自定义编写AD7862接口的VHDL代码,编写其用户逻辑作为系统外设,部分VHDL代码如下:

对于这个控制电路设计,利用Modesim进行仿真如图3所示,通过分析该设计符合时序要求。

2 、系统终端软件设计的实现

利用SOPC Builder开发工具创建专用的处理器系统的硬件后,SOPC Builder还为编写操作这些片上硬件的软件代码提供了一个Nios II集成开发环境IDE,这个软件开发环境包括语言的头文件、外围接口的驱动以及实时操作系统的内核,可完成整个软件工程的编缉、编译、调试和下载等过程,提高了软件的开发效率。

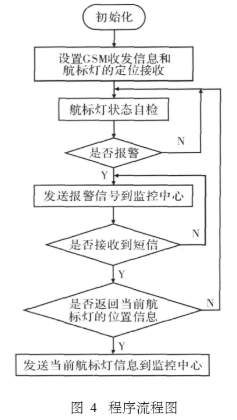

主控制程序是通过采集数据来实现自动报警、状态查询、位置显示等功能。系统进行给GSM上电复位,设置航标灯的4个坐标点区域信息;设定4个GPS工作时间间隔;航标灯其他系统参数检测是否需要重启等,程序流程如图4所示。

3、 结束语

介绍了一种基于Nios II软核处理器的内河航标监控系统的设计,与传统和限定的硬件组织和连接的控制系统方案相比,FPGA强大的逻辑控制性结合Nios II软核的灵活的功能,可方便地实现功能修改和添加;高度地集成能力,较大程度上减少产品体积以及外部信号对系统的干扰,增加了系统的可靠性、稳定性和灵活性。利用GSM和GPS进行定位数据的无线传输系统具有简单、稳定、可靠、覆盖范围广的特点,而且在成本上具有较大地优势。