芯片级验证的挑战

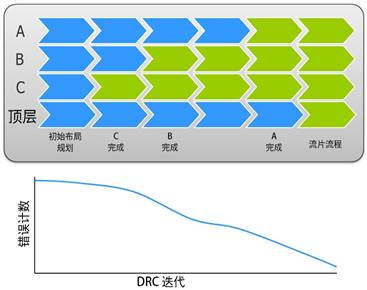

鉴于先进工艺设计的规模和复杂性,而且各方为 抢先将产品推向市场而不断竞争,片上系统 (SoC) 设计团队没有时间等到所有芯片模块都全 部完成后才开始组装芯片。因此,SoC 设计人员 通常会在模块开发的同时开始芯片集成工作,以 便在设计周期的早期捕获并纠正任何布线违规, 从而帮助缩短至关重要的上市时间。错误在早期 阶段更容易修复,而且对版图没有重大影响,设 计人员在此阶段消除错误,可以减少实现流片所 需的设计规则检查 (DRC) 迭代次数(图 1)。

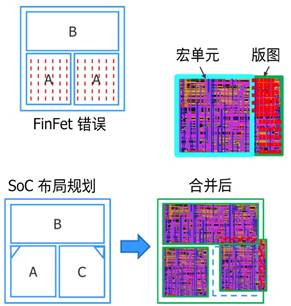

但是,早期阶段芯片级物理验证面临许多挑 战。通常,在布局规划的早期阶段,未完成模 块中报告的违规数量非常多,导致此现象的原 因是许多系统性问题可能广泛分布在整个设计中。系统性问题的典型例子包括:SoC 级别的模块布局偏离网格、SoC MACRO 封装外发生IP 合并、保留布线层上发生 IP 布线、时钟网络上的过孔类型 不正确,以及 SoC 中 IP 布局方向不匹配,如图 2 所示。在这 个阶段区分模块级违规和顶层布线违规并非易事。

图 1:识别和解决芯片集成问题与模块开发并行 进行,可最大程度地减少整个设计实现流程中 的 DRC 迭代次数。

对初始 DRC 运行使用晶圆代工厂规则集中的默认设置,通常会 导致运行时间非常长,还会报告非常多的违规,并产生极其庞 大的结果数据库,所有这些都使得调试极其困难且耗时。

图 2:系统性错误常常导致早期芯片级验 证中出现大量违规。

在此早期阶段,SoC 设计人员的目标通常是最大限度地减少每 次 DRC 迭代的运行时间,并且仅关注此时相关的违规情况。 除了将模块违规与需要调试的布线违规区分开来之外,SoC 设 计人员还可以将模块违规送回模块所有者进行调试和更正。 从早期的布局规划到最终的产品流片,SoC 设计人员的终极目 标是发现并修复 SoC 系统性问题。

改善错误较多的模块/芯片级验证

Calibre™ Reconnaissance (Calibre Recon) 工具是一个完整的功能包,支持设计团队在设计周 期的早期阶段(此时各种组件尚不成熟)便开始对整个芯片设计版图进行探索和物理验 证。Caliber Recon 工具能够非常有效地发现早期潜在的集成问题,向设计团队快速提供反 馈以便其采取适当的纠正措施,最终减少 DRC 迭代次数,缩短总周转时间,加快产品上市。 此外,Caliber Recon 工具经过精心设计,从第一次运行便能提供所有这些功能,支持在任何 工艺技术节点上按原样使用任何晶圆代工厂/独立设备制造商 (IDM) 的 Caliber sign-off 设计 套件。

自动检查选择

当存在错误时,某些规则检查往往会运行很长时 间。取消选择此类规则可以大大加快运行速度,但 设计人员如何确定取消选择哪些检查呢?取消选择涉 及许多操作的检查?还是取消选择某一类检查,例 如天线检查或所有连通性检查?选择运行 “最佳” 的一 组检查并不容易,这可能需要进行大量的高级分 析,并对晶圆代工厂规则集进行一些编辑(图 3)。

Caliber Recon 工具可自动取消选择与当前开发阶段无 关的检查。Calibre 引擎根据检查类型和检查涉及的操 作数量来决定取消选择哪些检查,以提供良好的覆盖率、加快运行时间并减少内存消耗。对于各种工艺节点,平均而言,Caliber Recon 工具可将 要执行的检查数量减少约 50%。取消选择的检查/类别会在过程记录副本中报告,以供用户 参考。Caliber Recon 工具也会接受用户手动取消选择的所有检查/类别。

图 3:选择正确的检查集合进行早期验 证需要仔细分析。

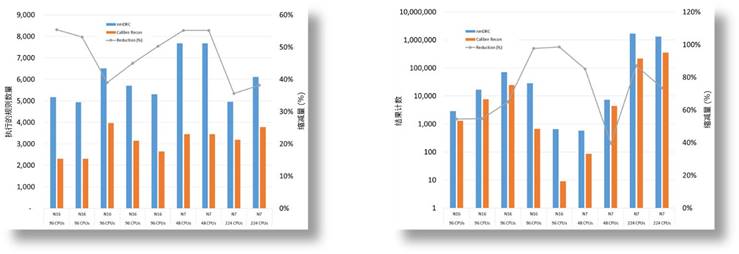

自动取消选择检查时,报告的违规总数通常会减少到原数量的 70% 左右(图 4)。但这些违 规对于目标实现阶段更有意义,有助于分析和调试实际系统性问题。

图 4:使用 Caliber Recon 功能时执行的规则检查总 数量的减少情况,以及最 终报告的违规数量的减少 情况。

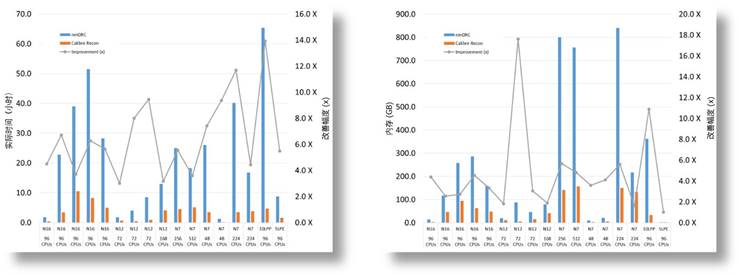

Caliber Recon 工具最多可将整体 DRC 运行时间缩短为原来的 1/14,同时仍能检查总 DRC 集合的大约 50%。Calibre 引擎自动选择的规则子集可以有效识别布局规划和子芯片集成问 题,向设计团队快速提供反馈以便采取适当的纠正措施,并显著缩短总周转时间。图 5 基于 测试显示了不同芯片的 DRC 运行时间结果。

图 5:在各种芯片上测试 Caliber Recon 自动检查选 择的结果表明,早期实 现阶段的 DRC 运行时间和 内存耗用量大幅减少。

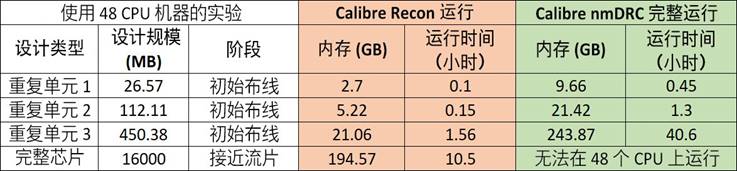

Caliber Recon 验证不仅能帮助 SoC 设计人员进行早期芯片级验证,而且支持早期模块验证。 因为模块和芯片设计是并行完成,所以模块设计人员可以在模块上运行 Caliber Recon 验证。 如果报告了错误,模块设计人员可以修复系统性问题。如果 Caliber Recon 结果无错误,便可 将模块传递给芯片,而模块设计人员可以在该模块上并行运行其余规则。如图 6 所示,在初 始布线期间对模块(重复单元)运行 Caliber Recon 工具可使运行时间缩短 8 倍,内存占用减 少 4 倍。

图 6:在不同的开发阶段 时,将针对重复单元和完 整芯片执行的 Calibre Recon 和完整 Calibre nmDRC 进 行比较,结果显示 Calibre Recon 的运行时间和内存 耗用量都减少。

灰框排除

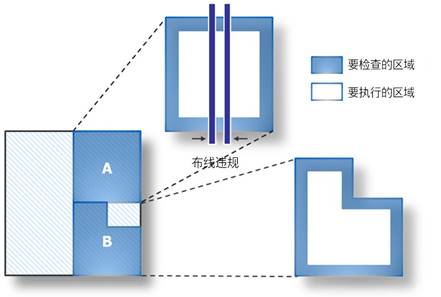

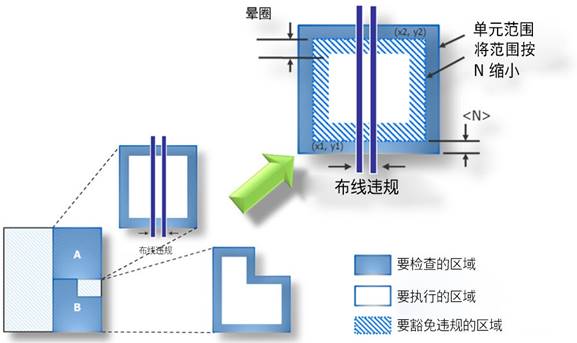

遵循相同的排除概念,但这次是从设计 角度来看,是否有可能忽略设计的某些 部分(主要是不成熟的模块),从而聚 焦于接口和布线违规并减少运行时间? Caliber Recon 灰框功能允许设计人员在 检查顶层布线时不必考虑单元细节。 灰框标记可移除指定单元中的数据,而 不会从更高的父层级中删除几何形状

(图 7)。因此,指定单元上的任何布线 违规仍能被捕捉到。此外,设计人员可 以通过缩小单元的范围来在移除的几何 形状周围保留一个晕圈,以便捕获指定 单元与其相邻单元之间的接口违规。

图 7:利用 Caliber Recon 灰框标记,设计人员可以从 DRC 中排除版图的某些部分,同时仍能检查这些区域是 否存在接口或布线违规。

灰框解决方案对于矩形和非矩形单元均适用,但设计人员可能需要指定代表非矩形单元范 围的层(边界层可用于此目的)。

虽然灰框功能可缩短运行时间,但从指定单元中移除几何形状可能会引入一些新的 DRC 违 规,这将需要额外的调试来区分哪些是实际违规,哪些是因为从指定单元中切除几何形状所 产生的违规。为了避免此问题,以及免于编辑晶圆代工厂规则集来为灰框功能增加规范说 明,设计人员可以将 Caliber Recon 灰框功能与 Caliber Auto-Waivers 功能结合使用。如图 8 所示,其主要目的是不检查不完整模块中的几何形状以缩短运行时间,附带的好处是可豁免 从指定单元排除区域时所引入的任何违规。这种结合使得设计人员可以专注于原始(有效) DRC 接口违规。所有豁免的违规都保存到豁免结果数据库文件中,供日后需要时审查。

图 8:Caliber Recon 灰框 功能与 Calibre Auto-Waiver 功能相结合,使得设计人 员可以执行接口和顶层布 线验证,而不必担心因为 从灰框单元中移除几何形 状而产生错误。

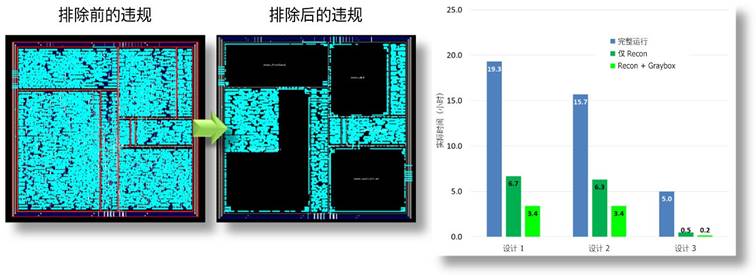

灰框解决方案能将 SoC 团队指向需要注意的接口 DRC 错误。它还将与组装相关的集成和布 线违规与不成熟模块的违规区分开来。如图 9 所示,将此功能与自动选择相关检查相结合, 可进一步缩短运行时间,因为系统会针对设计区域报告的违规,选择其中需要在特定阶段 多加注意的违规,让设计人员只专注在这些违规上。因此,它有助于设计团队在设计周期 的早期解决更多关键接口问题,避免最后一刻出现令人沮丧的意外。

图 9:Caliber Recon 自动 检查选择与灰框功能结合 使用,有助于在早期设计 实现阶段将验证重点放在 关键接口和布线问题上。

DRC ANALYZE

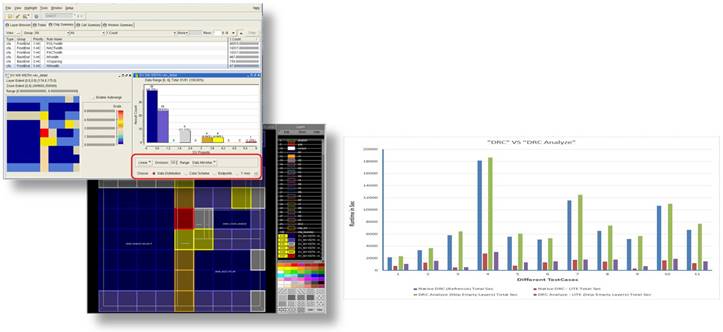

Caliber Recon DRC Analyze 功能可帮助设计人员快速分析其设计并直观地查看错误分布,以 便找出可快速提高版图质量的机会点。

DRC Analyze 功能允许设计人员绘制不同的直方图(基于层次化单元或窗口)以进行芯片分 析,并为这些直方图指定自定义缩放范围。它还支持绘制结果的彩色图,既可以在独立窗 口上绘制,也可以映射到设计上,让设计人员能够探查每个单元和每个窗口的错误细节, 结果会分布在整个设计上(图 10)。

图 10:Caliber Recon DRC Analyze 功能支持在错误 检查和调试过程中进行 快速、深入的可视化和 分析。

DRC Analyze 功能的主要优点是,设计人员可以使用晶圆代工厂规则集来执行所有必需的分 析,而无需进行任何编辑。与这种分析在芯片分析和调试期间提供的价值相比,相关开销

(运行时间平均增加 10% 和内存耗用量平均增加 20% )非常小。

……………未完待续………

我要赚赏金

我要赚赏金