今天给大侠带来Xilinx ZYNQ 动手实操演练,话不多说,上货。当我们一提到 Xilinx ZYNQ,大家脑海大多数就会浮现一个描述的词汇,高端,其实这个词很贴切的形容了Zynq系列产品,Xilinx (赛灵思公司)推出的行业第一个可扩展处理平台Zynq系列,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。

Zynq这个词很容易让人联想到zinc,也就是电池、日光屏、合金制品和药品中最常见的化学元素锌。锌与其他金属的合金可实现增强型功能,根据合金的不同对象表现为不同的色彩。锌最常见的用途就是电镀。那么这个名称与电镀之间有什么联系?

在2010年4月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台的架构详情,这款基于无处不在的ARM处理器的SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力要求。赛灵思可扩展处理平台芯片硬件的核心本质就是将通用基础双ARMCortex-A9MPCore处理器系统作为“主系统”,结合低功耗28nm工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的一致性,同时也方便日后本系列新产品的命名。

除了芯片外,赛灵思Zynq-7000系列还构成了最终平台产品的基础。赛灵思联盟计划生态系统和ARM互联社区的成员提供的软件开发与硬件设计实现工具、广泛采用的操作系统、调试器、IP及其他元素的工具就好像“电镀”在一起一样,从而使可扩展处理平台成为了可能。

Zynq-7000为何不是FPGA?

Zynq-7000可扩展处理平台是采用赛灵思新一代FPGA(Artix-7与Kintex-7FPGA)所采用的同一28nm可编程技术的最新产品系列。可编程逻辑可由用户配置,并通过“互连”模块连接在一起,这样可以提供用户自定义的任意逻辑功能,从而扩展处理系统的性能及功能。不过,与采用嵌入式处理器的FPGA不同,Zynq-7000产品系列的处理系统不仅能在开机时启动,而且还可根据需要配置可编程逻辑。采用这种方法,软件编程模式与全功能的标准ARM处理SoC毫无二致。

“可扩展”意味什么?

在软件工程领域,可扩展性(有时会同前向兼容性相混淆)是指实现方案考虑到未来发展需求的系统设计原理。这是一种能够扩展系统的系统性举措,也是实现扩展所需的工作。扩展可体现为增加新功能,也可体现为现有功能的修改。其核心主题就是在尽可能减少现有系统功能变动的基础上实现变革。

在系统架构中,可扩展性意味着系统设计时包含了通过新功能扩展/改进自身的机制和元素(hook),而且无需对系统基础架构进行较大的修改。良好的架构反映了实现上述目的的设计原理,也为今后可能的构建工作制定了发展蓝图。请注意,这通常是指最终交付的产品中包含了尚不会(实际上可能永远不会)用到的功能和机制,但这种功能并不是可有可无的,而是可维护性的必要元素,有助于避免产品过早被淘汰。

ZYNQ=processor

Zynq-7000嵌入式处理平台系列的每款产品均采用带有NEON及双精度浮点引擎的双核ARMCortex-A9MPCore处理系统,该系统通过硬连线完成了包括L1,L2缓存、存储器控制器以及常用外设在内的全面集成。该处理系统不仅能在开机时启动并运行各种独立于可编程逻辑的操作系统(OS),而且还可根据需要配置可编程逻辑。利用这种方法,软件编程模式与全功能的标准ARM处理SoC毫无二致。

应用开发人员利用可编程逻辑强大的并行处理能力,不仅可以解决多种不同信号处理应用中的大量数据处理问题,而且还能通过实施更多外设来扩展处理系统的特性。系统和可编程逻辑之间的高带宽AMBA®-AXI互联能以极低的功耗支持千兆位级数据传输,从而解决了控制、数据、I/O和存储器之间的常见性能瓶颈问题。

编程环境

Zynq-7000系列提供了一个开放式设计环境,便于可编程逻辑中双核Cortex-A9MPCore和定制加速器的并行开发,从而加速了产品上市进程。软件开发人员可以充分利用基于Eclipse的XilinxPlatformStudio软件开发套件(SDK)、ARM的DS-5和ARMRealViewDesignSuite(RVDS),或ARM互联社区和赛灵思联盟计划生态系统的领先厂商(诸如Lauterbach、WindRiver、PetaLogix、MathWorks、MentorGraphics、Micrium和MontaVista等)提供的编译器、调试器和应用。

此外,利用赛灵思屡获殊荣的ISE®设计套件的优势,Zynq-7000系列的可编程结构经定制可以最大化系统级性能,满足特定应用的各种需求。该套件提供了包括开发工具、AMB4AXI4即插即用IP核和总线功能模型(BFM)等在内的完整硬件开发环境,有助于加速设计和验证工作。赛灵思通过收购高级综合技术领先公司AutoESL进一步提升了在工具方面的进程,提供C,C++以及系统C综合优化Zynq-7000器件架构。未来的版本也将促进Zynq-7000产品系列中处理器和可编程逻辑之间关键算法的无缝衔接。

随着时间的推移,ARM互联社区和赛灵思联盟计划生态系统的第三方厂商将进一步扩展上述解决方案,这是赛灵思目标设计平台的一部分,可提供包括IP核、参考设计、开发套件及其他资源等在内的高效统一的开发环境,从而满足特定应用和设计领域要求。

可编程逻辑架构

Zynq-7000系列的可编程逻辑完全基于赛灵思最新7系列FPGA架构来设计,可确保28nm系列器件的IP核、工具和性能100%兼容。最小型的Zynq-7000、Zynq-7010和Zynq-7020均基于专门针对低成本和低功耗优化的Artix-7系列;较大型的Zynq-7030和Zynq-7040器件基于包括4至12个10.3Gbps收发器通道,可支持高速片外连接的中端Kintex-7系列。所有四款产品均采用基于2个12位1MspsADC(模数转换器)模块的新型模拟混合信号模块。

Zynq的一些概念

ZYNQ,总的来说,就是两大功能块,PS 部分和 PL部分, 直面意思理解就是ARM的SOC部分,和FPGA部分。

PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。之所以叫PL,而不是叫FPGA,原因主要是考虑到让做软件的大侠们不要望而生畏。对于逻辑而言,在这里就不多说了,单纯做软件的也不要去考虑了。

下一个层级, APU部分:

APU: 应用处理器单元(Application Processor Unit), 位于PS里面的中心位置。APU这三个字,AMD公司曾经用过,特指全称是“Accelerated Processing Units”,加速处理器,它是融聚了CPU与GPU功能的产品,电脑上两个最重要的处理器融合,相互补足,发挥最大性能。XILINX 的APU与AMD的APU在缩写上就是截然不同的两个词, 不要混淆了。

APU 这个词,在Xilinx内部的术语中,也是存在撞车的。在Xilinx 的 PowerPC体系中, 有一个辅助处理单元“Auxiliary Processing Unit” 的概念,指的是在PowerPC硬核外挂的浮点协处理器之类的单元。

在这个位置上的处理器, 还有各种其他的叫法, 有MCU (微控制器处理单元Microcontroller Unit),MPU (微处理器单元Microprocessor Unit),等等。 MCU这个叫法,暗示了处理器功能不强,只能搞搞输入输出控制啊,写个小状态机啊, 一般都是8位机。 MPU呢,就更先进了一些,成prcessor了,这意味着处理器通常是32位的, 能干点计算的事。但是有一个micro词根在里面,说明干的是小活,通常没有正式的和全尺寸的操作系统, 通常没有内存管理单元MMU。 ARM 的Cortex-M系列是干这类活的。

APU,带了Application这个词, 意味着在上面可以跑应用程序, 暗示着这个系统是需要全尺寸的操作系统的,和现在炙手可热的应用商店app store 遥相呼应。

APU里面具体包含的内容嘛,就是双ARM-CortexA9核,加上高速缓冲,DMA,定时器,中断控制,浮点和NEON协处理,硬件加速器一致性控制器ACP神马的。也就是处理器核心部分。

套用时下越来越流行的词汇,“嵌入式计算”, "embedded computing", 可以这么说,用MCU,MPU搭出来的东东,通常叫嵌入式系统。而APU搭出来的东东, 就够格叫嵌入式计算系统了。

TTC, 这个词,当年猜了半天也拿不准,看了文档,发现,是Triple Time Counter的意思。就是这个计数器里面有3个独立通道,可以独立计数。挂在APB上,为系统或外设提供定时或计数服务的。

WDT, 看门狗定时器,有两个,分别监视ARM-Cortex A9用的。如果软件跑飞,无法清定时器,一段时间后,看门狗就复位。

SWDT,系统级看门狗定时器, 这个看门狗的时钟和复位信号,都可以来自于芯片外部, 这样,即使系统有严重故障,比如时钟频率本身都有问题了,仍然可以通过与系统无关的外部信号计数,计数满就复位。

SCU, Snoop Control Unit, 用来保持双核之间的数据Cache的一致性。也就是是说,第一个A9处理器写存储时,只是写在了缓存里,没有进主存,如果第二个A9读操作,涉及到第一个写脏了的数据段, SCU要保证第二个A9的缓存里是最新的数据。 如果第二个A9写同样数据段的数据,需要在第一个中体现出写的内容。

SCU的存在,才使得两个核成互相联系的“双核”,才能成为MPsoc。在原先Xilinx的双PowerPC的芯片中, 是不存在的。不少学校的老师拿Xilinx的双powerpc练手和教学,从头搭一个Snoop协议在裸的双PowerPC中,倒也不错。

开发环境

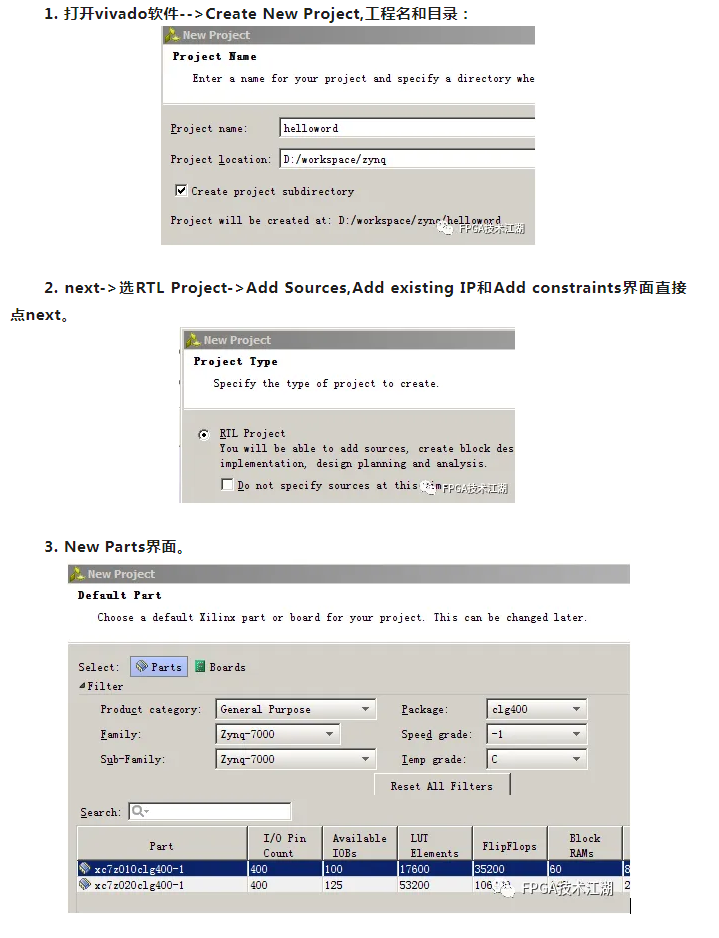

Zynq的开发环境,可以在ISE或者Vivado,不过ISE在14.7之后就停止了更新,建议安装VIVADO,毕竟Vivado号称是把各种开发工具集成并且支持图形化建模的功能强大的开发软件。

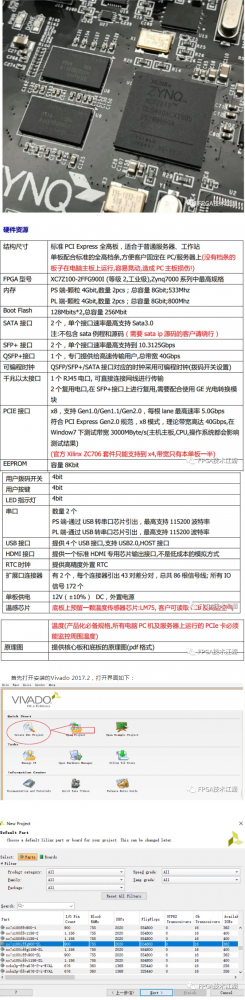

Vivado的安装教程公众号前篇推送过,各位大侠如有需要可以翻一下,这里放个超链接,Xilinx Vivado 2017.2安装教程,说了这么多,下面介绍一下开发硬件环境Zynq 7000 XC7Z100,Zynq 7000系列中顶配型号,Zynq + Kintex7最强组合,提供丰富的芯片内部资源。

实操演示

下面做一个从uart打印hello world的实验,只用PS,不用PL部分,程序从SD卡启动,跑在PS的内部RAM。

zynq 7000的PS虽然也是CPU,但是开发方法不像普通的CPU只需要一个SDK就可以了,它还需要vivado硬件设计软件。

ZYNQ 7000的PS开发需要两个工具,一个是vivado, 另一个是SDK。

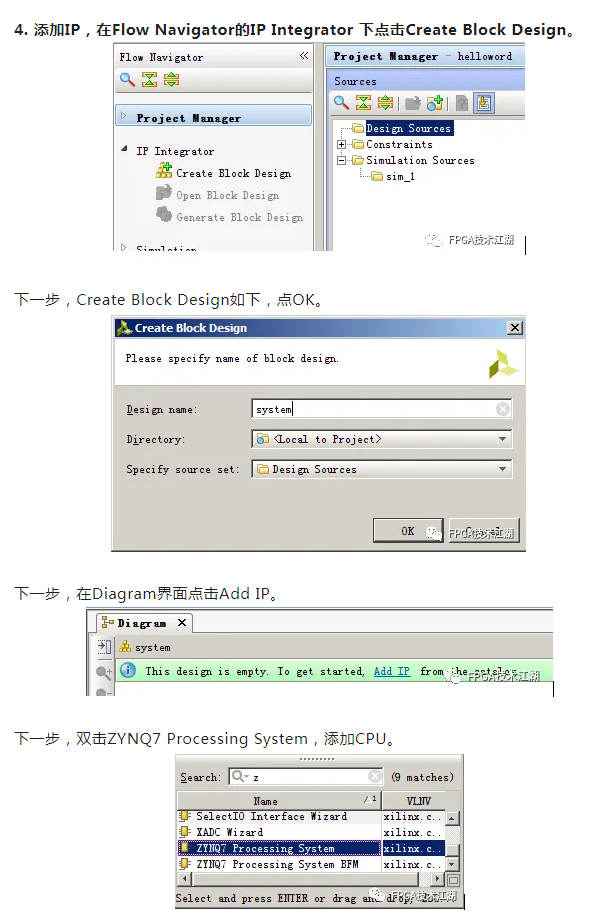

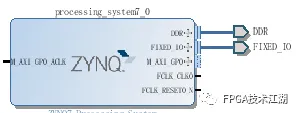

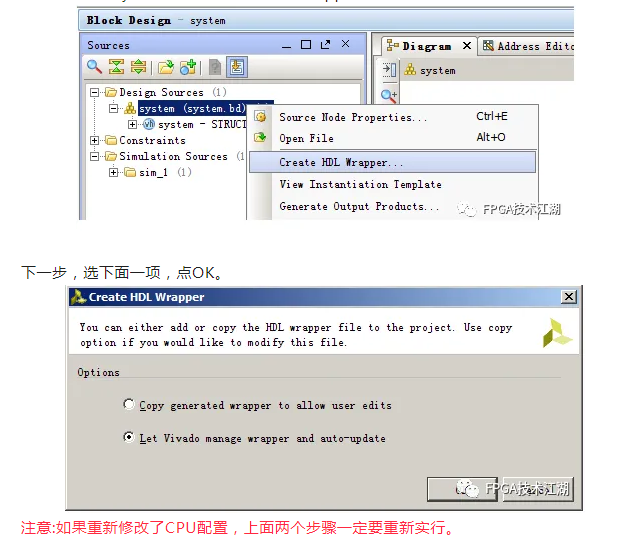

在Diagram界面点击Run Block Automation,不做修改,点Finish就可以。在Diagram界面双击。

进入设置界面,我们把所有的接口去掉,只留下FIXED_IO。

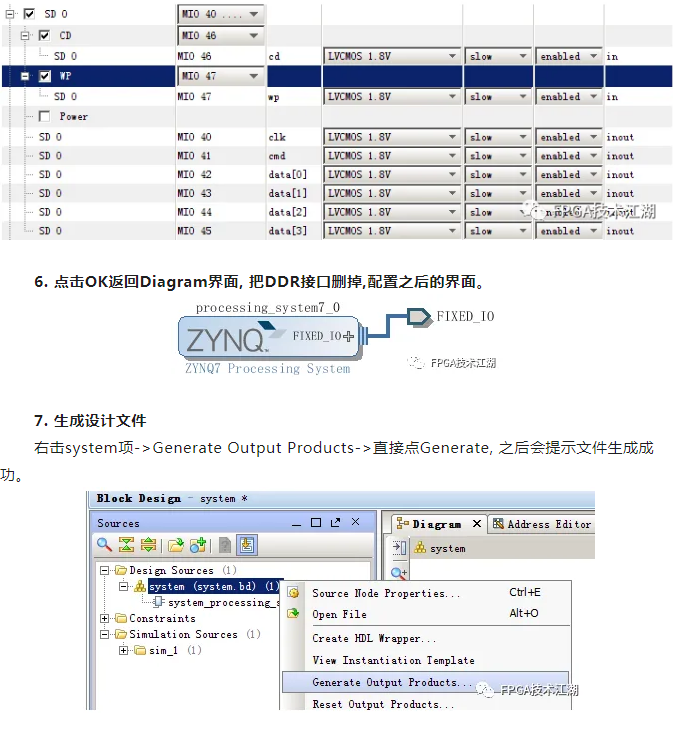

<1> PS-PL Configuration->General->Enable Clock Resets->去掉FCLK_RESET0_N

<2> PS-PL Configuration->GP Master AXI Interface->去掉 M AXI GP0 interface

<3> Clock Configuration->PL Fabric Clocks->去掉FCLK_CLK0

<4> DDR Congiguration->去掉Enable DDR

<5> 设置SD和UART引脚

MIO Configuration->Bank1 IO Voltage选LVCMOS 1.8V

MIO Configuration->IO Peripherals->选上SD 0, SD 0的引脚配置:

下一步,右击system项->Create HDL Wrapper。

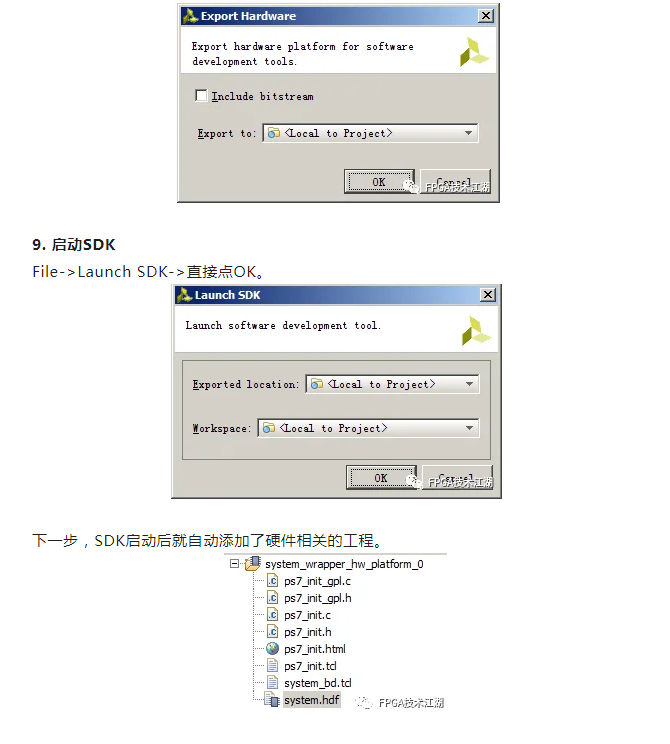

8. 导出硬件设计文件到SDK

导出前要确保Block Design是打开的,即Diagram界面要打开File->Export->Export Hardware->直接点OK,这样会把硬件文件system_wrapper.hdf导到helloword.sdk文件夹下,SDK工程也在该目录下。

system.hdf是system_wrapper.hdf文件的copy;

system.hdf是system_wrapper.hdf文件的copy;ps7_init.tcl是PS初始化的TCL脚本,PS不能执行TCL脚本,所以将该脚本转换为了C文件--ps7_init.c和ps7_init.h.;

前面用vivado的硬件设计就是为了生成这两个文件,ps7_init.c主要初始化CPU的时钟,引脚复用,ddr和外设等。后面的helloword工程只需要这两个文件,其他的文件都不需要。

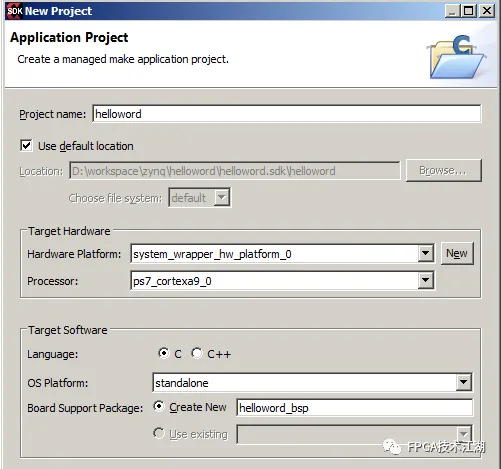

10.添加helloword工程

在SDK中->File->New->New Application Project->设置如下,点next->选hello world。

11. 修改源码

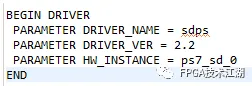

在helloword_bsp工程下打开system.mss文件,点击左下角的source,修改sd驱动版本为2.2。

修改之后重新生成BSP源码,点system.mss左下角的overview->Re-generate BSP Sources。 将ps7_init.c和ps7_init.h copy到helloword/src目录下,也可以创建连接,这里就直接copy了。

修改helloword/src/platform.c--init_platform函数,将ps7_init()函数的comment去掉, --包含头文件#include "ps7_init.h"

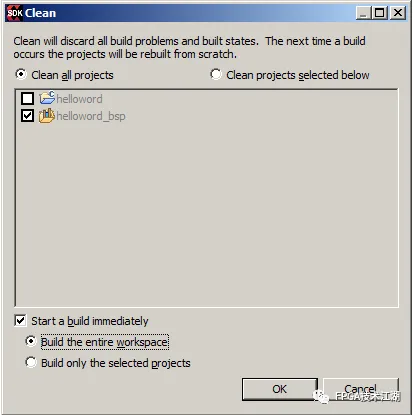

12. 编译代码->project->Clean->OK

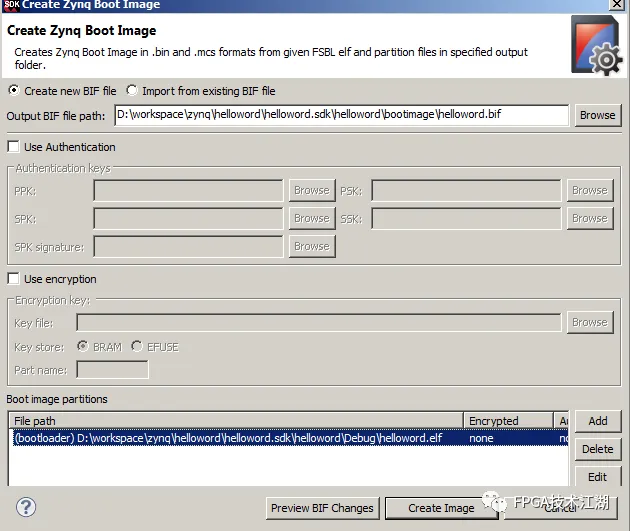

右击helloword工程->Create boot Image->Create Image。

14. 将生成的BOOT.bin文件copy到SD卡(已用HP USB Disk Storage Format Tool格式化成启动盘),启动,从串口可看到打印信息。

关于Zynq 的实操到这里就结束了,各位大侠如果想要更加深入的去研究,建议各位去Xilinx的官网下载更多的资料,自己实操动手训练,后续有时间再给各位大侠更新一些相关的内容,各位大侠如果有好的想法或者好的文章学习资料等,可以投稿,具体联系方式可以加底端群主微信,共同学习,共同进步,有缘再见。

我要赚赏金

我要赚赏金