最近在搞Nios,我自己写的avalon外设接口,为什么会驱动不了外设模块呢?我用signal tap观察avalon外设接口内相应的寄存器已经受我控制,但是引线出去到外设模块的输入端,对应的信号却没有变化。。。

请大侠帮忙看看问题究竟出在哪了?

下图是硬件连接部分:

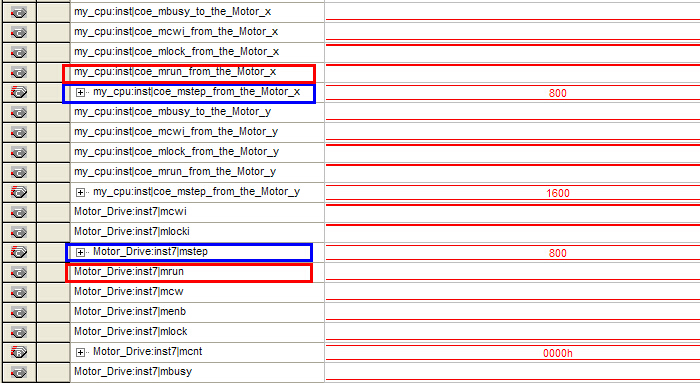

下图是signaltap采到的信号:

可以看到mrun信号在核内寄存器被置高,而经过连线到了外部模块却还是低,而令一信号mstep却跟着变了。。。

下面是我的avalon接口代码:

//==============================================================================

// Module : Motor_Drive_avalon_interface

// Editor : Acang

// Date : 2014/07/17

// Function :

// E-mail : acang301@sina.com

//==============================================================================

module Motor_Drive_avalon_interface

(

// Clcok Input

input wire csi_clk,

input wire csi_reset_n,

// Avalon-MM Slave

input wire [2:0] avs_address,

input wire avs_chipselect,

// input wire [1:0] avs_byteenable,

input wire avs_write,

input wire [31:0] avs_writedata,

input wire avs_read,

output wire [31:0] avs_readdata,

// Conduit End

output reg coe_mrun, // 电机运行开始信号

output reg coe_mcwi, // 方向输入,1:顺时针,0:逆时针

output reg coe_mlock, //

output reg [15:0] coe_mstep, // 电机运行计步:3200/r

input wire coe_mbusy // 电机忙信号

);

reg coe_mbusy_r;

//-----------------------------------------------------------------

// Write operation

//-----------------------------------------------------------------

always@(posedge csi_clk or negedge csi_reset_n) begin

if(!csi_reset_n) begin

coe_mrun <= 1'b0;

coe_mcwi <= 1'b0;

coe_mlock <= 1'b0;

coe_mstep <= 16'b0;

end

else if(avs_chipselect & avs_write) begin

case(avs_address)

0:coe_mrun <= avs_writedata[0];

1:coe_mcwi <= avs_writedata[0];

2:coe_mlock <= avs_writedata[0];

3:coe_mstep <= avs_writedata[15:0];

default: ;

endcase

end

end//always

//-----------------------------------------------------------------

// Read operation

//-----------------------------------------------------------------

reg [15:0] readdata_r;

assign avs_readdata = {16'b0,readdata_r};

//-----------------------------------------------------------------

always@(posedge csi_clk) begin

if(avs_chipselect & avs_read) begin

case(avs_address)

0:readdata_r[0] <= coe_mrun;

1:readdata_r[0] <= coe_mcwi;

2:readdata_r[0] <= coe_mlock;

3:readdata_r[15:0] <= coe_mstep;

4:readdata_r[0] <= coe_mbusy_r;

default: begin

readdata_r <= 16'b0;

end

endcase

end

else begin

readdata_r <= 16'b0;

end

end//always

//-----------------------------------------------------------------

// Signal control

//-----------------------------------------------------------------

always@(posedge csi_clk) begin

// if(coe_mbusy)

coe_mbusy_r <= coe_mbusy;

// else

// coe_mbusy_r = coe_mrun;

end//always

endmodule

//==========================================================================

// file end

//==========================================================================

我要赚赏金

我要赚赏金