刚接触Vivado不久,想掌握该软件的开发流程,于是乎就参考zedboard官网提供的zynqHW_201303_lab。

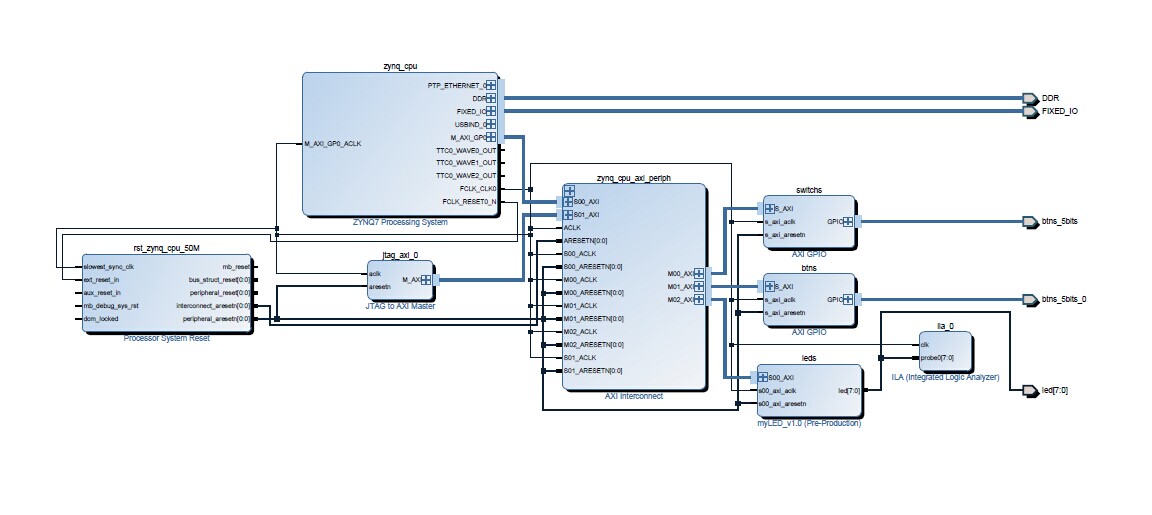

我用的vivado版本是2014.4,但是添加了ILA和JTAG TO AXI MASTER两个IP核,并连接了相应的网络,下载到板子后,系统的提示如下:

WARNING: [Xicom 50-38] xicom: No CseXsdb register file specified for CseXsdb slave type: 0, cse driver version: 0. Slave initialization skipped.

WARNING: [Xicom 50-38] xicom: No CseXsdb register file specified for CseXsdb slave type: 0, cse driver version: 0. Slave initialization skipped.

INFO: [Labtools 27-1434] Device xc7z020 (JTAG device index = 1) is programmed with a design that has no supported debug core(s) in it.

WARNING: [Labtools 27-3123] The debug hub core was not detected at User Scan Chain 1 or 3.

Resolution:

1. Make sure the clock connected to the debug hub (dbg_hub) core is a free running clock and is active OR

2. Manually launch hw_server with -e "set xsdb-user-bscan <C_USER_SCAN_CHAIN scan_chain_number>" to detect the debug hub at User Scan Chain of 2 or 4. To determine the user scan chain setting, open the implemented design and use: get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub].

WARNING: [Labtools 27-1974] Mismatch between the design programmed into the device xc7z020_1 and the probes file F:/StudyDocs/xilinx/VIVADOTEST/zynq_debug/zynq_debug.runs/impl_1/debug_nets.ltx.

The device design has 0 ILA core(s) and 0 VIO core(s). The probes file has 1 ILA core(s) and 0 VIO core(s).

Resolution:

1. Reprogram device with the correct programming file and associated probes file OR

2. Goto device properties and associate the correct probes file with the programming file already programmed in the device.

我的框图如下:

我是按照zedboard官方提供的文档走流程的,可是根本无法debug。

现在怎么弄都无法搞定,刚接触vivado,希望哪位大神可以提供解决方案,万分感谢。

我要赚赏金

我要赚赏金