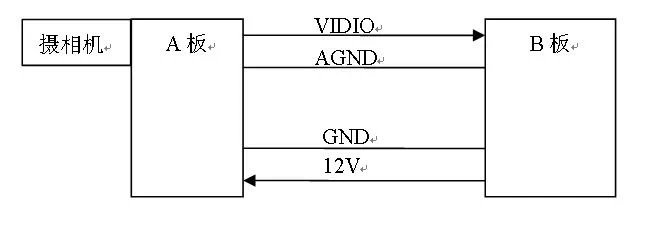

系统分为A、B两部分,A部分输出视频信号给B,再经由B板输出;B板为A板提供电源(开关电源,DC12V,纹波幅度200mV,50KHz)。

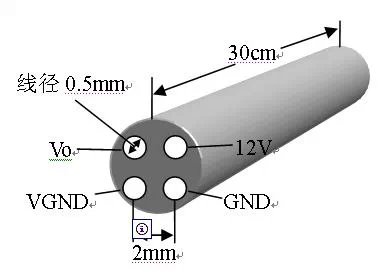

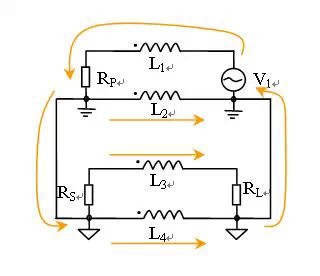

四根线捆在一起,长为30cm,为方便计算将其等效为如下四芯线模型(假设A板GND与AGND铺铜连接――即只有GND,B板GND与AGND隔离):

干扰分析:

先对线间串扰进行分析,串扰分容性串扰和感性串扰。按情景粗略估计容性串扰和感性串扰值都比较小,但这里还是通过简化模型计算来计算一下串扰值的大小,好与共路耦合干扰做一下对比。

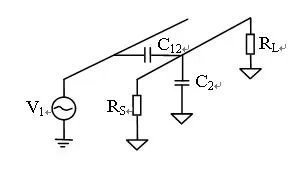

先分析一下容性串扰值(只分析12V对Vo的容性串扰值)。

简化后的模型如下:

12V电源线与Vo之间的互电容为C12;Vo线两端分别是A板源阻抗RS和B板目标阻抗RL,均为75欧;Vo对地电容为C2。聚乙稀材料相对介电常数为2.3,考虑到中间的气隙,使用1.8代替2.3。(对容性串扰,为方便画图,将干扰源画到A板侧,无影响。)

C2=1.8*0.3m*3.38/(0.14*log(4*2mm/0.5mm)) =10.8pF

C12=C2=10.8pF(近似估算)

串扰电压VSC=V1*Z2/(Z1+Z2)

Z2=|(-j/(2π*50k*10.8pF)||75||75)|=37.5

Z1=|-j/(2π*50k*10.8pF)|=294k

串扰电压值为200mV*37.5/294k=25.6uV

这样小的串扰电压不至于对1V峰峰值的视频信号造成有害干扰。(信噪比为20log(0.5V/25.6uV)=86dB,而一般摄相机输出信噪比为50dB,所以容性串扰对信号的影响可以忽略不计的。)

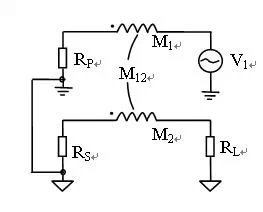

下面分析一下感性串扰:

把模型简化为两个环形线圈的互感引起的干扰,将两环路的电感分别等效到视频信号和12V上。

两个线圈之间的互感是(没有找到公式,自己大概推导一下――具体步骤就不写了^_^):

M12=μ*0.3m*ln((1.414*2mm+0.5mm/2)/(2mm-0.5mm/2))/π

=4*(10的负7次方)*π/π*ln1.759

=0.226uH

B板负载RP等效为50欧电阻并100uF电容(等效串联电阻ESR计为0.5欧)。则12V与地构成的回路中电流交流成分幅度值为:

I1=200mV/(50||(0.5-j/(50kHz*2*3.14*100uF)))=200mV/(50||(0.5-j0.03))=400mA

可见通过电容的交流电流还是比较大的,而这里对电流交流成分起决定性作用的是电容的ESR值。低ESR的电容有更好的滤波效果。

那么可以得出感性串扰电压值为:

VSL=I1*M12=400mA*0.226uH=0.09uV

呵呵,感性串扰引起的干扰比容性串扰值还要小很多,更不会引起可见的视频干扰。(注:并不是任何场合都是感性串扰小于容性串扰,而且也不一定都是很小的值,当频率升到100M左右数量级的时候这些值就会比较大了,而且那时感性串扰往往会比容性串扰更明显。)

下面就有请我们今天的主角登场吧――共路耦合干扰。

对于A板,我们可以单点接地,也可以视情况做全面铺铜而不区分GND和AGND,处理得当的话效果和单点接地接近。而对B板,我们可以选择单点连接、整板铺铜或是断开。如果单从单板设计角度来考虑,单点接地和整板铺铜都是没有问题的。但在这个系统中,B板地布的再好,只要AGND和GND连这就会导致共路干扰!唯一的选择就是GND和AGND在B板上不连接!

看一下在B板GND和AGND单点连接或铺铜连接的情况:

可以看到开关噪声从12V输出后有三条返回路径,L1=L2=L3=L4。

每根线自感按半匝线圈估算,一匝线圈电感值约为0.253uH,则每根线电感为0.13uH。对50kHz信号呈现阻抗为j2*3.14*50k*0.13uH=j40 mΩ。另外线路本身驱肤效应及导线本身电阻引进的阻抗也差不多在30-50 mΩ,也按40 mΩ算,则总的阻抗值为40*1.414=56 mΩ。不要小看这56 mΩ哈,看它给我们带来了什么?!

那么落在RL两端的50kHz信号幅度为:

VL=V1*(Z4||Z2)/(Z1+ZP+(Z4||Z2))*(RL/(RL+ Z1+RS))

=200mV*28mΩ/(560 mΩ+j60 mΩ)*(75Ω/150Ω)

=5mV

对于一个电源来说,5mV不算什么了不起,不过,对弱信号来说这已经是一个很“可观”的噪声(如果终端显视器75欧阻抗匹配电阻未拉入的话将是10mV)。信号的信噪比一下子变为20log(500mV/5mV)=40dB。另外再考虑实际有效视频信号占的幅度峰峰要小于1V(1V包含同步头),实际的信噪比还会更低一些。这样的干扰强度已经对视频信号起到影响!视频信号行频为1/64us=15625Hz,干扰源频率为50kHz,可以在监视器上看到淡淡的细纹,细纹间隔大致为6个行(间扫)。另外,只要干扰源频率不是场频的整数倍,我们就能在监视器上看到滚动的橫纹。这些都是经过我验证过的:)

引记:

通过这些相关的计算可以对容性串扰、感性串扰和共路干扰有一个更加深入的理性的认识。从定性到定量,可以让我们更好的理解这些干扰在我们设计中扮演的角色,也让我们能够更从容的处理我们的设计。如果不能过渡到量化这一阶段来,我们接触越多的东西只会变得更加迷茫,很多设计中的规则我们都知道什么样好,什么样不好,但当多条规则冲突的时候我们可能就会手足无措,如何取舍?这就需要我们对这些冲突起到的影响量化。

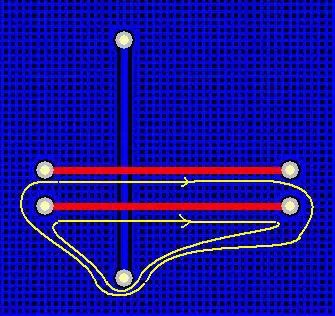

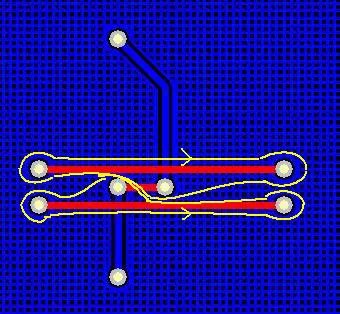

举个简单的例子,大家都说布线尽可能少走过孔,因为过孔会引入信号畸变。可是通过信号线增加过孔换层反可以增强信号回路的连续性。比如下面这个例子,三根线信号均为100M的数据线:

对左图来说看起来比较顺畅,也是大多数人比较倾向的布线方式,右图下面的信号“凭白”增加了两个过孔,貌似不太顺眼。其实左图存在着严重的回流障碍,可以看到黄线所示为两条信号回路的电流完整路径(从上方绕行的回流较远,电流小很多,忽略掉),存在共路问题。一方面是共路阻抗会引起共路干扰,另一方面两个电流环嵌套,存在比较大的互感,在100M的数据线上互感噪声是很可观的,如果竖线引起的缺口长5cm,宽3mm的话,互感噪声达到几百mV是很容易的,如果是一组数据线的话,足以使干扰达到1V以上,可能导致数据的错误或时序紊乱;而右图通过增加两个过孔则使两个电流路径分离开,没有了嵌套的电流环,共路问题也得到极大改善!

那么,在100M的数据线上增加过孔不会导致信号畸变吗?这就是上面我谈到的量化的问题。如果你对过孔做一下模型分析的话,可以发现我们通常用的过孔可以简化等效为一些电感和电容的组合,其自谐振频率在5G-10G左右,对200M以下的信号影响还是很小的,最多就是引入几十ps的沿错位和少量的信号失真,相对信号回路分割来说,影响要小得多。

大家往往对数模混合电路和高频电路有一些恐惧感,其实里面涉及到的东西也不是很复杂,主要就是模型提取及简化,再一个就是一些简单的计算。不要太迷信于别人的经验,别人也是道听途说得来的,很多是通过反复制版凑出来的经验,是理论的擦边球,并没有切中要害的。真正的从理论上深入分析才能获得更大的进步,对一个新的PCB设计也能做到一版成功。

当一天你看到板子上两根线能大概心算出其间干扰强度的时候,再做板就很容易做出取舍了:)

注:

文中计算公式以及模型的建立做了简化处理,也存在一些搞笑成分,好让大家觉得不是非常十分很枯燥呵:)不过,还是尽可能严谨的呵。另外可能按不同公司算出来会有一些差异,但应当不会相差50%,因为这里最关心的不是具体的值,因为很多原因,计算出来的值总会跟实际值有很大差异,我们最关心的是它们之间的相对关系。这点,我们的模型和计算已经足以说明问题。

水平有限,如有误还忘能通过邮件告知呵:zjd01@eyou.com

我要赚赏金

我要赚赏金