ADI专家的诚意之作,最新锁相环常见Q&A!完整文档→https://ezchina.analog.com/thread/15475

这是集ADI专家&用户在实际应用中总结所得,相关疑问的都可以在这里找答案~

问答涉及

·PLL 芯片接口相关问题;

·PLL 芯片性能相关问题;

·PLL 的调试步骤;

·为您的设计选择合适的 PLL 芯片;

......

例举三个问答,回答超级详细滴!so 全文是一定不能错过滴~ 完整文档→https://ezchina.analog.com/thread/15475

Q:请详细解释一下控制时序,电平及要求

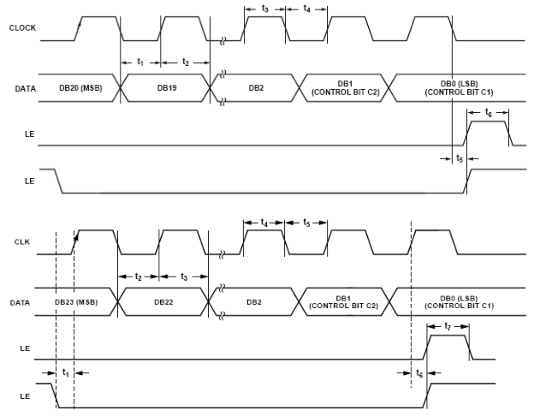

A:ADI 的所有锁相环产品控制接口均为三线串行控制接口。如图 所示。要注意的是:在 ADI 的PLL 产品中,大多数的时序图如图中上面的图所示,该图是错误的,正确的时序图如图中下面的图所示,LE 的上升沿应跟 Clock 的上升沿对齐,而非 Clock 的下降沿。

PLL 频率合成器的串行控制接口(3 Wire Serial Interface)

控制接口由时钟 CLOCK,数据 DATA,加载使能 LE 构成。加载使能 LE 的下降沿提供起始串

行数据的同步。串行数据先移位到 PLL 频率合成器的移位寄存器中,然后在 LE 的上升沿更新

内部相应寄存器。注意到时序图中有两种 LE 的控制方法。

控制接口由时钟 CLOCK,数据 DATA,加载使能 LE 构成。加载使能 LE 的下降沿提供起始串

行数据的同步。串行数据先移位到 PLL 频率合成器的移位寄存器中,然后在 LE 的上升沿更新

内部相应寄存器。注意到时序图中有两种 LE 的控制方法。

SPI 控制接口为 3V/3.3V CMOS 电平。

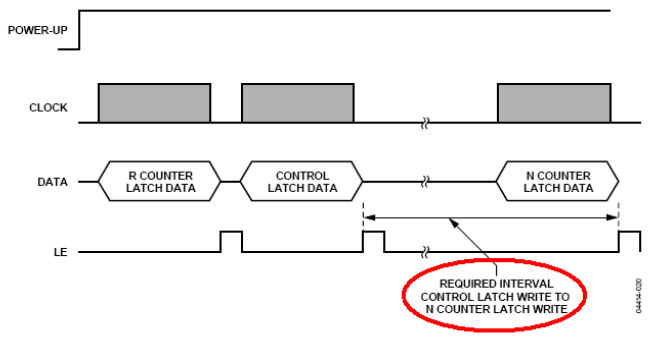

另外,需要注意的是对 PLL 芯片的寄存器进行写操作时,需要按照一定的次序来写,具体请参

照芯片资料中的描述。特别地,在对 ADF4360 的寄存器进行操作时,注意在写控制寄存器和 N

计数器间要有一定的延时。

控制信号的产生,可以用 MCU,DSP,或者 FPGA。产生的时钟和数据一定要干净,过冲小。

当用 FPGA 产生时,要避免竞争和冒险现象,防止产生毛刺。如果毛刺无法避免,可以在数据

线和时钟线上并联一个 10~47pF 的电容,来吸收这些毛刺。

Q:PLL 对于 VCO 有什么要求? 如何设计 VCO 输出功率分配器?

A:选择 VCO 时,尽量选择 VCO 的输出频率对应的控制电压在可用调谐电压范围的中点。

选用低控制电压的 VCO 可以简化 PLL 设计。

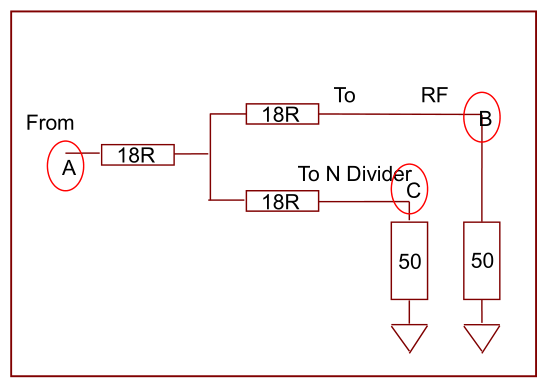

VCO 的输出通过一个简单的电阻分配网络来完成功率分配。从 VCO 的输出看到电阻网络的阻

抗为 18+(18+50)//(18+50)=52ohm。形成与 VCO 的输出阻抗匹配。下图中 ABC 三点功率关系。B,C 点的功率比 A 点小 6dB。

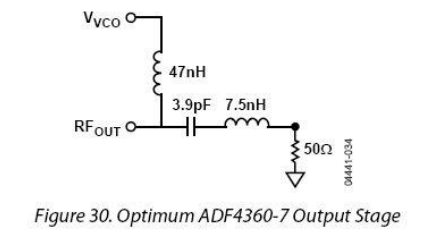

如图是 ADF4360-7 输出频率在 850MHz~950MHz 时的输出匹配电路,注意该例是匹配到 50 欧

的负载。如果负载是 75 欧,那么匹配电路无需改动,ADF4360-7 的输出级为电流源,负载值的小变动不会造成很大的影响,但要注意差分输出端的负载需相等。

ADF4360-7 输出匹配电路

Q:使用 ADF4158 进行锯齿波扫频工作,但输出只有点频,并不扫频,请问可能是什么原因?

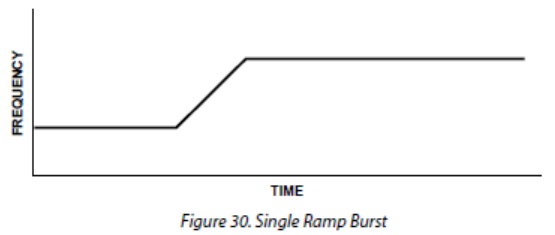

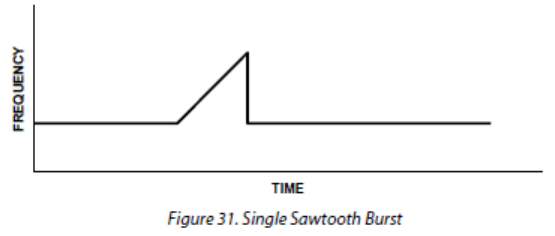

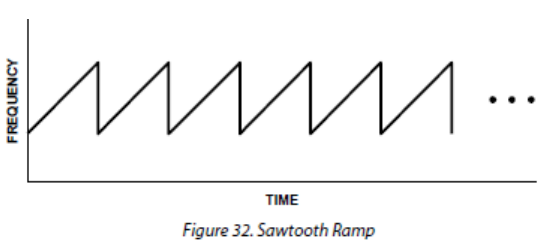

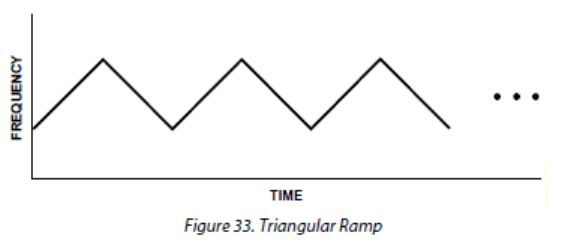

A:可能是以下一些问题造成的输出为点频,而不是扫频。首先请注意 Register0 的 DB31 设置,置1 为 Ramp ON。还有就是 Register3 的【DB11:DB10】,这两个比特是 Ramp 模式的选择。Ramp 共有 4 种基本模式。分别是 Single Ramp Burst,Single Sawtooth Burst,SawtoothRamp 和 Triangular Ramp 模式。

如果选成 Single Ramp Burst 模式的话,在频谱上只有一次变化从 f1 到 f2,在频谱仪可能会看到固定在 f2 上的频率;如果选成 Single Sawtooth Burst 模式的话,在频谱上 f1 变化到 f2,再回到f1,在频谱仪可能会看到固定于 f1 上的频率。

我要赚赏金

我要赚赏金